一理論基礎

當兩個電路彼此靠近時,由于電路之間的電容性(電場)和電感性(磁場)耦合,在一個電路中傳播的信號會在另一電路中感應出信號。這種現(xiàn)象稱為串擾。基礎模型如圖1所示。

圖1 微帶線PCB示意圖

兩條微帶線彼此之間距離為s,與接地層(信號返回平面)之間的距離為d。第一條走線(發(fā)射端)連接幅值為VS,內阻為RS的可變電壓源,并端接阻值為RL的負載電阻。第二條走線(接收端),近端和遠端分別接阻值為RNE和RFE的負載電阻。圖2所示為對上述電路布置的建模。

圖2 微帶線PCB電路模型

發(fā)射端線路上的交變電流IG產生磁場,該磁場引起的磁通量穿透在兩導體的環(huán)路之間,從而在接收電路中感應出電壓。我們通過互感LGR對此建模,如圖3所示。

圖3 電感耦合電路模型

類似地,發(fā)射端線路的交變電壓VG在接收端線路上產生電場),從而在接收器電路中感應出電流。我們通過互容CGR對此建模,如圖4所示。

圖4 電容耦合電路模型

兩種耦合機制的疊加可用如圖5所示電路等效。

圖5 接收器電路模型

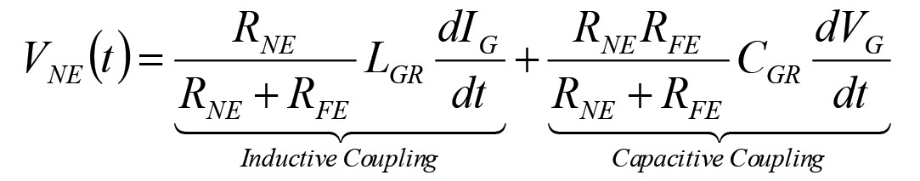

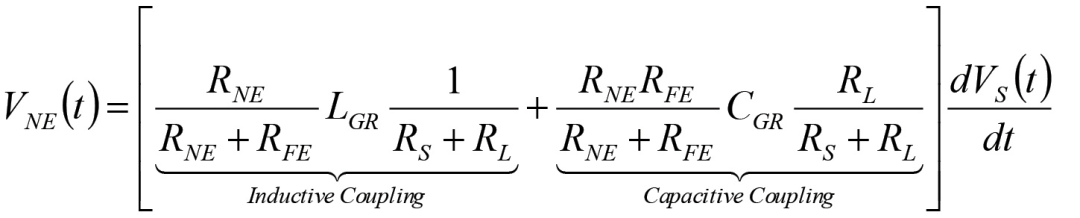

通過疊加,近端和遠端電壓由下式給出:

(1a)

(1b)

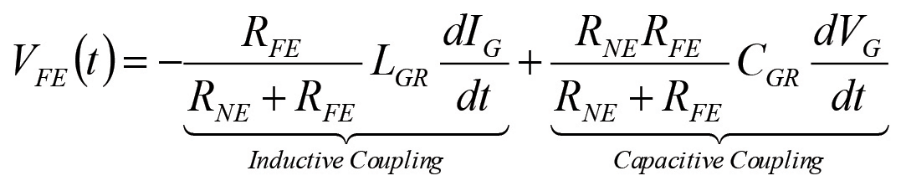

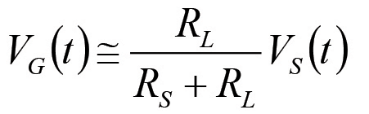

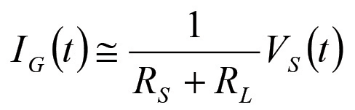

在假設線路在VS(t)的最高有效頻率分量上短路的情況下,發(fā)射端線路上的電壓和電流基本恒定。從而得出,

(2a)

(2b)

因此,

(3a)

(3b)

因此從上述公式我們可知,為了最小化串擾,我們可以減少:1)源信號Vs的變化,2)電感耦合LGR,或3)電容耦合CGR。

二驗證結果

為了驗證上述結論,我們做了如下實驗,實驗布置如圖6所示。

圖6 實驗布置

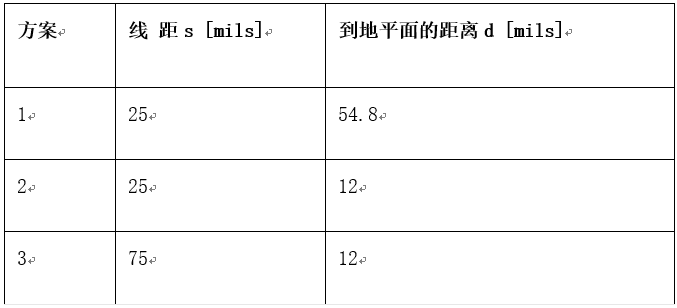

圖7為具有不同電路拓撲的PCB。

圖7 具有不同電路拓撲的PCB

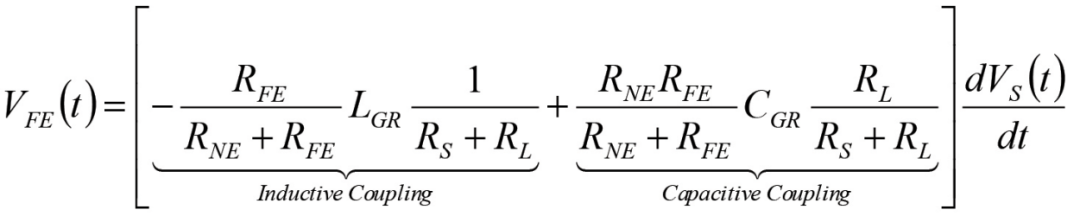

研究三種不同的電路拓撲,如表1所描述。

表1 電路拓撲

圖8至圖10顯示了發(fā)射端(干擾源)信號,以及在接收端(敏感源)信號線上感應到的近端和遠端電壓。

該信號源的開路電壓為1Vpp,1 MHz梯形脈沖信號,其上升時間為100 ns,下降時間為200 ns,占空比為50%。我們在方案1中進行以下觀察,如圖8所示。

圖8 串擾感應電壓-方案1

對于近端感應電壓,由于上升時間是下降時間的兩倍,根據公式3a,感應電壓的大小應相差兩倍,實測與理論相符。我們還注意到,這兩個電壓的極性相反,這也可從公式3a得出。對于遠端感應電壓可以進行類似的觀察。此外,由于近端電壓的耦合系數(參考公式3a)為正,因此在上升期間的感應電壓也為正。遠端電壓在上升時間內為負,表明電感性耦合相對于容性耦合為主要耦合方式(參見公式3b)。

方案2:使接地層靠近線路,同時保持線路之間的距離不變,主要減少了電感耦合并導致了感應電壓幅值的減小,實測如圖9所示。

圖9 串擾感應電壓-情況2

方案3描述了與方案2到地平面的距離不變的情況,但是線之間的距離增加了。如圖10所示,這主要減少了電容耦合,并進一步降低了感應電壓。

圖10 串擾感應電壓-情況3

串擾不僅影響信號完整性,同時增加電磁兼容風險,因此在PCB設計過程中要時刻注意關鍵信號走線方式,避免額外的噪聲串擾。

責任編輯:lq

-

電路

+關注

關注

172文章

5851瀏覽量

171915 -

pcb

+關注

關注

4317文章

23010瀏覽量

396339 -

串擾

+關注

關注

4文章

189瀏覽量

26932

原文標題:如何有效減少PCB走線之間的串擾

文章出處:【微信號:TLTECH,微信公眾號:韜略科技EMC】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

博眼球還是真本事?參考平面不完整信號串擾反而好

pcb走線厚度:打造更穩(wěn)定、精準的PCB設計

PCB產生串擾的原因及解決方法

如何使用SigXplorer進行串擾的仿真

怎么樣抑制PCB設計中的串擾

如何有效減少PCB走線之間的串擾

如何有效減少PCB走線之間的串擾

評論