門電平模型化

本章講述Verilog HDL為門級電路建模的能力,包括可以使用的內置基本門和如何使用它們來進行硬件描述。

5.1 內置基本門

Verilog HDL中提供下列內置基本門:

1) 多輸入門:

and, nand,or, nor, x o r, x n o r

2) 多輸出門:

buf, not

3) 三態門:

bufif0, bufif1, notif0,notif1

4) 上拉、下拉電阻:

pullup, pulldown

5) MOS開關:

cmos, nmos, pmos, rcmos, rnmos, rpmos

6) 雙向開關:

tran,tranif0, tranif1, rtran, rtranif0, rt r a n i f 1

門級邏輯設計描述中可使用具體的門實例語句。下面是簡單的門實例語句的格式。

g a t e _ t y p e[i n s t a n c e _ n a m e] (term1, term2, . . . ,termN ) ;

注意,i n s t a n c e _ n a m e是可選的;g a t e _ t y p e為前面列出的某種門類型。各 term用于表示與門的輸入/輸出端口相連的線網或寄存器。

同一門類型的多個實例能夠在一個結構形式中定義。語法如下 :

g a t e _ t y p e

[i n s t a n c e _ n a m e 1] (term11, term12, . . .,term1N ) ,

[i n s t a n c e _ n a m e 2] (term21, term22, . . .,term2N ) ,

. . .

[i n s t a n c e _ n a m e M] (termM1, termM2, . . .,termMN ) ;

5.2 多輸入門

內置的多輸入門如下:

and nand nor or xor xnor

這些邏輯門只有單個輸出, 1個或多個輸入。多輸入門實例語句的語法如下:

m u l t i p l e _ i n p u t _ g a t e _ t y p e

[i n s t a n c e _ n a m e] (OutputA, Input1, Input2, . . .,InputN ) ;

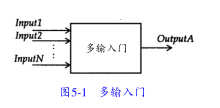

第一個端口是輸出,其它端口是輸入。如圖5 - 1所示。

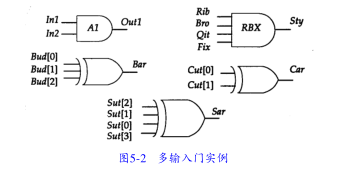

下面是幾個具體實例。圖5 - 2為對應的邏輯圖。

and A 1(Out1, In1, In2 ) ;

a n d R B X (Sty, Rib, Bro, Qit, Fix ) ;

x o r (Bar, Bud[ 0 ] ,B u d[1], B u d[ 2 ] ) ,

(Car, Cut[0], C u t[ 1 ] ) ,

(Sar, Sut[2], S u t[1], S u t[0], S u t[ 3 ] ) ;

第一個門實例語句是單元名為 A 1、輸出為O u t 1、并帶有兩個輸入I n 1和I n 2的兩輸入與門。第二個門實例語句是四輸入與門,單元名為 R B X,輸出為S t y,4個輸入為R i b、B ro、Q i t和F i x。第三個門實例語句是異或門的具體實例,沒有單元名。它的輸出是 B a r,三個輸入分別為B u d[ 0 ]、B u d[ 1 ]和B u d[ 2 ]。同時,這一個實例語句中還有兩個相同類型的單元。下面是這些門的真值表。注意在輸入端的 z與對x的處理方式相同;多輸入門的輸出決不能是z。

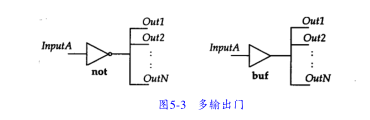

5.3 多輸出門

多輸出門有:

buf not

這些門都只有單個輸入,一個或多個輸出。如圖 5 - 3所示。這些門的實例語句的基本語法如下:

m u l t i p l e _ o u t p u t _ g a t e _ t y p e

[i n s t a n c e _ n a m e] (Out1, Out2, . . . OutN ,InputA ) ;

最后的端口是輸入端口,其余的所有端口為輸出端口。

例如:

b u f B 1 (Fan [ 0 ],Fan [ 1 ],Fan [ 2 ],Fan [ 3 ],C l k);

n o t N 1 (P h A,P h B,R e a d y);

在第一個門實例語句中,C l k是緩沖門的輸入。門B 1有4個輸出:F a n[ 0 ]到F a n[ 3 ]。在第二個門實例語句中,R e a d y是非門的唯一輸入端口。門N 1有兩個輸出:P h A和P h B。這些門的真值表如下:

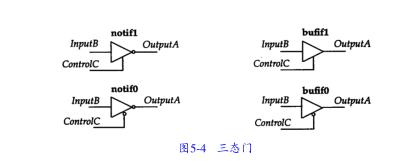

5.4 三態門

三態門有:

bufif0 bufif1 notif0 notif1

這些門用于對三態驅動器建模。這些門有一個輸出、一個數據輸入和一個控制輸入。三態門實例語句的基本語法如下:

t r i s t a t e _ g a t e[i n s t a n c e _ n a m e] (OutputA, InputB,ControlC ) ;

第一個端口O u t p u t A是輸出端口,第二個端口 I n p u t B是數據輸入, C o n t ro l C是控制輸入。參見圖5 - 4。根據控制輸入,輸出可被驅動到高阻狀態,即值 z。對于b u f i f 0,若通過控制輸入為1,則輸出為z;否則數據被傳輸至輸出端。對于 b u f i f 1,若控制輸入為0,則輸出為z。對于n o t i f 0,如果控制輸出為 1,那么輸出為 z;否則輸入數據值的非傳輸到輸出端。對于 n o t i f 1,若控制輸入為0;則輸出為z。

例如:

bufif1BF1 (D b u s,M e m D a t a,S t r o b e);

n o t i f 0 N T 2 (Addr, Abus, Probe ) ;

當Strobe為0時,bufif1門B F 1驅動輸出D b u s為高阻;否則Mem Data被傳輸至D b us。在第2個實例語句中,當P ro b e為1時,A d d r為高阻;否則Abus的非傳輸到Addr。

下面是這些門的真值表。表中的某些項是可選項。例如, 0 /z表明輸出根據數據的信號強度和控制值既可以為0也可以為z。

5.5 上拉、下拉電阻

上拉、下拉電阻有:

pullup pulldown

這類門設備沒有輸入只有輸出。上拉電阻將輸出置為 1。下拉電阻將輸出置為 0。門實例語句形式如下:

pull _ gate[i n s t a n c e _ n a m e] (out putA) ;

門實例的端口表只包含1個輸出。例如:

pullupPUP (P w r) ;

此上拉電阻實例名為P U P,輸出P w r置為高電平1。

5.6 MOS開關

M O S開關有:

cmos pmos nmos rcmos rpmos rnmos

這類門用來為單向開關建模。即數據從輸入流向輸出,并且可以通過設置合適的控制輸入關閉數據流。

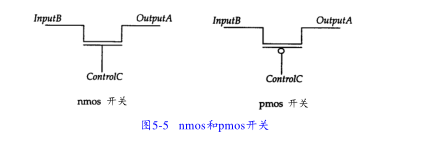

pmos ( p類型M O S管)、nmos( n類型M O S管),rnmos( r代表電阻)和r p m o s開關有一個輸出、一個輸入和一個控制輸入。實例的基本語法如下:

g a t e _ t y p e[i n s t a n c e _ n a m e] (OutputA, InputB, ControlC ) ;

第一個端口為輸出,第二個端口是輸入,第三個端口是控制輸入端。如果 n m o s和r n m o s開關的控制輸入為0,p m o s和r p m o s開關的控制為1,那么開關關閉,即輸出為 z;如果控制是1,輸入數據傳輸至輸出;如圖 5 - 5所示。與n m o s和p m o s相比,r n m o s和r p m o s在輸入引線和輸出引線之間存在高阻抗(電阻)。因此當數據從輸入傳輸至輸出時,對于 r p m o s和r m o s,存在數據信號強度衰減。

例如:

pmos P 1 (BigBus, SmallBus, GateControl ) ;

rnmos R N 1 (ControlBit, ReadyBit, Hold ) ;

第一個實例為一個實例名為 P 1 的p m o s開關。開關的輸入為smallbus輸出為bigbus,控制信號為Gate Control。

這些開關的真值表如下所示。表中的某些項是可選項。例如, 1 /z表明,根據輸入和控制信號的強度,輸出既可以為1,也可以為z。

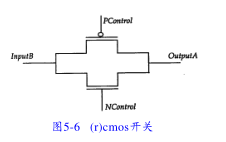

c m o s ( m o s求補)和r c m o s ( c m o s的高阻態版本)開關有一個數據輸出,一個數據輸入和兩個控制輸入。這兩個開關實例語句的語法形式如下:

(r)cmos [i n s t a n c e _ n a m e]

(OutputA, InputB, NControl, PControl);

第一個端口為輸出端口,第二個端口為輸入端口,第三個端口為n通道控制輸入,第四個端口為是 P通道控制輸入。c m o s ( r c m o s )開關行為與帶有公共輸入、輸出的 p m o s

(r p m o s)和n m o s ( r n m o s )開關組合十分相似。參見圖5 - 6。

5.7 雙向開關

雙向開關有:

tran rtran tranif0 rtranif0 tranif1 rtranif1

這些開關是雙向的,即數據可以雙向流動,并且當數據在開關中傳播時沒有延時。后 4個開關能夠通過設置合適的控制信號來關閉。t r a n和r t r a n開關不能被關閉。

t r a n或r t r a n ( t r a n 的高阻態版本)開關實例語句的語法如下:

( r ) t r a n [i n s t a n c e _ n a m e] (SignalA, SignalB) ;

端口表只有兩個端口,并且無條件地雙向流動,即從 S i g n a l A向S i g n a l B,反之亦然。其它雙向開關的實例語句的語法如下:

g a t e _ t y p e[i n s t a n c e _ n a m e] (SignalA, SignalB, ControlC ) ;

前兩個端口是雙向端口,即數據從 S i g n a l A流向S i g n a l B,反之亦然。第三個端口是控制信號。如果對 t r a n i f 0和t r a n i f 0,controlC是1;對t r a n i f 1和r t r a n i f 1,contorlC是0;那么禁止雙向數據流動。對于 r t r a n、r t r a n i f 0和r t r a n i f 1,當信號通過開關傳輸時,信號強度減弱。

5.8 門時延

可以使用門時延定義門從任何輸入到其輸出的信號傳輸時延。門時延可以在門自身實例語句中定義。帶有時延定義的門實例語句的語法如下:

gate_type [d e l a y] [i n s t a n c e _ n a m e] (t e r m i n a l _ l i s t) ;

時延規定了門時延,即從門的任意輸入到輸出的傳輸時延。當沒有強調門時延時,缺省的時延值為0。

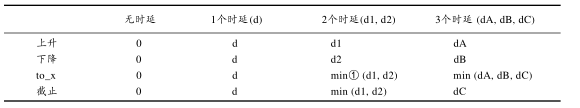

門時延由三類時延值組成:

1) 上升時延

2) 下降時延

3) 截止時延

門時延定義可以包含 0個、1個、2個或3個時延值。下表為不同個數時延值說明條件下,各種具體的時延取值情形。

注意轉換到x的時延( t o _ x )不但被顯式地定義,還可以通過其它定義的值決定。下面是一些具體實例。注意 Verilog HDL模型中的所有時延都以單位時間表示。單位時間與實際時間的關聯可以通過` t i m e s c a l e編譯器指令實現。在下面的實例中 ,

n o t N 1 (Qbar, Q) ;

因為沒有定義時延,門時延為0。下面的門實例中,

n a n d #6 (Out, In1, In2) ;

所有時延均為6,即上升時延和下降時延都是 6。因為輸出決不會是高阻態,截止時延不適用于與非門。轉換到x的時延也是6。

a n d #(3,5) (Out, In1, In2, In3 ) ;

在這個實例中,上升時延被定義為 3,下降時延為5,轉換到x的時延是3和5中間的最小值,即3。在下面的實例中,

n o t i f 1 #(2,8,6) (Dout, Din1, Din2 ) ;

上升時延為2,下降時延為8,截止時延為6,轉換到x的時延是2、8和6中的最小值,即2。對多輸入門(例如與門和非門)和多輸出門 (緩沖門和非門 )總共只能夠定義 2個時延(因為輸出決不會是 z)。三態門共有 3個時延,并且上拉、下拉電阻實例門不能有任何時延。

minmax時延形式

門延遲也可采用m i n : t y p : m a x形式定義。形式如下:

最小值、典型值和最大值必須是常數表達式。下面是在實例中使用這種形式的實例。

n a n d #(24, 57) ( Pout, Pin1, Pin2 ) ;

選擇使用哪種時延通常作為模擬運行中的一個選項。例如,如果執行最大時延模擬,與

非門單元使用上升時延4和下降時延7。程序塊也能夠定義門時延。

5.9 實例數組

當需要重復性的實例時,在實例描述語句中能夠有選擇地定義范圍說明 (范圍說明也能夠在模塊實例語句中使用)。這種情況的門描述語句的語法如下:

g a t e _ t y p e [d e l a y]instance_name [l e f t b o u n d : r i g h t b o u n d]

(l i s t _ o f _ t e r m i n a l _ n a m e s) ;

l e f t b o u n d和r i g h t b o u n d值是任意的兩個常量表達式。左界不必大于右界,并且左、右界兩者都不必限定為0。示例如下。

w i r e [3:0] Out, InA, InB ;

. . .

n a n d G a n g [3:0] (Out, InA, InB ) ;

帶有范圍說明的實例語句與下述語句等價:

n a n d

Gang3 (O u t[3], I n A[3], I n B[ 3 ] ) ,

G a n g 2 (O u t[2], I n A[2], I n B[ 2 ] ) ,

G a n g 1 (O u t[ 1 ] , I n A[1], I n B[ 1 ] ) ,

Gang0 (O u t[0], I n A[ 0 ] , I n B[ 0 ] ) ;

注意定義實例數組時,實例名稱是不可選的。

5.10 隱式線網

如果在Verilog HDL模型中一個線網沒有被特別說明,那么它被缺省聲明為 1位線網。但是` d e f a u l t _ n e t t y p e編譯指令能夠用于取代缺省線網類型。編譯指令格式如下:

` d e f a u l t _ n e t t y p e n e t _ t y p e

例如:

`default_nettype wand

根據此編譯指令,所有后續未說明的線網都是 w a n d類型。

` d e f a u l t _ n e t t y p e編譯指令在模塊定義外出現,并且在下一個相同編譯指令或 ` re s e t a l l編譯指令出現前一直有效。

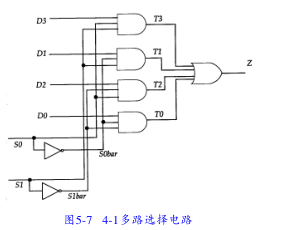

5.11 簡單示例

下面是圖5 - 7中4 - 1多路選擇電路的門級描述。注意因為實例名是可選的 (除用于實例數組

情況外),在門實例語句中沒有指定實例名。

如果或門實例由下列的實例代替呢 ?

o r Z (Z , T 0 , T 1 , T 2 , T 3); //非法的Verilog HDL表達式。注意實例名還是Z,并且連接到實例輸出的線網也是 Z。這種情況在Verilog HDL中是不允許的。在同一模塊中,實例名不能與線網名相同。

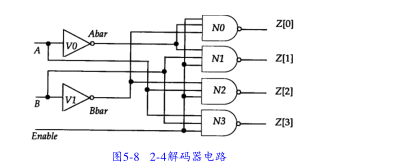

5.12 2-4解碼器舉例

圖5 - 8中顯示的2 - 4解碼器電路的門級描述如下:

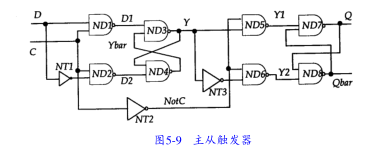

5.13 主從觸發器舉例

圖5 - 9所示的主從D觸發器的門級描述如下:

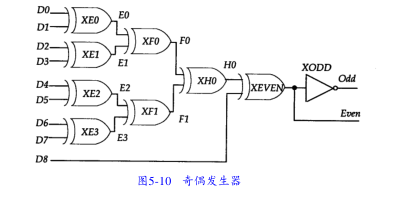

5.14 奇偶電路

圖5 - 1 0所示的9位奇偶發生器門級模型描述如下:

原文標題:verilog入門- 門電平模型化

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

電路

+關注

關注

172文章

5849瀏覽量

171909 -

Verilog

+關注

關注

28文章

1343瀏覽量

109986 -

HDL

+關注

關注

8文章

327瀏覽量

47336

原文標題:verilog入門- 門電平模型化

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字系統設計與Verilog HDL

Verilog硬件描述語言參考手冊

如何利用Verilog-A開發器件模型

Verilog HDL為門級電路建模的能力詳解

Verilog HDL為門級電路建模的能力詳解

評論