引言

S3C2410是三星公司生產的基于ARM920T內核的RISC微處理器,主頻率可達203MHz,適用于信息家電、Smart Phone、Tablet、手持設備、移動終端等領域。其中,集成的LCD控制器具有通用性,可與大多數的LCD顯示模塊接口。

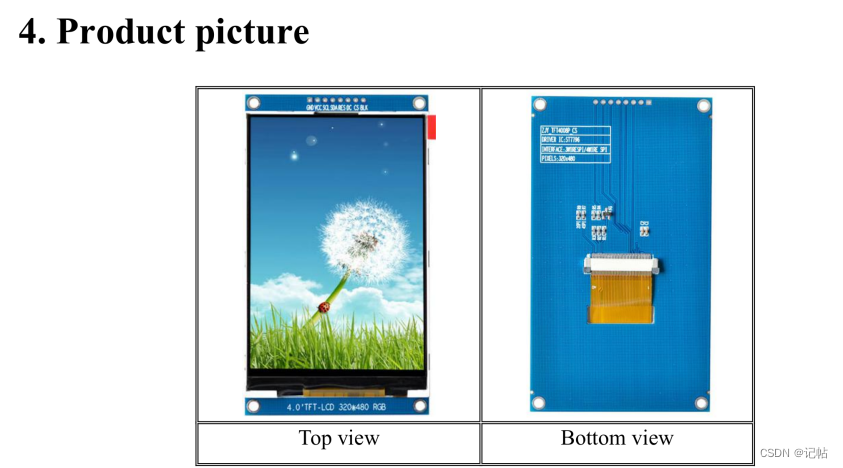

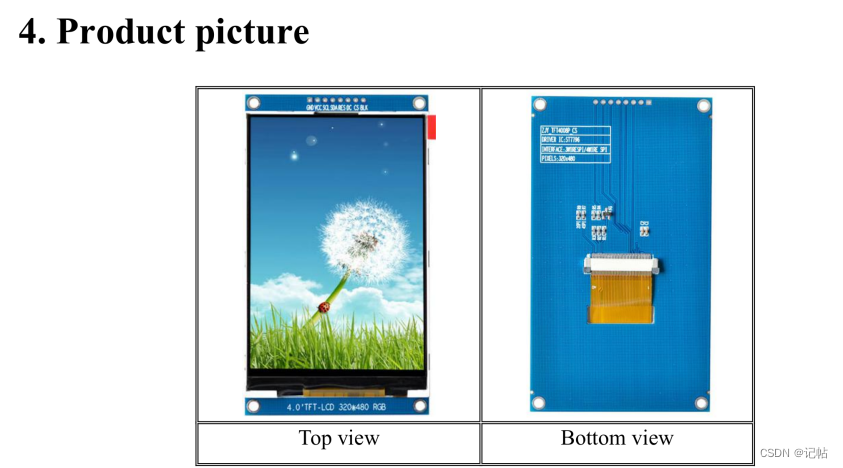

PD064VT5是一種用非晶硅TFT作為開關器件的有源矩陣液晶顯示器,該模塊包括TFT-LCD顯示屏、驅動電路和背光源,其接口為TTL電平。分辨率為640 x480像素,可通過18bit數據信號顯示262 144種色彩。

1 S3C2410的LCD控制器

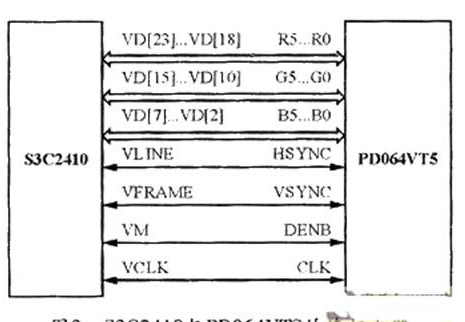

S3C2410中的LCD控制器可用于傳輸視頻數據并產生必要的控制信號(像VFRAME、VLINE、VCLK、VM等)。S3C2410的輸出視頻數據端口VD [23:0]的示意圖如圖1所示。

通常使用的LCD控制管腳的定義如下:

VCLK:像素時鐘信號;

VD [23:0]:LCD像素輸出端口;

VM/VDEN/TP:LCD驅動器的AC偏置信號(STN)/數據使能信號(TFT)/SEC TFT源驅動器數據加載脈沖信號復用端口。

1.1 S3C2410中的LCD控制寄存器

S3C2410的LCD控制寄存器主要有LCDCON1寄存器、LCDCON2寄存器、LCDCON3寄存器、LCDCON4寄存器和LCDCON5寄存器。

1.2 控制流程

由圖1可見,S3C2410中的LCD控制器由REGBANK、LCDCDMA、VIDPRCS、TIMEGEN和LPC3600組成。其中REGBANK有17個可編程寄存器組和256x16的調色板存儲器,可用來設定LCD控制器;LCDCDMA是一個專用DMA,可自動從幀存儲器傳輸視頻數據到LCD控制器,通過這個特殊的DMA,視頻數據可不經過CPU處理就在屏幕上顯示;VIDPRCS可接收從LCDCDMA來的視頻數據并將其修改到合適數據格式,然后經VD[23:0]送到LCD驅動器,如4/8單掃描或4雙掃描顯示模式;TIMEGEN則由可編程邏輯組成,可支持不同LCD驅動器接口時序和不同的速率,TIMEGEN用于產生VFRAME、VLINE、VCLK、VM等信號。

FIFO存儲器通常位于LCDCDMA。當FIFO為空或部分為空時,LCDCDMA要求從基于突發傳輸模式的幀存儲器中取出數據并存入要顯示的圖像數據,而這幀存儲器是LCD控制器在RAM中開辟的一片緩沖區。當這個傳輸請求被存儲控制器中的總線仲裁器接收后,系統存儲器就給內部FIFO成功傳輸4個字。FIFO的總大小是28個字。其中低位FIFOL是12個字,高位FIFOH是16個字。S3C2410有兩個FIFO,可支持雙掃描顯示模式。但在單掃描模式下只使用一個FIFO (FIFOH)。

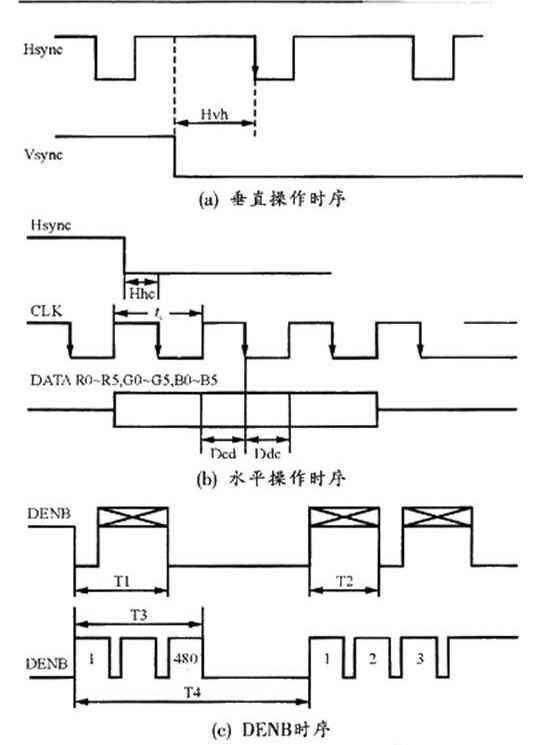

1.3 TFT控制器操作

S3C2410可支持STN-LCD和TFT-LCD,這里只介紹其對TFT-LCD的控制。TIMEGEN可產生LCD驅動器的控制信號(如VSYNC、HSYNC、VCLK、VDEN和LEND等)。這些控制信號與REGBANK寄存器組中的LCDCON1/2/3/4/5寄存器的配置關系相當密切。基于LCD控制寄存器中的這些可編程配置,TIMEGEN便可產生可編程控制信號來支持不同類型的LCD驅動器。而VSYNC和 HSYNC脈沖的產生則依賴于LCD-CON2/3寄存器的HOZVAL域和LINEVAL域的配置。HOZVAL和L NEVAL的值由LCD屏的尺寸決定:

HOZVAL=水平顯示尺寸-1 (1)

LINEVAL=垂直顯示尺寸-1 (2)

VCLK信號的頻率取決于LCDCON1寄存器中的CLKVAL域。VCLK和CLKVAL的關系如下(其中CLKVAL的最小值是0):

VCLK(Hz)=HCLK/[(CLKVAL+1)x2] (3)

一般情況下,幀頻率就是VSYNC信號的頻率,它與LCDCON1和LCDCON2/3/4寄存器的VSYNC、VB2PD、VFPD、LINEVAL、HSYNC、HBPD、HFPD、HOZVAL和CLKVAL都有關系。大多數LCD驅動器都需要與顯示器相匹配的幀頻率,幀頻率計算公式如下:

Frame Rate=1{[(VSPW+1)+(VBPD+1)+(LINEVAL+1)+(VFPD+1)]×[(HSPW+1)+(HBPD+1)+(HFPD+1)+(HOZVAL+1)]×[2×(CLKVAL+1)/(HCLK)]} (4)

參照PD064VT5的參數和公式(1)、(2)可得出:HOZVAL=639;LINEVAL=479。其余主要寄存器的值在下面給出。

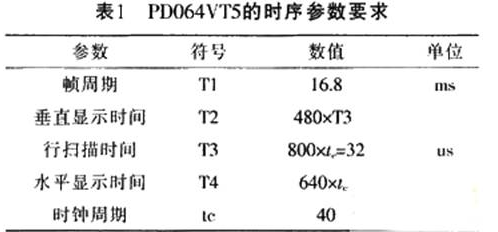

2 PD064VT5的邏輯時序

根據該時序要求,設計時可設定VM/VDEN信號作為LCD的ENAB信號,VCLK信號作為LCD的NCLK信號。要想得到合適的VM和VCLK波形,就要正確設定寄存器的值,并根據寄存器的值與VM和VCLK波形的關系設定如下關鍵寄存器的值:

HSPW=10;HBPD=100;HFPD=47;

VSPW=1;VBPD=37;VFPD=4

由于S3C2410的HCLK工作頻率大多在100MHz左右,因此,根據公式(3)可設CLKVAL=1。

圖3所示是S3C2410與PD064VTS的硬件連接電路。

開發該嵌入式系統驅動程序時,FrameBuffer可作為出現在Linux2.2.xx內核當中的一種驅動程序接口。對應的源文件在linux/driver s/video/目錄下,總的抽象設備文件為fbcon.c。這種接口將顯示設備抽象為幀緩沖區,用戶可以將它看成是顯示內存的一個映像。但在使用幀緩沖時,Linux是將顯卡置于圖形模式下的。

根據以上對LCD各主要寄存器設置的分析所得出的結果,筆者開發了基于FrameBuffer機制的S3C2410fb驅動程序。下面是調試成功的部分代碼,作用是初始化顯示屏幕和設置LCD控制寄存器的值。

4 結束語

本設計經過硬件方面的調試修改,在S3C2410開發板的VCLK腳和VM腳成功得到了PD064VT5所需的時鐘信號和復合控制信號;同時通過在軟件方面修改S3C2410的驅動程序,并經編譯整個系統后再重新寫到Flash中,可以在重啟后正確顯示原系統的靜態啟動畫面,而且畫面清晰穩定,達到了預期的效果。該裝置可用于工業控制和車載通信等領域的顯示輸出設備,如再加上適當的觸摸屏,還可組成方便可靠的輸入輸出設備。

編輯:jq

-

芯片

+關注

關注

454文章

50459瀏覽量

421951 -

ARM

+關注

關注

134文章

9057瀏覽量

366863 -

TFT-LCD

+關注

關注

13文章

151瀏覽量

31771

發布評論請先 登錄

相關推薦

屏驅可觸摸TFT-LCD mcu(專用開發板方案)

開源物聯網技術--TFT LCD屏驅動軟硬件設計分享

瑞薩e2studio----SPI驅動TFT-LCD屏

電視和監視器TFT-LCD面板的偏置電源TPS65161數據表

單電感四路輸出 TFT-LCD電源TPS6512x數據表

電視和監視器TFT-LCD面板的偏置電源TPS65160數據表

用于電視和監視器TFT-LCD面板的帶高速放大器的緊湊型LCD偏置IC TPS65165數據表

用于TFT-LCD電視面板的緊湊型LCD偏置電源TPS65167數據表

s3c2410中斷控制模塊的中斷源狀態寄存器是?

STM32H5開發(6)----SPI驅動TFT-LCD屏

瑞薩e2studio(26)----SPI驅動TFT-LCD屏

教你ARM芯片S3C2410的TFT-LCD驅動方法

教你ARM芯片S3C2410的TFT-LCD驅動方法

評論