最近完成了Arria10的原理圖設計,想做一些記錄,下面是關于FPGA配置的一些方式。

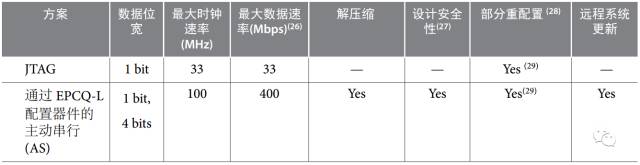

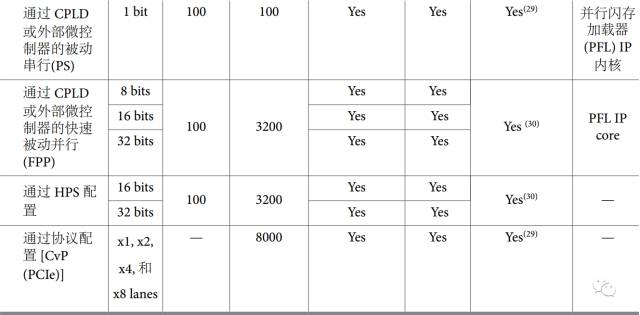

MSEL

將 MSEL 管腳直接連接到VCCPGM 或 GND,不需使用任何的上拉或下拉電阻,即可選擇出所需的

配置方案

? 不要通過微處理器或其他器件驅動 MSEL 管腳。

? 對“通過 HPS 的配置”(Configurationvia HPS)使用 PS 或 FPP MSEL 管腳設置。

三種主要的配置方式

1、主動配置方式(AS)

2、被動配置方式(PS)

3、JTAG方式

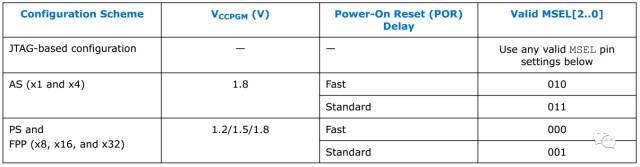

1、AS模式(active serial configuration mode):FPGA器件每次上電時作為控制器,由FPGA器件引導配置操作過程,它控制著外部存儲器和初始化過程,對配置器件EPCS主動發出讀取數據信號,從而把EPCS的數據讀入FPGA中,實現對FPGA的編程配置數據通過DATA0引腳送入FPGA,配置數據被同步在DCLK輸入上,1個時鐘周期傳送1位或者數據。AS是燒到FPGA的配置芯片里保存的,每次上電就寫到FPGA里。

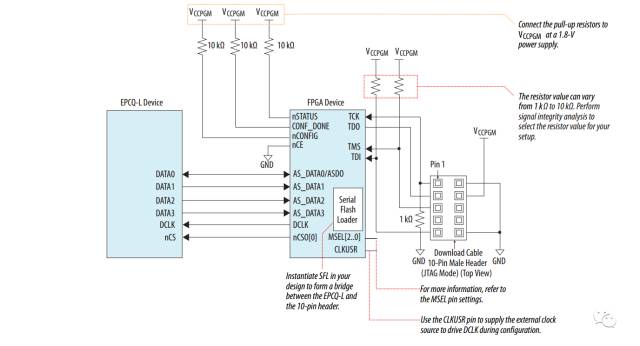

(1)AS programming interface

當編程 EPCQ-L 器件時,下載電纜通過驅動 nCE 管腳為高電平而禁用對 AS 接口的訪問。nCONFIG線也被拉低以保持 Arria 10 器件處于復位階段。編程完成后,下載電纜釋放 nCE 和 nCONFIG,從而使得 下拉和 上拉電阻能夠分別驅動 GND 和 VCCPGM 的管腳。使用下載電纜進行 EPCQ-L 編程期間,DATA0 將編程數據、操作指令和地址信息從下載電纜傳輸到 EPCQ-L。使用下載電纜進行 EPCQ-L 驗證期間,DATA1 將編程數據返回到下載電纜。

(2)JTAG interface

使用 AS 編程接口時, 配置數據通過 Quartus Prime 或任何支持的第三方軟件被編程到 EPCQ-L。使用 JTAG 接口時,稱為 SFL IP core 的 Altera IP 必須被下載到 Arria 10 器件以形成 JTAG 接口和 EPCQ-L 之間的橋接。這樣就能夠使用 JTAG 接口直接編程 EPCQ-L。這種方式的燒寫文件是.JIC。

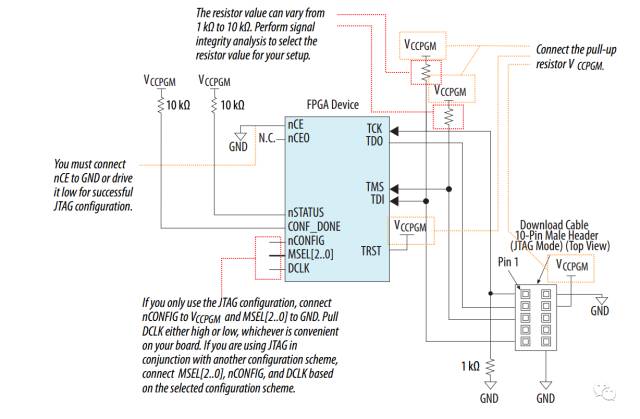

2、JTAG模式

JTAG:JTAG是直接配置到FPGA里面的,由于是SRAM,斷電后要重燒;JTAG燒寫的時SRAM對象文件(.sof)

JTAG配置的時間只與目標芯片的型號有關,而與具體應用無關。

JTAG Configuration of a Single Device Using a Download Cable

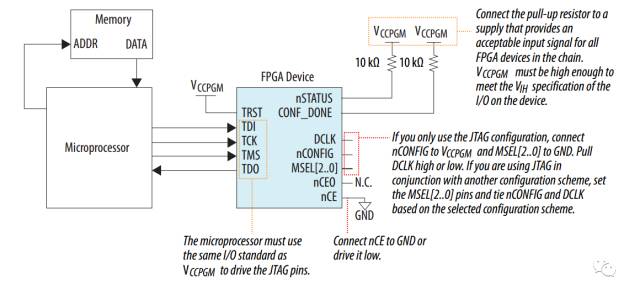

JTAG Configuration of a Single Device Using a Microprocessor

對于這種連接方式,是把數據寫入到存儲器中,每次上電時由控制器去配置FPGA。

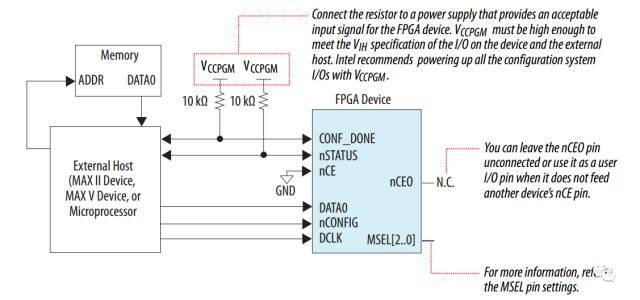

3、被動配置方式(PS)

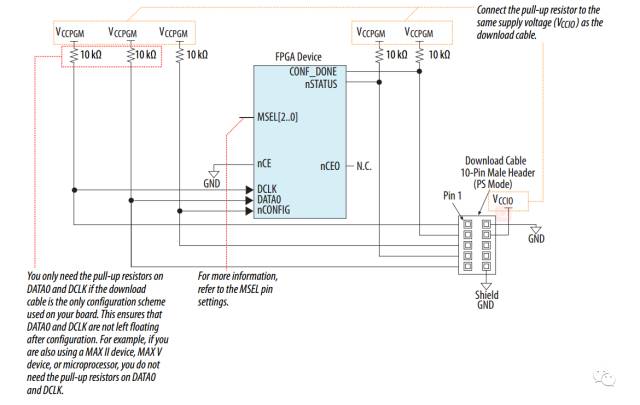

PS模式(passive serial configuration mode):由外部計算機或控制器讀取外部存儲器的配置數據寫入到FPGA的配置過程。控制配置過程的操作是在外部處理器上實現的,對于MAX V和MAX II可以通過PFL IP來實現這個過程,對于PC主機可以通過下載線來實現該過程。被動配置模式又分為串行被動模式和并行被動模式。該模式可以實現對FPGA在線可編程。

Single Device PS Configuration Using an External Host

Single Device PS Configuration Using an Intel FPGA Download Cable

這種方式我是沒有實現過的,所以了解的可能不是很正確。

原文標題:FPGA配置的三種主要方式

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

處理器

+關注

關注

68文章

19178瀏覽量

229200 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602034

原文標題:FPGA配置的三種主要方式

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA有哪些主要配置方式?

FPGA有哪些主要配置方式?

評論