結 構 建 模

本章講述Verilog HDL中的結構建模方式。結構建模方式用以下三種實例語句描述:

? Gate實例語句

? UDP實例語句

? Module實例語句

第5章和第6章已經討論了門級建模方式和U D P建模方式,本章講述模塊實例語句。

9.1 模塊

Verilog HDL中,基本單元定義成模塊形式,如下所示 :

m o d u l e m o d u l e _ n a m e(p o r t _ l i s t) ;

D e c l a r a t i o n s _ a n d _ S t a t e m e n t s

e n d m o d u l e

端口隊列p o rt _ l i s t列出了該模塊通過哪些端口與外部模塊通信。

9.2 端口

模塊的端口可以是輸入端口、輸出端口或雙向端口。缺省的端口類型為線網類型(即wire類型)。但是,端口可被顯式地指定為線網。輸出或輸入輸出端口能夠被重新聲明為reg型寄存器。無論是在線網說明還是寄存器說明中,線網或寄存器必須與端口說明中指定的長度相同。下面是一些端口說明實例。

m o d u l e M i c r o (PC, Instr, NextAddr );

/ /端口說明

i n p u t [3:1] P C;

o u t p u t [1:8] I n s t r;

i n o u t [16:1] N e x t A d d r;

/ /重新說明端口類型:

w i r e [16:1] N e x t A d d r; //該說明是可選的,但如果指定了,就必須與它的端口說明保持相同長度。

r e g [1:8] I n s t r;

/ /I n s t r已被重新說明為r e g類型,因此它能在always 語句或在i n i t i a l語句中賦值。

。 . 。

e n d m o d u l e

9.3 模塊實例語句

一個模塊能夠在另外一個模塊中被引用,這樣就建立了描述的層次。模塊實例語句形式

如下:

module_name instance_name (p o r t _ a s s o c i a t i o n s) ;

信號端口可以通過位置或名稱關聯;但是關聯方式不能夠混合使用。端口關聯形式如下:

p o r t _ e x p r / /通過位置。

.P o r t N a m e (p o r t _ e x p r) / /通過名稱。

p o rt _ e x p r可以是以下的任何類型:

1) 標識符(r e g或n e t)

2) 位選擇

3) 部分選擇

4) 上述類型的合并

5) 表達式(只適用于輸入端口)

在位置關聯中,端口表達式按指定的順序與模塊中的端口關聯。在通過名稱實現的關聯中,模塊端口和端口表達式的關聯被顯式地指定,因此端口的關聯順序并不重要。下例使用兩個半加器模塊構造全加器;邏輯圖如圖 9 - 1所示。

在第一個模塊實例語句中, H A是模塊的名字 ,h 1是實例名稱,并且端口按位置關聯,即

信號P與模塊(H A)的端口A連接,信號Q與端口B連接,S 1與S連接,C 1與模塊端口C連接。在第二個實例中,端口按名稱關聯,即模塊( H A)和端口表達式間的連接是顯示地定義

的。下例是使用不同端口表達式形式的模塊實例語句。

Micro M1 (U d I n[3:0], {WrN, RdN}, S t a t u s[0], S t a t u s[ 1 ] ,

& U d O u t [0:7], T x D a t a) ;

這個實例語句表示端口表達式可以是標識符( T x D a t a)、位選擇(S t a t u s[ 0 ]) 、 部分位選擇(U d I n[ 3 : 0 ])、合并({Wr N,R d N})或一個表達式(& u d O u t[ 0 : 7 ]);表達式只能夠連接到輸入端口。

9.3.1 懸空端口

在實例語句中,懸空端口可通過將端口表達式表示為空白來指定為懸空端口,例如:

DFF d1 ( .Q(Q S), .Q b a r(), .D a t a( D ) ,

.P r e s e t(), .C l o c k(CK)); //名稱對應方式。

DFF d2 (QS, , D, , CK ) ; / /位置對應方式。

/ /輸出端口Q b a r懸空。

/ /輸入端口P r e s e t打開,其值設定為z。

在這兩個實例語句中,端口Q b a r和P re s e t懸空。

模塊的輸入端懸空,值為高阻態z。模塊的輸出端口懸空,表示該輸出端口廢棄不用。

9.3.2 不同的端口長度

當端口和局部端口表達式的長度不同時,端口通過無符號數的右對齊或截斷方式進行匹

配。例如:

在對C h i l d模塊的實例中, B d l[ 2 ]連接到P b a[ 0 ],B d l[1] 連接到P b a[ 1 ],余下的輸入端口P b a[ 5 ]、P b a[ 4 ]和P b a[ 3 ]懸空,因此為高阻態 z。與之相似,M p r[ 6 ]連接到P p y[ 0 ],M p r[ 5 ]連接到P p y[ 1 ],M p r[4] 連接到P p y[ 2 ]。參見圖9 - 2。

9.3.3 模塊參數值

當某個模塊在另一個模塊內被引用時,高層模塊能夠改變低層模塊的參數值。模塊參數值的改變可采用下述兩種方式:

1) 參數定義語句(d e f p a r a m);

2) 帶參數值的模塊引用。

1. 參數定義語句

參數定義語句形式如下:

d e f p a r a m hier_path_name1 = v a l u e 1,

hier_path_name2 = v a l u e 2, 。..;

較低層模塊中的層次路徑名參數可以使用如下語句顯式定義(層次路徑名在下一章中講述)。下面是一個例。模塊FA和H A已在本節前面描述過。

2. 帶參數值的模塊引用

在這種方法中,模塊實例語句自身包含有新的參數值。下面的例子在前幾節中也出現過,本例中采用帶參數的模塊引用方式。

模塊實例語句中參數值的順序必須與較低層被引用的模塊中說明的參數順序匹配。在模塊TO P 3中,A N D _ D E L AY已被設置為5,X O R _ D E L AY已被設置為2。

模塊TO P 3和TO P 4解釋說明了帶參數的模塊引用只能用于將參數值向下傳遞一個層次(例如,O R _ D E L AY),但是參數定義語句能夠用于替換層次中任意一層的參數值。

應注意到:在帶參數的模塊引用中,參數的指定方式與門級實例語句中時延的定義方式相似;但由于對復雜模塊的引用時,其實例語句不能像對門實例語句那樣指定時延,故此處不會導致混淆。參數值還可以表示長度。下面是通用的 M×N乘法器建模的實例。

第1個值8指定了參數E M的新值,第2個值6指定了參數E N的新值。

9.4 外部端口

在迄今為止所見到的模塊定義中,端口表列舉出了模塊外部可見的端口。例如,

A r b、C t r l、M e m _ B l k和B y t e為模塊端口。這些端口同時也是外部端口,即在實例中,當采用名稱關聯方式時,外部端口名稱用于指定相互連接。下面是模塊 S c r a m _ A的實例。

Scram_A SX( .B y t e(B 1) , .M e m _ B l k(M 1) , .C t r l(C 1) , .A r b(A 1) ) ;

在模塊S c r a m _ A中,外部端口名稱隱式地指定。Verilog HDL中提供顯式方式指定外部端

口名稱。這可以通過按如下形式指定一個端口來完成:

.e x t e r n a l _ p o r t _ n a m e(i n t e r n a l _ p o r t _ n a m e)

下面是同一個例子,只不過是顯式地指定外部端口。

模塊S c r a m _ B在此實例中指定的外部端口是 D a t a、C o n t ro l、M e m _ Wo rd和A d d r。端口表顯式地表明了外部端口和內部端口之間的連接。注意外部端口無需聲明,但是模塊的內部端口卻必須聲明。外部端口在模塊內不可見,但是卻要在模塊實例語句中使用,而內部端口因為在模塊中可見,所以必須在模塊中說明。在模塊實例語句中,外部端口的使用如下所示:

Scram_B S1 ( .A d d r(A 1) , .D a t a(D 1) , .C o n t r o l(C 1) ,

.M e m _ W o r d(M 1) ) ;

在模塊定義的端口表中,這兩種概念不能混淆,即在模塊定義中所有端口必須指定顯式的端口名稱,或者沒有一個端口帶有顯式的端口名稱。如果模塊端口通過位置連接,則模塊實例語句中不能使用外部端口名稱。

內部端口名稱可以是標識符,也可以是下述類型的表達式:

? 位選擇;

? 部分選擇;

? 位選擇、部分選擇和標識符的合并。

例如,

在S c r a m _ C的模塊定義中,端口表包括部分選擇( A r b[ 0 : 2 ])、標識符( C t r l)、合并({M e m _ B l k[ 0 ],M e m _ B l k[ 1 ] } )和位選擇(B y t e[ 3 ])。在內部端口是位選擇、部分選擇或合并的情況下,沒有隱式地指定外部端口名。因此,在這樣的模塊實例語句中,模塊端口必須通過位置關聯相互連接。例如,

Scram_C SYA (L 1[ 4 : 6 ] ,C L , M M Y[ 1 : 0 ] ,B T) ;

在這個實例語句中,端口通過位置關聯相連接,因此 L 1[ 4∶6 ]連接到A r b[ 0∶2 ],C L連接

到C t r l,M M Y[ 1 ]連接到M e m _ B l k[ 0 ] ,M M Y[ 0 ]連接到M e m _ B l k[ 1 ],B T連接到B y t e[ 3 ]。

若使用端口名稱關聯(即當內部端口不是標識符時),必須對模塊中的端口指定外部端口名。如下面的S c r a m _ D模塊定義所示。

在S c r a m _ D模塊實例語句中,端口既能夠使用位置連接,也能夠使用名稱連接,但是不能混合使用。下例的模塊實例語句端口通過名稱連接。

Scram_D SZ ( .D a t a(L 1[ 4 : 6 ] , .C o n t r o l(C L) ,

.M e m _ W o r d(M M Y[ 1 : 0 ],.A d d r(B T) ) ;

模塊中可以只有外部端口而沒有內部端口。即模塊在引用中其外部端口可以懸空,不與內部信號相連。例如:

模塊S c r a m _ E 有兩個外部端口D a t a和A d d r,這兩個端口在使用時被懸空。

一個內部端口是否能與多個外部端口連接?Verilog HDL允許這樣連接。例如,

內部端口C o n d O u t 與兩個外部端口B和C連接,所以C o n d O u t的值在B和C上都出現。

9.5 舉例

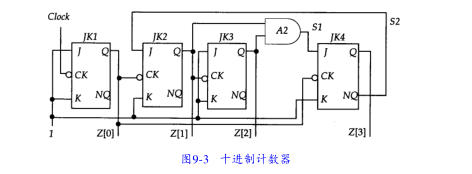

下例采用結構模型描述十進制計數器。十進制計數器的邏輯圖如圖 9 - 3所示。

注意常數作為輸入端口信號的用法,以及懸空端口。

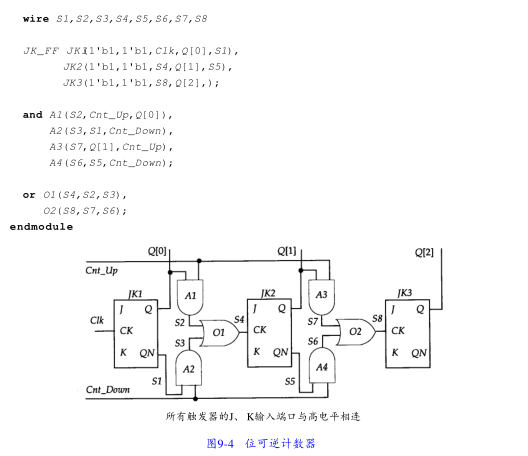

下面是另一個例子,3位可逆計數器的邏輯結構如圖9 - 4所示,其結構描述如下:

責任編輯:lq6

-

UDP

+關注

關注

0文章

322瀏覽量

33876 -

端口

+關注

關注

4文章

955瀏覽量

32014 -

Verilog HDL

+關注

關注

17文章

125瀏覽量

50385 -

可逆計數器

+關注

關注

0文章

2瀏覽量

6761

原文標題:Verilog入門-結構建模

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Verilog HDL中的結構建模方式細述

Verilog HDL中的結構建模方式細述

評論