3 月 16 日,當(dāng)?shù)貢r(shí)間周一 AMD 發(fā)布名為 “米蘭”(Milan)的服務(wù)器芯片,旨在從競(jìng)爭(zhēng)對(duì)手英特爾手中奪取更多的市場(chǎng)份額。

AMD 表示,公司最新發(fā)布的 “米蘭”服務(wù)器芯片比目前最好的數(shù)據(jù)中心芯片處理速度更快。據(jù)悉,AMD 完成該芯片的設(shè)計(jì),并委托臺(tái)積電采用 7 納米芯片制造工藝來實(shí)現(xiàn)量產(chǎn)。

在AMD服務(wù)器處理器的演進(jìn)路線圖上,“米蘭”具有重要的戰(zhàn)略位置,經(jīng)歷了前兩代的“那不勒斯”和“羅馬”之后,對(duì)于實(shí)現(xiàn)在數(shù)據(jù)中心市場(chǎng)的進(jìn)一步攻城略地,“米蘭”被寄予厚望。

發(fā)布會(huì)上,AMD高級(jí)副總裁兼服務(wù)器業(yè)務(wù)總經(jīng)理Dan McNamara,AMD 全球院士、Zen核心首席設(shè)計(jì)師Mike Clark,AMD院士及SoC架構(gòu)師Noah Beck,AMD EPYC產(chǎn)品管理全球副總裁Ram Peddibhotla等接受了集微網(wǎng)在內(nèi)的媒體采訪,從架構(gòu)、設(shè)計(jì)、產(chǎn)品等方面詳細(xì)介紹了“米蘭”背后的更多細(xì)節(jié)。

Dan McNamara表示,“米蘭”的發(fā)布將會(huì)進(jìn)一步鞏固AMD在數(shù)據(jù)中心市場(chǎng)中的地位,無論是從核心還是系統(tǒng)層面都體現(xiàn)出優(yōu)越的性能。對(duì)于市場(chǎng)用戶而言,在整體擁有成本方面,“米蘭”將帶來更高的價(jià)值,同時(shí)AMD也在加速布局生態(tài),推出圍繞“米蘭”的更多應(yīng)用。

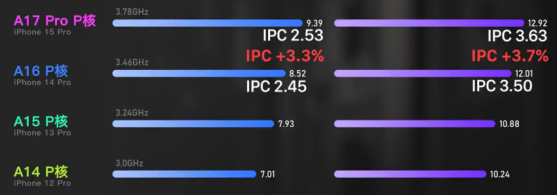

7nmZen3架構(gòu) 19%IPC性能提升

自2017年重返數(shù)據(jù)中心市場(chǎng)開始,AMD一直追求架構(gòu)上的創(chuàng)新以及由此帶來的性能飛越,從Zen1到到Zen3,都在IPC性能表現(xiàn)方面實(shí)現(xiàn)了顯著提升。如采用Zen2架構(gòu)的“羅馬”發(fā)布時(shí),實(shí)現(xiàn)了較上一代15%的IPC性能提升,而此次Zen3架構(gòu),實(shí)現(xiàn)了約19%的IPC性能提高,遠(yuǎn)高于行業(yè)平均水平。

據(jù)Mike Clark介紹,要實(shí)現(xiàn)這樣的進(jìn)步,必須在整個(gè)架構(gòu)的每個(gè)環(huán)節(jié)去分別優(yōu)化。首先,在Zen3上,AMD改善了分支預(yù)測(cè)的功能,不僅提高了準(zhǔn)確性同時(shí)能夠更快的到達(dá)目標(biāo),同時(shí)在系統(tǒng)中能發(fā)出更快指令,更高指數(shù)的吞吐量,增加了更多的流水線提高吞吐量,同時(shí)也為推理方面的工作負(fù)載去更強(qiáng)的賦能。從四核到八核都讓整個(gè)通訊的速度加快,效果更完善,即使是在線程數(shù)比較低的系統(tǒng)中由于能夠?qū)崿F(xiàn)共享內(nèi)存調(diào)用,可以降低有效的內(nèi)存訪問的延遲。

具體而言,從Zen2到Zen3,在前端改進(jìn)方面,AMD將BTB提高了一倍,達(dá)到1024。同時(shí)增加了分支預(yù)測(cè)器的帶寬,另外在分支預(yù)測(cè)中消除了冒泡現(xiàn)象,因?yàn)槊芭莠F(xiàn)象在很多架構(gòu)中是常見問題,能夠更快的從誤測(cè)中去恢復(fù),能夠更快的尋址。

Mike Clark表示,對(duì)于更大的服務(wù)器工作負(fù)載而言,Zen3可以更無縫的在op cache和I cache切換,實(shí)現(xiàn)現(xiàn)更高顆粒度的流水線切換。

在執(zhí)行部分,Zen3首先針對(duì)整數(shù)設(shè)置了專用的分支和ST數(shù)據(jù)揀選器,有更大的窗口,減少了某些運(yùn)行時(shí)延,在浮點(diǎn)方面增加兩個(gè)位寬的調(diào)度和分發(fā),更快的FMAC周期,還有兩條INT8的IMAC流水線。

在加載存儲(chǔ)這部分Zen3有三個(gè)加載和兩個(gè)存儲(chǔ),操作靈活性增加,也對(duì)內(nèi)存依賴性的檢測(cè)做了優(yōu)化,同時(shí)對(duì)于這些非常隨機(jī)內(nèi)存的操作我們也提供了6個(gè)頁(yè)表查詢器去實(shí)現(xiàn)更好的TLB查詢。

在指令集方面,在加速、加密和解密算法上Zen3擴(kuò)展了AVX2指令到256位。Mike Clark指出安全是改進(jìn)最大的部分,首先對(duì)SEV的改進(jìn),限制中斷的注入,限制惡意管理程序注入SEV-ES訪客中斷/異常類型,還有能夠?qū)⒄{(diào)試寄存器添加到交換狀態(tài)中。

此外,Mike Clark介紹,在一代EPYC產(chǎn)品投入市場(chǎng)時(shí),行業(yè)正在遭遇幽靈攻擊,現(xiàn)在看當(dāng)時(shí)的應(yīng)對(duì)方式并不是最優(yōu)解,但到目前三代時(shí),應(yīng)該說AMD從架構(gòu)方面已經(jīng)做好了強(qiáng)防御,同時(shí)對(duì)性能的折損也能夠降到最低,在提升的IPC性能的同時(shí),也大大增強(qiáng)了系統(tǒng)的安全性和穩(wěn)定性。

目前 AMD 采用與第三方芯片制造商合作的方式量產(chǎn)。而英特爾采用的是自行制造芯片的不同戰(zhàn)略,但最近一代芯片制造技術(shù)的延遲令其備受困擾。相比而言,“米蘭”芯片及其前輩的表現(xiàn)都超過了英特爾芯片,幫助 AMD 搶到了更多市場(chǎng)份額,并贏得了 Alphabet 旗下谷歌等客戶的青睞。

不過英特爾即將反擊。分析師預(yù)計(jì),英特爾將在未來幾周推出最新的 “冰湖”(Ice Lake)服務(wù)器芯片,這將是首款采用英特爾 10 納米制造工藝量產(chǎn)的服務(wù)器芯片。英特爾 10 納米制造工藝所生產(chǎn)芯片的性能相當(dāng)于 7 納米制造工藝的 “米蘭”芯片。

無論這兩款芯片的速度如何,但 AMD 仍有望擁有一些優(yōu)勢(shì),比如每個(gè)芯片上的計(jì)算內(nèi)核數(shù)更多,這使得芯片可以同時(shí)處理更多的軟件應(yīng)用程序。

本文由電子發(fā)燒友綜合報(bào)道,內(nèi)容參考自IT之家、AMD、科技先知,轉(zhuǎn)載請(qǐng)注明以上來源。

-

amd

+關(guān)注

關(guān)注

25文章

5441瀏覽量

133937 -

intel

+關(guān)注

關(guān)注

19文章

3480瀏覽量

185752

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

美國(guó)多IP服務(wù)器和美國(guó)多服務(wù)器有什么區(qū)別

GPU服務(wù)器和傳統(tǒng)的服務(wù)器有什么區(qū)別

所謂的7nm芯片上沒有一個(gè)圖形是7nm的

ai服務(wù)器和通用服務(wù)器的區(qū)別在哪

超微發(fā)布新款AMD H13代CPU服務(wù)器產(chǎn)品

存內(nèi)計(jì)算——助力實(shí)現(xiàn)28nm等效7nm功效

AMD 搶先發(fā)布 7nm 服務(wù)器芯片 “米蘭”

AMD 搶先發(fā)布 7nm 服務(wù)器芯片 “米蘭”

評(píng)論