人類接受信息中有70%是視頻信息。相對于語音和文字信息來說,視頻信息更直觀,信息量更大,處理和傳輸技術(shù)也更為復(fù)雜。視頻監(jiān)控系統(tǒng)作為視頻技術(shù)的一個應(yīng)用領(lǐng)域,在軍事安全等領(lǐng)域發(fā)揮著重要的作用。目前視頻監(jiān)控系統(tǒng)主要采用模擬和數(shù)字兩種技術(shù)。數(shù)字視頻技術(shù)不僅能減少視頻傳輸引起的失真,還能對視頻信息進(jìn)行分析、識別及有效信息提取。因此隨著數(shù)字技術(shù)的進(jìn)步,數(shù)字視頻監(jiān)控將成為今后的發(fā)展方向。

數(shù)字視頻監(jiān)控的一項(xiàng)核心技術(shù)是視頻壓縮技術(shù)。視頻信號包含大量的數(shù)據(jù)信息,通過壓縮手段把信息數(shù)據(jù)量壓下來,以壓縮形式存儲和傳輸,既緊縮了存儲空間,又提高了通信干線的傳輸效率,同時也使計算機(jī)實(shí)時處理音頻、視頻信息,以保證播放出高質(zhì)量的視頻、音頻節(jié)目成為可能。MPEG-2 標(biāo)準(zhǔn)是運(yùn)動圖像專家組于1995 年正式公布的。它的用處在于可以使運(yùn)動視音頻數(shù)據(jù)作為一種計算機(jī)可處理的數(shù)據(jù)形式,并且可以存儲在各種存儲媒體上,可以在現(xiàn)存或未來的網(wǎng)絡(luò)上發(fā)送、接受,并且可以在現(xiàn)存或未來的廣播信道上傳播。本文討論的就是一種采用MPEG-2 壓縮標(biāo)準(zhǔn)的數(shù)字視頻監(jiān)控系統(tǒng)。

MPEG-2 視頻數(shù)據(jù)壓縮原理

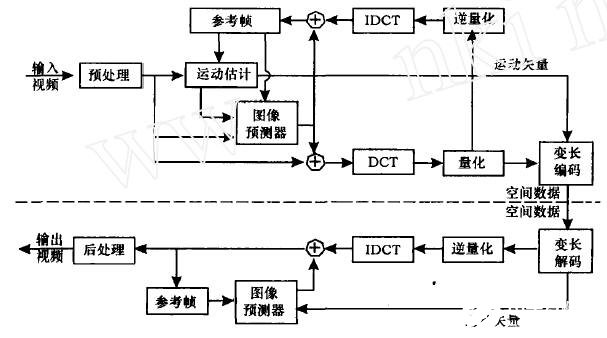

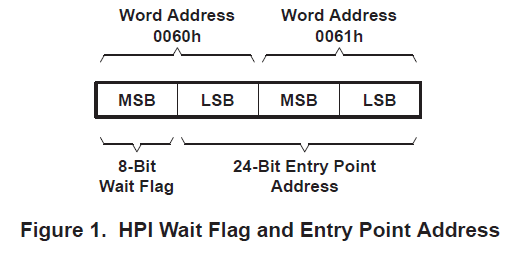

MPEG-2 圖像壓縮的原理是利用了圖像中的兩種特性:空間相關(guān)性和時間相關(guān)性。利用離散余弦變換(DCT) 編碼技術(shù)降低空間數(shù)據(jù)相關(guān)性;運(yùn)動估計和預(yù)測技術(shù)降低鄰近幀像素的時間相關(guān)性來實(shí)現(xiàn)幀間數(shù)據(jù)壓縮。MPEG-2 基本編解碼模型如圖1 所示。圖中虛線上半部分完成視頻編碼功能,虛線下半部分完成視頻解碼功能。

編碼器中的預(yù)處理器對原始圖像中的噪聲進(jìn)行過濾,并將圖像分割成宏塊。對于幀內(nèi)編碼,宏塊經(jīng)過DCT 變換、量化和變長編碼后輸出壓縮的視頻數(shù)據(jù);對于幀間編碼,運(yùn)動估計對宏塊的運(yùn)動進(jìn)行估測和補(bǔ)償來減少圖像的時序冗余;圖像預(yù)測器根據(jù)參考幀來預(yù)測當(dāng)前幀,兩者之間的差值經(jīng)過DCT變換、量化和變長編碼后輸出,由于差值較小可以使編碼所需比特數(shù)減少很多;逆量化和IDCT的目的是為了完成參考幀的重現(xiàn)。解碼器中變長解碼、逆量化和IDCT重構(gòu)幀內(nèi)編碼的圖像,圖像預(yù)測器根據(jù)參考幀和運(yùn)動矢量完成幀間編碼圖像的重現(xiàn)。

圖1 MPEG-2 編解碼模型圖

系統(tǒng)設(shè)計

系統(tǒng)硬件設(shè)計

系統(tǒng)總體結(jié)構(gòu)

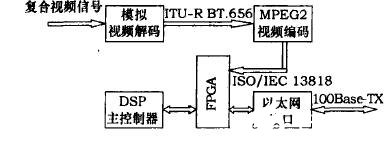

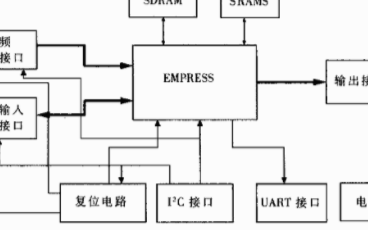

系統(tǒng)主要由兩個部分組成:一是模擬視頻數(shù)據(jù)解碼和數(shù)字視頻數(shù)據(jù)編碼子系統(tǒng)。二是視頻碼流以太網(wǎng)傳送子系統(tǒng)。此外還有電源子系統(tǒng)、JTAG調(diào)試子系統(tǒng)等,這里不做詳述。系統(tǒng)的基本結(jié)構(gòu)圖如圖2 所示。

圖2 系統(tǒng)原理圖

系統(tǒng)首先通過模擬攝像機(jī)將外部的信號轉(zhuǎn)換為PAL 制的復(fù)合視頻信號,然后模擬視頻解碼和數(shù)字視頻編碼子系統(tǒng)將模擬攝像機(jī)的PAL 制式復(fù)合視頻信號壓縮為MPEG-2 格式視頻流,最后,DSP 控制器將視頻流封包通過以太網(wǎng)傳送子系統(tǒng)以百兆的帶寬傳送出去。

模擬視頻解碼和數(shù)字視頻編碼子系統(tǒng)

模擬視頻解碼部分的任務(wù)是對輸入的PAL 制視頻信號進(jìn)行采樣量化編碼后,轉(zhuǎn)換成標(biāo)準(zhǔn)數(shù)字視頻信號。我們選用的PHILIPS 公司的SAA7114 芯片。SAA7114 是一種高性能的單片NTSC/PAL/SECAM復(fù)合視頻解碼器,低功耗、低價格、具有卓越的三線自適應(yīng)梳狀濾波器能克服傳統(tǒng)濾波器的人工痕跡而保證全屏視頻分辨率,具有靈活的像素端口,并具有外圍電路簡單和易于編程等優(yōu)點(diǎn)。

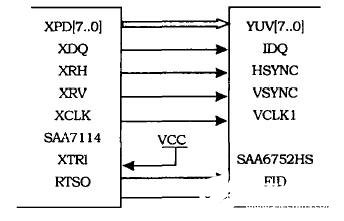

在系統(tǒng)中, SAA7114將模擬信號解碼后得到的信號轉(zhuǎn)換為ITU-RBT.656 數(shù)字視頻格式,可以與SAA6752 直接相連,如圖3所示。系統(tǒng)中采用SAA7114的視頻輸出口為X-port作為數(shù)據(jù)輸出口。X-port的信號分為以下幾類:

a、數(shù)據(jù)信號XPD7-XPD0 :輸出解碼后的數(shù)據(jù)值;

b、時鐘信號XCLK:作為系統(tǒng)參考時鐘信號;

圖3 SAA7114 與SAA6752 的接口

c、行同步信號XRH 和場同步信號XRV :當(dāng)輸出為行同步信號和場同步信號時,這兩個信號有效;

d、XDQ 作為輸出數(shù)據(jù)有效指示;

e、XDRI 控制X-port 是作為輸入口還是輸出口。

RTS0 輸出奇數(shù)場或偶數(shù)場的標(biāo)志位。

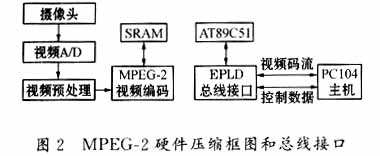

MPEG-2 視頻編碼部分是整個系統(tǒng)的關(guān)鍵部分,它將ITU-RBT.656格式的數(shù)據(jù)編碼壓縮為ISO/IEC 13818的MPEG2傳輸流(TS) 。這一部分選用的是Philips 公司的SAA6752HS芯片。它是一款高集成度低成本的單芯片音視頻編碼芯片,可以執(zhí)行全部的視頻編碼、噪聲濾波和運(yùn)動估計的功能。另外,通過I2C 總線就能實(shí)現(xiàn)對SAA6752HS 控制,因此SAA6752HS 只需要從主控制處理器的I2C總線上傳輸少量設(shè)置編碼的參數(shù)就可以使SAA6752HS 開始編碼工作。SAA6752 與TMS320VC5502 主控DSP 的連接如圖4 所示。

SAA6752 的輸出接口各引腳功能如下:

a、PDO[7. 。 0 ]輸出數(shù)據(jù);

b、PDIOCLK輸出參考時鐘,可以設(shè)為9MHz 或6. 75MHz ;

c、PDOAV 信號表示輸出的是視頻數(shù)據(jù)還是音頻數(shù)據(jù);

d、PDOVAL 信號表示輸出的數(shù)據(jù)是否有效;

e、PDOSYNC 表示輸出的是數(shù)據(jù)包的第一個字節(jié)。

圖4 SAA6752HS 與TMS320VC5502 的連接圖

需要說明的是,圖4 中的移位寄存器、FIFO、計數(shù)器(模4) ,計數(shù)器2 (模47) 是用FPGA 實(shí)現(xiàn)。DSP 控制器我們選用的是TI 公司中的TMS320VC5502(‘5502) 芯片,它的核心電壓只有1.2V ,功耗僅0. 05mW/MIPs ,性能達(dá)600MIPS。這款芯片尤其適合于數(shù)據(jù)速率高,運(yùn)算量大,又要求低功耗的系統(tǒng)。同時TMS320VC5502 集成了豐富外圍設(shè)備,比如32 位的外部內(nèi)存接口(EMIF) ,可以與系統(tǒng)中的網(wǎng)卡連接;內(nèi)部集成的I2C 總線接口,便于對Philips 的視頻芯片進(jìn)行控制。另外,它還對外提供JTAG口,這使系統(tǒng)的調(diào)試可依靠JTAG仿真器和TI 公司最新的DSP 開發(fā)平臺CCS 而變得更為方便。

視頻流以太網(wǎng)傳送子系統(tǒng)

以太網(wǎng)接口部分主要用來將打好包的數(shù)據(jù)傳到遠(yuǎn)程主機(jī)上, 我們使用的是SMSC 公司的LAN91C111 芯片,它是一塊高性能非PCI 接口的10M/100M以太網(wǎng)接口的芯片。LAN91C111 采用的是一種流量I/O 的工作方式。所謂流量IO 方式曾經(jīng)是為磁盤與處理器接口而設(shè)計的,它比ISA 的DMA 方式具有更高的效能而且能更方便的使用。LAN91C111 對數(shù)據(jù)的處理能力也很強(qiáng),其理論上最大數(shù)據(jù)處理能力為320Mbit/s = 40MB/s。由于LAN91C111 具有MMU 功能使得整個系統(tǒng)具有較高的網(wǎng)絡(luò)性能和較低的系統(tǒng)開銷。

圖5 LAN91C111 的接口圖

由LAN91C111 組成的網(wǎng)絡(luò)接口如圖5 所示。LAN91C111 通過局部總線接口把CPU 傳過來的數(shù)據(jù),通過內(nèi)部的MAC 控制器進(jìn)行數(shù)據(jù)的封裝,物理層收發(fā)器(PHY) 將數(shù)據(jù)傳輸?shù)矫}沖變壓器上,這樣由噪聲產(chǎn)生的錯誤可以降至最低,保證數(shù)據(jù)的正確傳輸。同時,LAN91C111 的物理層收發(fā)器還能接收網(wǎng)絡(luò)上的數(shù)據(jù)包,并且MAC 可以進(jìn)行載波偵聽、碰撞檢測協(xié)議和CRC 校驗(yàn)功能;此外LAN91C111 還具有大的緩沖區(qū)可以提高整個電路的效率,LED控制器可以標(biāo)識網(wǎng)絡(luò)接口的狀態(tài)。LAN91C111 的主機(jī)端的接口比較靈活,它可以支持異步或同步方式的傳輸,還可以支持非觸發(fā)方式和觸發(fā)方式(Burst mode) 的傳輸。為了提高系統(tǒng)的吞吐率,由DSP 向網(wǎng)卡傳送數(shù)據(jù)時,通過DSP 的EMIF 接口,采用同步觸發(fā)傳輸方式,并且使用直接32 位數(shù)據(jù)傳輸,數(shù)據(jù)不通過BIU ,直接寫入網(wǎng)卡FIFO ,這樣更為合理地實(shí)現(xiàn)TMS320VC5502 與LAN91C111 高速連接。

系統(tǒng)軟件設(shè)計

本系統(tǒng)的軟件包括兩大部分,一是硬件驅(qū)動程序,二是控制邏輯設(shè)計。下面分而述之。

系統(tǒng)驅(qū)動程序設(shè)計

環(huán)境下進(jìn)行的。CCS 界面簡單明了,操作方便,功能強(qiáng)大,大大降低了開發(fā)的難度。系統(tǒng)的驅(qū)動程序由TMS320VC5502 初始化程序,SAA7114A ,SAA6752HS 和LAN91C111 的配置程序、數(shù)字視頻MPEG2 碼流接收存儲封包程序、MPEG2 碼流以太網(wǎng)發(fā)送程序和系統(tǒng)主控程序等多個模塊組成。圖6 為軟件系統(tǒng)框圖。

圖6 軟件系統(tǒng)框圖

TMS32VC5502 的初始化程序完成對‘C5502 的堆棧和運(yùn)行狀態(tài)位,中斷使能位的設(shè)置,以及DSP內(nèi)核頻率的設(shè)置。SAA7114 和SAA6752HS 的配置程序通過‘C5502 的I2C 接口完成對其的設(shè)置,使其能正常地進(jìn)行模擬解碼和數(shù)字編碼。LAN91C111 的初始化程序完成對該芯片的一些寄存器設(shè)置,使其能正常運(yùn)轉(zhuǎn)起來。數(shù)字視頻MPEG2 碼流接收存儲封包程序是通過‘C5502 將SAA6752HS 傳過來的數(shù)據(jù)按照RTP 協(xié)議標(biāo)準(zhǔn)打成網(wǎng)絡(luò)上的數(shù)據(jù)包,然后再通過MPEG2碼流以太網(wǎng)發(fā)送程序?qū)?shù)據(jù)包發(fā)送出去。數(shù)據(jù)傳輸時都是使用的DMA 傳輸方式,這樣可以節(jié)省大量的時間,提高系統(tǒng)運(yùn)行的效率。

在整個驅(qū)動程序設(shè)計當(dāng)中,時序的把握是十分關(guān)鍵的。比如SAA7114 的配置程序,當(dāng)中需要用到I2C 總線,而I2C 總線對時序要求是相當(dāng)嚴(yán)格的,如果在發(fā)出START 命令之后,不加上一定的時延,而立即傳送數(shù)據(jù),由于DSP 的速度太快,可能會造成前后數(shù)據(jù)的覆蓋,導(dǎo)致程序出錯。另外,由于系統(tǒng)是進(jìn)行實(shí)時處理的,中斷程序設(shè)計是必不可少的。在程序設(shè)計時有幾個問題需要注意:

第一, 當(dāng)外部中斷信號不穩(wěn)定時,比如波形前后跳動、毛刺過多等,都有可能造成能檢測到中斷,但無法進(jìn)入中斷服務(wù)程序的情況。

第二, 若將程序單步執(zhí)行,這樣會造成仿真器出錯,無法檢測到中斷。

第三, 在修改兩個中斷矢量指針I(yè)VPD 和IVPH 之前,應(yīng)確信:

a、禁止所有的可屏蔽中斷( INTM= 1) 。這可以在修改中斷矢量指針,使之指向新中斷矢量之前,防止產(chǎn)生一個可屏蔽中斷。

b、每個硬件非屏蔽中斷對新舊IVPD 值分別有一個中斷矢量和一個中斷服務(wù)程序。這樣在修改IVPD 過程中,產(chǎn)生一個硬件非屏蔽中斷時,可以防止非法指令代碼。

FPGA 邏輯設(shè)計

該系統(tǒng)中使用了一塊Altera 公司的ACEXEP1K30QC208-3Q 型號的FPGA ,主要利用該FPGA實(shí)現(xiàn)SAA6752 與TMS320VC5502 之間的接口。如上SAA6752HS 與TMS320VC5502 的連接圖4 所示,移位寄存器負(fù)責(zé)將SAA6752HS 輸出的8 位數(shù)據(jù)方式擴(kuò)展成32 位寬度,以提高數(shù)據(jù)的吞吐效率。通過時鐘信號PDIOCLK、有效位信號PDOVAL 和音視頻標(biāo)志位PDOAV 來控制移位寄存器的工作。FIFO是一個寬度為32 位的緩沖器,TMS320VC5502 通過片選信號CE3 和讀信號ARE/SRE/SDRE 控制對FIFO 數(shù)據(jù)的讀操作。

當(dāng)SAA6752HS 采用傳送流的數(shù)據(jù)結(jié)構(gòu)時,每讀完4 個數(shù)據(jù)包(每個數(shù)據(jù)包為188個字節(jié)) , 計數(shù)器2 就會產(chǎn)生一次中斷,TMS320VC5502 從FIFO 中讀入這些數(shù)據(jù)包,完成信道編碼后向網(wǎng)絡(luò)上傳輸。FPGA 邏輯正是依據(jù)這一思想設(shè)計的。為了提升系統(tǒng)的穩(wěn)定性,避免累積錯誤,該邏輯中采用了一種雙FIFO 輪流切換的方法。在系統(tǒng)開始運(yùn)行,只往FIFO1 里寫,當(dāng)寫完4 個數(shù)據(jù)包,產(chǎn)生一次中斷,通知DSP 來讀數(shù)據(jù);接下來,系統(tǒng)自動切換到往FIFO2 里寫,此時DSP 同時在讀FIFO1里的數(shù)據(jù),直到往FIFO2 里寫完4 個數(shù)據(jù)包(由于DSP 讀數(shù)據(jù)的速度遠(yuǎn)遠(yuǎn)快于SAA6752 往FIFO 里寫數(shù)據(jù)的速度,故此時FIFO1 已被讀空) ,便又產(chǎn)生中斷;接下來,DSP 讀FIFO2 里的數(shù)據(jù),同時往FIFO1里寫,依次輪流切換。

圖7 DIO 主模式下輸出傳輸流分組的時序圖

SAA6752 的輸出采用DIO 主模式,其輸出端口的時序如圖7 所示,每個數(shù)據(jù)包包含188 個字節(jié),這是MPEG2 傳輸流分組的特性。在MAX+PLUSII 下設(shè)計其邏輯,運(yùn)行正常。

結(jié)束語

本文針對數(shù)字視頻壓縮及網(wǎng)絡(luò)傳輸作了較為深入的研究,并針對嵌入式網(wǎng)絡(luò)視頻服務(wù)器的設(shè)計和實(shí)現(xiàn)作了初步而有益的探索,其中既有經(jīng)驗(yàn)也有教訓(xùn)。由于時間及其它因素的限制,研究工作留有許多需要完善的地方。Non-PCI 結(jié)構(gòu)網(wǎng)絡(luò)接口性能的優(yōu)化和客戶端軟件的具體實(shí)現(xiàn)及形成嵌入式網(wǎng)絡(luò)視頻服務(wù)器原理樣機(jī)是我們下一步的目標(biāo)。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19160瀏覽量

229117 -

芯片

+關(guān)注

關(guān)注

453文章

50396瀏覽量

421793 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5374瀏覽量

171104

發(fā)布評論請先 登錄

相關(guān)推薦

MPEG-2壓縮編碼技術(shù)原理應(yīng)用

MPEG-2系列編碼器

怎么實(shí)現(xiàn)嵌入式MPEG-2遠(yuǎn)程網(wǎng)絡(luò)視頻監(jiān)控系統(tǒng)的設(shè)計?

分析一款不錯的基于SAA6752的MPEG-2的編碼系統(tǒng)

如何利用SAA6752HS實(shí)現(xiàn)嵌入式視頻監(jiān)控和傳輸系統(tǒng)設(shè)計?

基于MIPS體系結(jié)構(gòu)的嵌入式MPEG-2音視頻解碼設(shè)計

MPEG-2系列編碼器

5300系列MPEG-2高清模塊MediaPort

嵌入式MPEG-2遠(yuǎn)程網(wǎng)絡(luò)視頻監(jiān)控系統(tǒng)的實(shí)現(xiàn)

DiviCom多通道MPEG-2編碼器

TMS320VC5501和TMS32VC5502數(shù)字信號處理器引導(dǎo)加載程序詳細(xì)概述

基于SAA6752HS的嵌入式視頻監(jiān)控和傳輸系統(tǒng)設(shè)計

基于MPEG-2編碼芯片SAA6752實(shí)現(xiàn)應(yīng)用系統(tǒng)的設(shè)計

基于SAA6752HS芯片和TMS32VC5502實(shí)現(xiàn)MPEG-2視頻編碼系統(tǒng)的設(shè)計

基于SAA6752HS芯片和TMS32VC5502實(shí)現(xiàn)MPEG-2視頻編碼系統(tǒng)的設(shè)計

評論