一、 IRIG-B格式碼的格式與規范

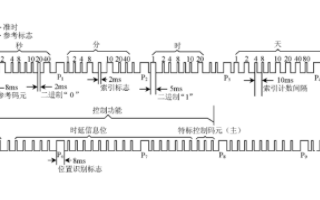

圖1為B(DC)碼示意圖。它是每秒一幀的時間串碼,每個碼元寬度為10ms,一個時幀周期包括100個碼元,為脈寬編碼。碼元的“準時”參考點是其脈沖前沿,時幀的參考標志由一個位置識別標志和相鄰的參考碼元組成,其寬度為8ms;每10個碼元有一個位置識別標志:P1,P2,P3,…,P9,P0,它們均為8ms寬度;PR為幀參考點;二進制“1”和“0”的脈寬為5ms和2ms。

圖1 B(DC)碼示意圖

一個時間格式幀從幀參考標志開始。因此連續兩個8ms寬脈沖表明秒的開始,如果從第二個8ms開始對碼元進行編碼,分別為第0,1,2,…,99個碼元。在B碼時間格式中含有天、時、分、秒,時序為秒-分-時-天,所占信息位為秒7位、分7位、時6位、天10位,其位置在P0~P5之間。P6~P0包含其他控制信息。其中“秒”信息:第1,2,3,4,6,7,8碼元;“分”信息:第10,11,12,13,15,16,17碼元;“時”信息:第20,21,22,23,25,26,27碼元;第5,14,24碼元為索引標志,寬度為2ms。時、分、秒均用BCD碼表示,低位在前,高位在后;個位在前,十位在后。

二、 B碼解碼接口卡設計方案

B碼解碼接口卡功能框圖如圖2所示。

圖2 “B碼解碼接口卡”功能框圖

對B碼進行解碼就是將B碼中所包含的時、分、秒信息提取出來,轉換成主計算機能夠識別的形式,同時以秒的準時點為參考,生成毫秒信息,一同送入主計算機中。解碼的關鍵在于檢測B碼中各個碼元的高電平寬度,首先要檢測連續兩個8ms寬的碼元出現的位置,然后再檢測隨后的30個碼元脈沖寬度,以確定時、分、秒。這里不檢測天的值,天可以直接在主計算機上設置。

圖3 B碼解碼接口卡電路

檢測高電平寬度:將B碼送入單片機89C51的INT0端,在INT0引腳由低電平變為高電平時,啟動單片機的內部定時器T0,開始計數;在INT0引腳由高變低時(即下降沿),觸發INT0中斷,讀取計數器的值,脈沖寬度等于計數值乘以計數周期。

形成毫秒值:將1kHz信號接到單片機的INT1端,每毫秒產生一次中斷。INT1中斷處理程序完成毫秒計數,當計到1000ms時完成秒加1。

三、 電路設計

1 電路設計方案1

方案1中,輸入輸出模塊由5片鎖存器構成,接口控制簡單,如圖3所示。

來自時統設備的IRIG-B(DC)碼,為RS422接口信號,經轉換后變為TTL電平,送至單片機89C51的INT0端。單片機初始化設置中,定時器T0工作在模式1,采用內部時鐘。當INT0引腳由低到高時,定時器T0開始計時;當INT0引腳由高變低時,觸發INT0中斷,執行中斷服務程序,計算INT0引腳的高電平寬度。根據寬度對B碼各脈沖進行解碼,形成秒、分、時的BCD碼,存入單片機的內部RAM中。同時,由頻率源產生的12MHz的信號經分頻器后,輸出1kHz信號,送至單片機INT1引腳,使1ms產生一次INT1中斷,執行INT1中斷處理程序,對毫秒進行計數。毫秒計數到1000時,進行秒加1,毫秒初值在B碼的準時點進行賦值。

單片機的P0口經鎖存器Ⅰ輸出地址線A0、A1,以控制兩個并行接口芯片8255的輸出端。單片機解碼和計數輸出的毫秒(2字節)、秒(1字節)、分(1字節)、時(1字節)BCD碼,在單片機的寫指令控制下,分五次送到兩片8255的不同端口。各端口經鎖存器Ⅱ“鎖存器Ⅵ,將數據鎖存。單片機送出一組時間碼后,向主計算機發送中斷。主計算機響應中斷后,依次讀取各鎖存器的值,即為當前的時統時間。

圖4 FIFO實現輸入輸出控制原理圖

鎖存器Ⅱ”Ⅵ的數據輸出端直接掛在EISA(ISA)總線上,其片選信號CS1“CS5通過地址譯碼產生。

主計算機讀時應能保證數據不處于變化中,因此,須將單片機的寫信號WR經延時反向后,送到各鎖存器的LE端,使數據被鎖存。主計算機內設一存儲單元,存放前一秒的數據。當前讀取的數據如果比前一秒多1,則認為時間正確。

為避免板內程序死循環,在該板上設計了看門狗復位電路。在單片機板內程序中,每隔一定時間對P1.6口進行置1。計時器的最高位輸出端接至單片機的Reset端。在正常情況下,P1.6口總能執行置1操作,不會對單片機復位;但若程序中有死循環,則P1.6口不被置1。當計時器計到最高位輸出端為1時,就會對單片機復位。看門狗復位電路采用14位二進制計數器4060,并具備上電復位和手動復位的功能,其振蕩周期由外接電阻、電容的大小決定。

2 電路設計方案2

方案2如圖4所示。解碼原理同方案1。該電路采用FIFO(IDT7201)加狀態寄存器和緩沖器,實現單片機與主計算機之間的數據傳輸,無需8255和鎖存器,器件較少,但相應地會增加軟件控制的工作量。單片機解碼后,在每幀數據前加上標志碼,輸出時、分、秒、毫秒信息,在寫信號的控制下,經緩沖器送入FIFO中。主計算機查詢狀態寄存器,了解FIFO的狀態(空、滿、半滿)后,讀取FIFO中的數據。這里用FIFO的8位數據線。

IDT7201為先進先出雙口存儲器。內部RAM:512×9,設有空標志(EF)、滿標志(FF)和半滿標志(HF),以避免數據溢出和空讀。讀、寫數據通過內部循環指針,無須地址信息存取數據。

IDT7201復位時,空標志(EF)置0;滿標志(FF)和半滿標志(HF)置1;讀、寫指針設到初始位置。當寫信號()由高變低時,若滿標志(FF)為1,則開始寫循環,將數據寫入RAM中,不受任何讀操作的影響;當RAM半滿時,HF置0;當寫指針比讀指針小1時,表明緩沖區已滿,FF置0,禁止寫操作。當讀信號()由低到高時,如果EF為1,則開始讀循環,數據以FIFO的方式讀出;當所有數據均讀出,讀指針等于寫指針,緩沖區已空,EF置0,禁止讀操作。在緩沖區空或滿時,、信號的外部變化,不影響FIFO。

四、 板內程序設計流程

在單片機內部RAM中,用可位尋址的21H、22H、23H、24H單元分別存放“秒”、“分”、“時”BCD碼和幀標志等,如表1所列。

表1 時間碼存放表

INT0、INTI中斷處理程序如圖5和圖6所示。

圖5 INT0中斷處理程序流程圖

圖6 INT1中斷處理程序流程圖

責任編輯:gt

-

單片機

+關注

關注

6032文章

44516瀏覽量

633026 -

計算機

+關注

關注

19文章

7421瀏覽量

87718

發布評論請先 登錄

相關推薦

兩種典型的電池供電電路的設計方案

基于CAN總線的智能接口卡的設計

基于USB的接口卡

基于EZ-USB FX單片機的無線式數據通訊接口卡的設計

使用TDS3000B DPO測試網絡接口卡

廣域網接口卡/WIC

基于PCI局部總線的1553B總線接口卡設計

B碼解碼接口卡電路的兩種設計方案的應用

B碼解碼接口卡電路的兩種設計方案的應用

評論