1引 言

列車需要傳輸大量的設(shè)備控制和旅客服務(wù)信息,隨著這些信息的數(shù)量和種類不斷地增長,迫切需要一種大容量,高速度的信息傳輸系統(tǒng)。為此,國際電工委員會(IEC)制定了一項用于規(guī)范車載設(shè)備數(shù)據(jù)通信的標(biāo)準(zhǔn)——IEC61375(列車通信網(wǎng)標(biāo)準(zhǔn)),即TCN標(biāo)準(zhǔn),該標(biāo)準(zhǔn)于1999年6月成為國際標(biāo)準(zhǔn)。目前國際上主要的TCN產(chǎn)品供應(yīng)商是德國西門子和瑞士Duagon公司,國內(nèi)的株洲電力機(jī)車研究所和大連北車集團(tuán)電力牽引研究所等單位進(jìn)行了大量的TCN相關(guān)研究工作并取得了豐碩的科研成果。

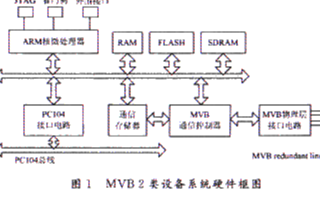

TCN標(biāo)準(zhǔn)推薦在機(jī)車上層使用絞線式列車總線WTB,在下層使用多功能車輛總線MVB。MVB總線和機(jī)車中的各種電氣設(shè)備相連,這些設(shè)備按性能可以分為5類,其中二類設(shè)備的主要特征是具有消息數(shù)據(jù)通信的功能。為了實現(xiàn)消息數(shù)據(jù)通信,需要在實時操作系統(tǒng)的支持下采用軟件編程,利用應(yīng)用程序接口API等接口來調(diào)用網(wǎng)絡(luò)協(xié)議的各種功能,從而實現(xiàn)消息數(shù)據(jù)的通信。MVB 2類設(shè)備硬件核心采用ARM7內(nèi)核微處理器NET+50作為主CPU實現(xiàn)系統(tǒng)的總體控制,采用MVBC01芯片作為MVB通信控制器實現(xiàn)鏈路層的數(shù)據(jù)處理,軟件核心采用嵌入式實時操作系統(tǒng)Nucleus Plus來實現(xiàn)任務(wù)管理、中斷管理等上層管理。

2 MVB 2類設(shè)備系統(tǒng)硬件設(shè)計

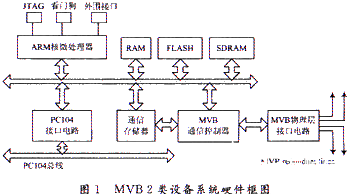

硬件系統(tǒng)設(shè)計主要包括應(yīng)用處理器模塊、通信存儲器模塊、通信控制器模塊、存儲器模塊、PC104接口模塊、物理層接口模塊等幾部分的設(shè)計,其中核心模塊是ARM處理器和MVB通信控制器MVBC01。系統(tǒng)硬件設(shè)計框圖如圖1所示。

系統(tǒng)硬件各部分電路的功能和設(shè)計方法如下:

2.1 應(yīng)用處理器模塊

應(yīng)用處理器采用ARM核微處理器NET+50作為核心處理器。NET十50由Netsilicon公司生產(chǎn),屬于ARM7系列。

[table][/table]NET+50處理器包括一個ARM7TDMI核,32位內(nèi)部總線,支持所有SRAM,SDRAM,F(xiàn)LASH,E2PROM,有40個可編程I/O接口引腳,16個輸入接口引腳,36個可編程中斷,2個完全獨立的HDLC/UART/SPI串行口以及完整的以太網(wǎng)控制器。

2.2 存儲器模塊

存儲器模塊為ARM處理器NET+50正常工作時提供所需的程序存貯空間,內(nèi)存空間和數(shù)據(jù)存儲空間。NET+50集成了內(nèi)存控制器模塊(Memory Controller Mod-ule),為存儲設(shè)備提供無縫連接,系統(tǒng)通過配置內(nèi)存控制器模塊的控制寄存器和片選CS控制寄存器來實現(xiàn)訪問相應(yīng)存儲器的信號和邏輯。

本設(shè)計中選用大小為16 MB的高速SDRAM為系統(tǒng)提供內(nèi)存服務(wù),選用大小為512 kB的NVRAM為系統(tǒng)提供數(shù)據(jù)存儲空間,選用大小為4 MB的FLASH為系統(tǒng)提供程序存儲空間。使用ARM處理器的地址線、數(shù)據(jù)線以及相應(yīng)的片選、讀/寫、時鐘線完成對存儲器的尋址。

2.3 通信控制器模塊

通信控制器MVBC是MVB總線上的新一代核心處理器,他獨立于物理層和功能設(shè)備,為在總線上的各個設(shè)備提供通訊接口和通訊服務(wù),可通過配置應(yīng)用在符合TCN標(biāo)準(zhǔn)的1,2,3,4類設(shè)備中。MVBC把來自于MVB總線的串行化信號轉(zhuǎn)換為并行的數(shù)據(jù)字節(jié),也把需發(fā)送的字節(jié)交由串行化電路發(fā)送到傳輸介質(zhì)上。MVBC可實現(xiàn)數(shù)據(jù)鏈路層以及一部分傳輸層的數(shù)據(jù)處理,并通過通訊存儲器來與上層軟件交互。

本系統(tǒng)中MVB通信控制器采用MVBC01 ASIC專用芯片,符合IEC61375-1國際標(biāo)準(zhǔn)。MVBC01專用芯片采用16位數(shù)據(jù)總線,提供了豐富的接口控制信號,簡化了與各種宿主CPU以及通信存儲器的接口設(shè)計,支持MVB協(xié)議中鏈路層及以下的功能。

2.4 通信存儲器模塊

通信存儲器地址空間保存MVBC01的所有數(shù)據(jù)和信息,既可以被MVBC01訪問又可以被ARM處理器訪問。本系統(tǒng)中采用兩片512 kB大小的SRAM cy62148擴(kuò)展成1 MB的尋址空間。通信存儲器的尋址空間劃分為4部分,分別為Logical AddreSS Space(LA),Device AddressSpace(DA),Service Area(1 kB)和Miscellany。

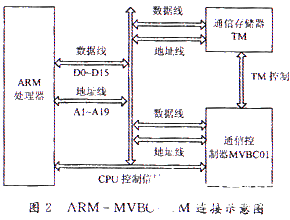

通信存儲器分別通過數(shù)據(jù)線,地址線和ARM處理器以及MVBC01相連,從而實現(xiàn)數(shù)據(jù)交換和地址尋址,ARM處理器、MVBC01和通信存儲器的連接示意圖如圖2所示。

MVBC01內(nèi)部集成Traffic Memory Controller(TMC)模塊,負(fù)責(zé)控制通信存儲器的訪問模式,TMC與仲裁控制器和邏輯地址密切相關(guān)。TMC模塊負(fù)責(zé)控制3種存儲器訪問模式,分別是:ARM CPU訪問通信存儲器;ARM CPU訪問MVBC內(nèi)部寄存器;MVBC01訪問通信存儲器。TMC模塊還對ARM處理器和MVBC同時訪問通信存儲器所產(chǎn)生的訪問沖突做出仲裁。

2.5 MVB物理層接口電路模塊

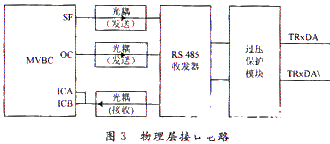

物理層接口電路模塊的設(shè)計如圖3所示。物理層接口采用電氣短距離介質(zhì)ESD+接口,系統(tǒng)信號通道使用光耦實現(xiàn)主系統(tǒng)與外界得電隔離以提高系統(tǒng)可靠性,使用RS 485芯片作為收發(fā)器,并使用過壓保護(hù)模塊來防止瞬問過壓對器件的損壞。

圖3所示的MVBC端口ICA(MVB Input Data Chan-nel A)和ICB(MVB Input Data Channel B)分別為MVB輸入數(shù)據(jù)通道A和輸入數(shù)據(jù)通道B,來自物理層收發(fā)器的MVB信號由此端口送入MVB通信控制器MVBC01中;MVBC端口OC(MVB Output Data Channel)是MVB數(shù)據(jù)輸出端口,數(shù)據(jù)經(jīng)由此端口將發(fā)送至物理層收發(fā)器;MVBC端口SF(Send Frame)為輸出端口,輸出信號可作為物理層的使能信號,該信號有效時表示一個報文正在通過MVBC端口OC(MVB Output Data Channel)輸出。

2.6 其他

在MVB設(shè)備正常運行時,可以通過RS 485/RS 232通信接口進(jìn)行程序的監(jiān)控和調(diào)試。系統(tǒng)可以通過跳線選擇RS 485/RS 232接口是工作在RS 485還是RS 232下。

其他還有諸如看門狗、JTAG接口、時鐘、電源、PC104接口等模塊,本文不再詳述。

3 系統(tǒng)軟件設(shè)計

3.1 系統(tǒng)軟件體系結(jié)構(gòu)

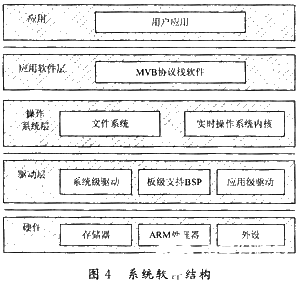

MVB 2類設(shè)備軟件體系采用典型的嵌入式軟件體系結(jié)構(gòu),包括驅(qū)動層、操作系統(tǒng)層、應(yīng)用軟件層,其中操作系統(tǒng)層是軟件體系的核心。系統(tǒng)的軟件結(jié)構(gòu)如圖4所示。

系統(tǒng)軟件結(jié)構(gòu)各部分功能如下:

3.1.1 驅(qū)動層

驅(qū)動層是直接和硬件相聯(lián)系的一層,他對操作系統(tǒng)和應(yīng)用提供所需的驅(qū)動支持。該層主要包括3種類型的程序:板級支持BSP、系統(tǒng)級驅(qū)動和應(yīng)用級驅(qū)動。

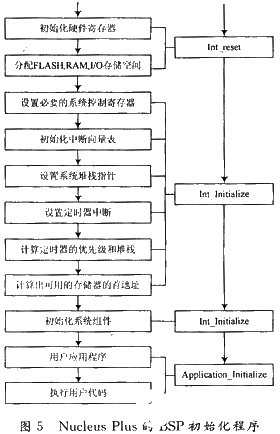

板級支持BSP 在用戶的應(yīng)用程序啟動之前,完成對系統(tǒng)的初始化必須有專門的一段啟動代碼,即板級支持BSP。板級支持BSP介于物理硬件和實時操作系統(tǒng)之間,在系統(tǒng)上電后,初始化系統(tǒng)的硬件環(huán)境,包括初始化ARM處理器、初始化中斷控制器、初始化存儲器、初始化堆棧等。NucleusPlus操作系統(tǒng)的BSP初始化程序流程如圖5所示。

系統(tǒng)級驅(qū)動 與系統(tǒng)軟件相關(guān)的驅(qū)動,這類驅(qū)動是操作系統(tǒng)和中間件等系統(tǒng)軟件所需的驅(qū)動程序,他們的開發(fā)要按照系統(tǒng)軟件的要求進(jìn)行。

應(yīng)用級驅(qū)動 與應(yīng)用程序相關(guān)的驅(qū)動,和操作系統(tǒng)無關(guān),由應(yīng)用決定。

3.1.2 操作系統(tǒng)層

操作系統(tǒng)層足嵌入式軟件的核心,是系統(tǒng)的軟件支持平臺。主要包括實時操作系統(tǒng)內(nèi)核、文件系統(tǒng)、電源管理、嵌入式GUI系統(tǒng)、嵌入式網(wǎng)絡(luò)系統(tǒng)。其中嵌入式內(nèi)核是基礎(chǔ)和必備的部分,主要完成任務(wù)調(diào)度、內(nèi)存管理、任務(wù)間通信、任務(wù)的同步與互斥、中斷管理、定時器等功能。本系統(tǒng)采用Nucleus Plus嵌入式操作系統(tǒng),能完全滿足MVB對于實時性、可靠性、完整性和有效性的要求。NucleusPlus采用了軟件組件的方法,每個組件具有單一而明確的目的,包括任務(wù)控制管理、內(nèi)存控制管理、定時器管理、中斷、系統(tǒng)診斷、I/O驅(qū)動管理等16個組件。

3.1.3 應(yīng)用軟件層

應(yīng)用軟件層主要由多個相對獨立的應(yīng)用任務(wù)組成,每個應(yīng)用完成一個特定的工作,這里主要包括MVB協(xié)議棧軟件。MVB協(xié)議棧軟件在實時操作系統(tǒng)內(nèi)核的支持下,通過MVB驅(qū)動模塊完成MVB網(wǎng)絡(luò)數(shù)據(jù)通信任務(wù)。用戶應(yīng)用可以利用MVB協(xié)議棧的接口函數(shù)訪問需要的數(shù)據(jù)集,并利用收到或者發(fā)送的數(shù)據(jù)進(jìn)行相應(yīng)的控制或其他數(shù)據(jù)處理工作。

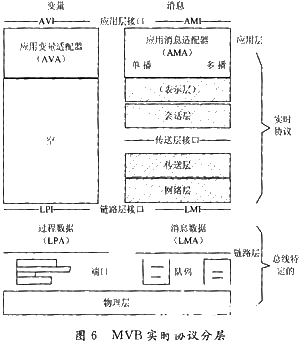

3.2 實時協(xié)議

每個網(wǎng)絡(luò)都要有與之相應(yīng)的網(wǎng)絡(luò)軟件在其上運行,這些軟件被稱為協(xié)議。在互聯(lián)網(wǎng)上運行的協(xié)議我們稱之為TCP/IP協(xié)議,在列車通信網(wǎng)上運行的類似TCP/IP的協(xié)議我們稱之為實時協(xié)議(Real Time Protocol,RTP),實時協(xié)議為一個應(yīng)用與另一個應(yīng)用在列車通信網(wǎng)上的通信提供協(xié)議和服務(wù)。

實時協(xié)議分層結(jié)構(gòu)如圖6所示。由圖中的分層結(jié)構(gòu)可知MVB實時協(xié)議包括過程變量通訊和消息數(shù)據(jù)通訊兩部分。由圖可知變量的協(xié)議和服務(wù)包括過程數(shù)據(jù)鏈路層接口(LPI)和變量的應(yīng)用層接口(AVI)。消息協(xié)議和服務(wù)包括消息數(shù)據(jù)鏈路層接口(LMI)、網(wǎng)絡(luò)層、傳送層、會話層、應(yīng)用層接口(AMI)。其中鏈路層接口又稱為低層接口,他規(guī)定來自總線的服務(wù),應(yīng)用層接口又稱為高層接口,他規(guī)定提供給應(yīng)用的應(yīng)用層接口。

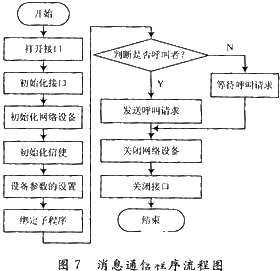

3.3 消息通信機(jī)制及其實現(xiàn)

MVB 2類設(shè)備的主要特征是實現(xiàn)消息數(shù)據(jù)的發(fā)送和接收。消息通信中實時協(xié)議是由信使執(zhí)行的,他是作為獨立的進(jìn)程與應(yīng)用并行運行。實時協(xié)議的網(wǎng)絡(luò)層、傳輸層、會話層、表示層是由信使來執(zhí)行并實現(xiàn)的,信使與應(yīng)用層有一個消息應(yīng)用層接口(AMI),通過這個接口應(yīng)用可以調(diào)用信使的服務(wù)。同時信使與鏈路層也有一個接口:消息鏈路層接口(LMI),鏈路層通過這個接口向信使提供服務(wù)。在編程實現(xiàn)消息通信時,只需要使用消息應(yīng)用層接口。

用戶開發(fā)程序來實現(xiàn)消息通信,就是使用消息應(yīng)用層接口中的接口函數(shù)來調(diào)用信使的各項功能,實現(xiàn)消息通信的應(yīng)用程序就是按照這個順序編寫和執(zhí)行的。消息數(shù)據(jù)的實現(xiàn)程序的流程如圖7所示。

4 結(jié) 語

使用符合TCN標(biāo)準(zhǔn)的產(chǎn)品是開發(fā)下一代新式列車的重要發(fā)展趨勢,本文通過對IEC61375-1列車通訊網(wǎng)絡(luò)標(biāo)準(zhǔn)的研究,提出了MVB 2類設(shè)備軟硬件的設(shè)計方案并完成了系統(tǒng)硬件各功能模塊設(shè)計和上層軟件的部分設(shè)計,對MVB實時協(xié)議RTP和消息通信的機(jī)制也做了深入的研究,并給出了消息通信的編程實現(xiàn)方法。通過對基于ARM處理器的MVB 2類設(shè)備的深入研究和功能設(shè)計實現(xiàn),不但為以后開發(fā)更高類別的MVB設(shè)備積累了經(jīng)驗,而且為進(jìn)一步自主開發(fā)其他符合TCN標(biāo)準(zhǔn)的MVB產(chǎn)品提供了借鑒。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19178瀏覽量

229200 -

控制器

+關(guān)注

關(guān)注

112文章

16214瀏覽量

177479 -

存儲器

+關(guān)注

關(guān)注

38文章

7455瀏覽量

163623

發(fā)布評論請先 登錄

相關(guān)推薦

詳解微處理器和微控制器區(qū)別

【轉(zhuǎn)帖】詳解微處理器和微控制器區(qū)別

處理器及微處理器系統(tǒng)

嵌入式微處理器如何選擇

dsp芯片和通用微處理器有什么區(qū)別

什么是總線微處理器

ARM微處理器介紹

ARM微處理器的應(yīng)用領(lǐng)域及其特點

基于S3C44B0X微處理器的JFFS2件系統(tǒng)的實現(xiàn)

采用NET+50和MVBC01芯片實現(xiàn)MVB 2類設(shè)備系統(tǒng)的設(shè)計

基于微處理器NET+50和MVBC01芯片實現(xiàn)MVB 2類設(shè)備系統(tǒng)的設(shè)計

基于微處理器NET+50和MVBC01芯片實現(xiàn)MVB 2類設(shè)備系統(tǒng)的設(shè)計

評論