時鐘技術在現代科學技術中有著廣泛的應用。計量測試系統需要高精度的參考源,通信系統需要高精度的同步時鐘作參考,以此來協調全網所有基站的工作。傳統時鐘源的內外頻標切換是用檢波器對外頻標進行檢波,用檢波出來的信號去控制晶振的電源通斷,從而實現切換。但這種傳統的檢波方式,只能對頻標的有無進檢波,無法檢出參考的頻率,而且要求內外頻標的頻率相等,因此,存在硬件電路復雜,需要外部控制,成本高等缺點。

本文設計的自適應式時鐘源的內外頻標切換采用軟件檢測和控制來適應5 MHz,10 MHz和20 MHz頻標,通過改變芯片內部寄存器的頻率控制字,改變參考頻率的倍頻次數,最終得到所需頻率的時鐘。時鐘源采用目前應用最為廣泛的一種頻率合成方法中的鎖相技術,具有低雜散、低相噪、輸出帶寬較寬的特點。與傳統的內外頻標切換時鐘源相比,內外頻標切換可以不用外部控制,達到完全自適應多個不同頻率外頻標,并且可以省去檢波、繼電器切換電路,具有硬件電路簡單,成本低等優點。

1 自適應式時鐘源內外頻標的切換原理

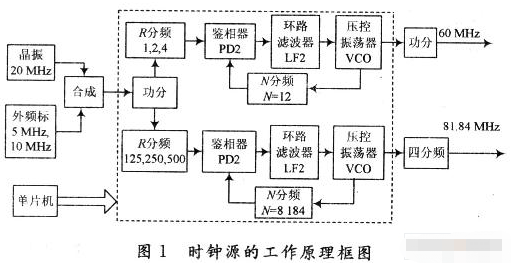

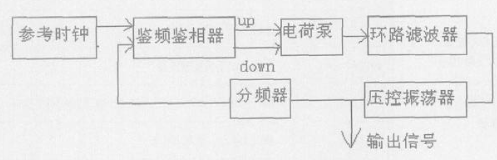

圖1給出的鎖相時鐘源是單片機通過串行數字接口對鎖相芯片內部的分頻器進行設置,將需要的頻率N次分頻作為一路鑒相輸入;將參考信號進行R次分頻,作為另一路鑒相輸入,通過鑒相器后得到反映兩路鑒相信號誤差的控制電壓,經過低通濾波器后,取出其中緩慢變化的直流電壓分量,用來控制壓控元件電容量的變化,將VCO的輸出頻率拉回到穩定值上來,環路鎖定。

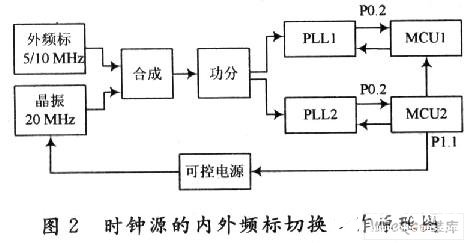

時鐘源的內外頻標切換主要由軟件來實現。圖2中單片機的P1.1口用來控制內部晶振加電,P0.2口用來檢測環路鎖定指示。當外加頻標時,單片機通過串行數據口,給鎖相環芯片送入5 MHz參考的頻率控制字,延時等待,檢測鎖定指示電平為高,則環路鎖定在5 MHz頻標上,單片機停止送數,降單片機的內部時鐘,來避免單片機帶給環路的干擾;如果鎖定指示為低,單片機繼續送10 MHz參考的頻率控制字,延時等待,如果檢測鎖定指示電平為高,則環路鎖定在10 MHz頻標上,單片機停止送數,降單片機的內部時鐘;如果鎖定指示為低,單片機將通過P1.1口的高電平,控制穩壓塊LT1762,給內部的20 MHz晶振加電,然后單片機送20 MHz參考的頻率控制字,最終環路鎖定。如果內外頻標同時外加,鎖定指示電平高低發生跳變,環路處于失鎖狀態,單片機隨即切斷內頻標電源,環路重新鎖定在外頻標上。

傳統的內外頻標切換時鐘源的內外頻標頻率是相同的,而自適應式時鐘源內外頻標頻率不同,外頻標還可以有幾種不同頻率的選擇。因此,該時鐘源在整機使用中對外部頻標的要求大大降低,內部的恒溫晶振也保證了在沒有外頻標情況下,時鐘源仍然能正常工作,增加了在整機系統使用中的兼容性。軟件的實時監測又可以保證在內外頻標同時存在的情況下,及時切斷內部晶振的電源,避免兩種不同的參考頻率,對環路帶來不必要的干擾。所以改進后的自適應時鐘源從產品的適應性和使用的方便性都大大增強。

在調試中發現,若外頻標為方波,上升沿比較陡,對頻標的電平要求不高,大于0 dBm即可;若外頻標為正弦波,上升沿不夠陡,因此如果環路預先鎖定在內頻標上,再加外頻標,外頻標的信號需強于內頻標,環路才能重新鎖在外頻標上。所以,外頻標為正弦波的時侯,電平必須大于5 dBm,環路才能在內外頻標間自適應切換。

2 自適應內外頻標切換時鐘源的設計與實現

2.1 自適應式時鐘源的內外頻標切換軟件的設計

該時鐘源軟件的流程如圖3所示。

2.2 自適應式時鐘源的環路濾波器的設計

環路濾波器的設計在整個時鐘源中很關鍵,既要兼顧5 MHz,10 MHz外頻標,又要兼顧20 MHz內頻標。因此,環路的設計必須同時考慮到各個頻標的因素。鑒于這種情況,設計環路時,對參考頻率分別進行1,2,4分頻,使得環路在多個頻標下,均以5 MHz鑒相頻率,相同的N分頻次數,滿足鎖相環的要求。所以,對環路帶寬必須合理選擇。一般情況下,選擇在參考源噪聲源和VCO噪聲源譜密度線的交叉點。

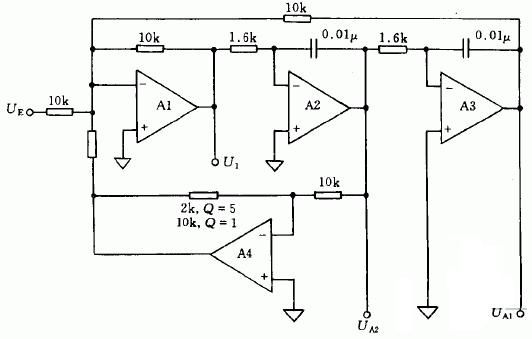

在設計中采用無源三階濾波器,環路帶寬大致設為45 kHz,相位裕量為65°。環路帶內的相位噪聲取決于晶振相位噪聲,環路帶外的噪聲取決于壓控振蕩器的相位噪聲。時鐘源輸出信號的相位噪聲是所有噪聲同時作用的結果。圖4為鎖相環附加噪聲源的系統框圖。

數字鎖相環在鎖定狀態下可以認為是線性系統,應用線性疊加原理,將各噪聲源反映到時鐘源輸出端的相位噪聲功率譜密度相加,則可得到總的相位噪聲功率譜密度(單位:dBc/Hz):

其中:Sr(f),SPD(f),SLP(f),SVCO(f),So。(f)分別為參考頻標、鑒相器、環路濾波器、VCO、時鐘源輸出的相位噪聲,單位均為dBc/Hz,H(j2πF)為環路的有效傳輸函數。上式右邊第一項為環路的低通輸出相位噪聲譜,第二項為環路的高通輸出相位噪聲譜。

參考信號的相位噪聲對輸出信號相噪的貢獻L1(f)(單位:dBc/Hz),可用式(1)計算:

式中:Lr(f)為晶振的相位噪聲(單位:dBc/Hz);鑒相器的基底相噪對輸出信號相噪的貢獻L2(f)(單位:dBc/Hz),可用式(2)來計算:

式中:LpD(f)為鑒相器的基底相噪(單位:dBc/Hz);Fc為鑒相頻率(單位:Hz)。

由式(1)和式(2)得,在環路帶內輸出信號的相位噪聲L(f)(單位:dBc/Hz),可由式(3)得到:

利用式(3)可估算出輸出信號的相位噪聲為-120 dBc/Hz@1 kHz。

由于參考頻率的不同,R分頻的次數不同,相位噪聲改善的不同,加之N倍頻相位噪聲惡化的差異性,最終環路在各頻標作用下,表現出來的相位噪聲也各有差異,不盡相同。

3 實驗結果及其分析

實驗結果證明,三種參考頻率在相同的相位噪聲基準下,20 MHz頻標倍頻次數最少,相位噪聲曲線最好;5 MHz頻標倍頻次數最多,相位噪聲也能滿足要求。圖5給出了E4440A測試的時鐘源輸出相位噪聲曲線(其橫坐標表示頻率,縱坐標表示相位噪聲)。

從圖5可以看出,時鐘源實際輸出相位噪聲與根據上述公式估算的結果比較接近,滿足系統對時鐘源相位噪聲的要求,這說明本文提出的內外頻標自適應式時鐘源的環路帶寬設計合理,電路布局優化,設計方法是完全可行的。

4 結 語

新設計的內外頻標自適應式時鐘源具有電路硬件結構簡單,成本低,相位噪聲低,雜散小的特點。內外頻標的切換不用外部控制,完全自適應多個不同頻率的內外頻標,而且產品的適應性和使用的方便性都大大增強。目前該時鐘源已在數字基帶系統中得到廣泛應用。

責任編輯:gt

-

單片機

+關注

關注

6032文章

44525瀏覽量

633264 -

濾波器

+關注

關注

160文章

7749瀏覽量

177737 -

分頻器

+關注

關注

43文章

447瀏覽量

49820

發布評論請先 登錄

相關推薦

改進的變階數LMS自適應濾波算法

自適應Notch濾波器的FPGA實現

基于單片機和無源三階濾波器實現自適應式時鐘源的應用方案

基于單片機和無源三階濾波器實現自適應式時鐘源的應用方案

評論