0 引言

隨著工藝的進步以及深亞微米集成電路技術的不斷發展,芯片的集成度越來越高,芯片的規模也越來越大。在無線通信、圖像處理等各個芯片應用領域,越來越多的系統芯片(SoC)選擇將各個功能不同的模擬電路模塊和數字電路模塊集成在同一芯片中,以便在整個系統的性能達到最優的同時使成本降到最低。但這卻給芯片的測試帶來了意想不到的困難,也使得測試成本大為增加。ADC作為連接數字系統和模擬系統的橋梁,其測試顯得格外重要。隨著ADC性能的不斷提高,芯片外部環境也已經成為ADC測試的主要障礙。

為了解決上述問題,同時更準確地測試ADC作為IP核集成到SoC中工作時的真實性能,各種ADC的內建自測試(Built-In-Self Test)方法應運而生,而如何精確而高效地為ADC內建自測試提供測試激勵是一個非常關鍵的問題。本文提出一種可用于ADC片上測試的三角波信號發生器的實現方法,產生的三角波具有非常好的線性度,可以滿足14 b高精度ADC的測試要求。整個設計采用UMC 0.18 μm CMOS工藝實現,電源電壓為1.8 V。

1 三角波信號發生器的設計約束

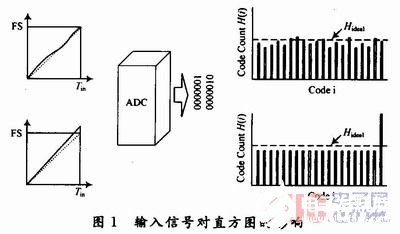

碼密度直方圖測試法基于統計學,用該法對ADC的靜態特性進行測試時所加的測試激勵必須盡量接近理想,在本文中也就是要盡量獲得精準的三角波。如果獲得的三角波信號存在非線性或增益誤差,則用該信號去測試一個理想的ADC,測得的碼元的直方圖分布就會不均勻(如圖1所示),這種不均勻來自測試激勵本身的誤差,所以由此測得的ADC的積分非線性(INL)和微分非線性(DNL)就引入了誤差。

這樣一來,測試結果的精確性很大程度上取決于所加三角波信號的精確度。所以,在設計三角波發生器時,必須根據被測ADC的性能指標來確定所需要的三角波發生器的線性度以及幅度。本文所設計的三角波信號發生器要滿足精度為14 b的ADC的測試要求,那么其精度要求必須不低于16 b。

2 三角波信號發生器的原理

產生三角波信號的原理是用一個恒定不變的正向電流對電容進行充電得到一個均勻上升的斜波電壓,當電壓上升到一定值時再用一個恒定不變的負向電流對電容放電,從而得到一個均勻下降的斜波電壓,交替用正負方向的電流對電容進行充放電,就可以得到連續的三角波電壓信號,上升和下降的斜率由正負向電流與電容的比值I/C決定。為了滿足ADC測試的要求,三角波信號應具有較好的線性度,同時也要保證較低的斜率,這就需要一個精確的小電流和一個較大的電容。

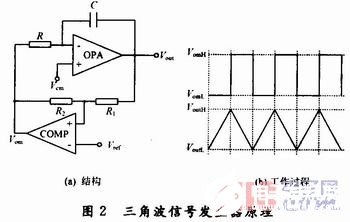

圖2描述了三角波信號發生器的原理。圖中運算放大器、電阻R、電容C組成一個方波積分器;比較器、電阻R1、電阻R2組成一個遲滯比較器作為一個反饋控制電路。電路的工作過程如下:

(1)當比較器輸出電平為低電平VomL時,電容C處于充電狀態,Vout不斷上升,當Vout的值上升到使得比較器正相輸入端電壓高于Vref時,比較器輸出翻轉,輸出高電平VomH,同時電流方向改變,電容C進入放電狀態;

(2)當比較器輸出電平為高電平VomH時,電容C處于放電狀態,Vout不斷下降,當Vout的值下降到使得比較器正相輸入端電壓低于Vref時,比較器輸出翻轉,輸出低電平VomL,同時電流方向也翻轉,電容C進入充電狀態;

(3)如此循環振蕩,便產生了周期的連續三角波電壓信號。

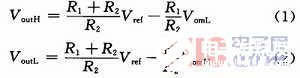

輸出三角波電壓信號Vout的閾值電壓為:

式中:Vref為比較器負端參考電壓;VomH,VomL分別為比較器輸出的高、低電平。

由以上公式可知,周期T由RC常數、峰峰值Vout.pp以及比較器輸出的高低電平VomH,VomL決定。

3 具體電路設計實現

3.1 運算放大器設計

運算放大器是整個電路結構中的關鍵部分,它直接決定了三角波信號發生器的線性度和線性輸出范圍。運算放大器與電阻R、電容C構成積分電路,其主要作用是使積分電容C一端電平保持穩定,這就要求運放具有較高的增益;同時,為了使三角波信號發生器的線性輸出范圍盡可能大,要求運放具有較大的輸出擺幅。

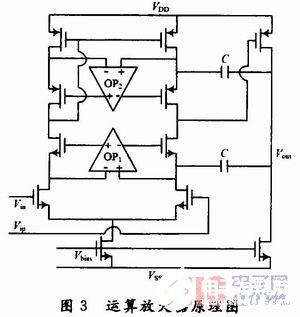

本文中運算放大器采用兩級結構,如圖3所示。其中:輸入級采用帶增益自舉電路的套筒式共源共柵結構,包括主運放和輔助運放。主運放采用NMOS輸入的套筒式共源共柵結構,具有高增益、低功耗以及良好的頻率特性。輔助運放OP1,OP2分別為采用PMOS輸入和NMOS輸入的折疊式共源共柵全差分結構,進一步提高運放增益。

第二級采用共源結構來改善套筒式共源共柵結構輸出擺幅小的缺點,同時也能一定程度上提高運算放大器的開環增益。由于級數增加也會引入新的零極點,從而會影響運放的穩定性。所以,必須加入補償電容C,使相位裕度滿足要求。

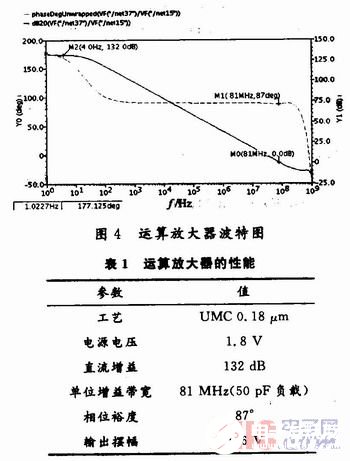

由Spectre仿真所得的運算放大器的交流幅頻、相頻特性如圖4所示。表1總結了運算放大器的基本性能參數。

3.2 遲滯比較器設計

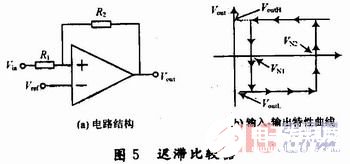

遲滯比較器的遲滯特性是比較器中引入正反饋的結果。遲滯比較器有兩個輸入閾值,當輸入電壓經過其中一個閾值時輸出電壓會改變,同時輸入閾值會跳變到另一個值。要再次改變輸出,輸入必須到達跳變之后的閾值,在輸出改變的同時,閾值又會跳變回原來的值。本文所采用的遲滯比較器電路及輸入-輸出特性曲線如圖5所示。

兩個輸入閾值分別為:

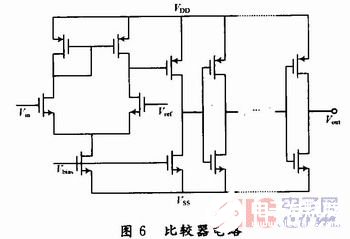

遲滯比較器中的比較器電路采用兩級開環運放實現,由于比較器后級是一個2 mΩ的電阻,所以必須使比較器輸出級電阻足夠低,以防止由于電阻分壓而導致比較器輸出電壓達不到電源電壓以及地電壓。因此,在兩級開環運放之后增加了一個大寬長比的反相器鏈以獲得較低的輸出電阻,如圖6所示。

4 仿真結果

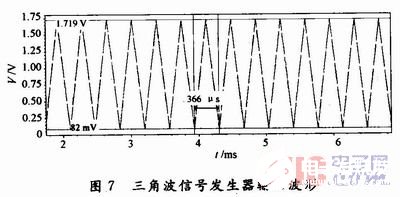

對該三角波信號發生器整體電路進行晶體管級仿真,仿真得到的三角波電壓信號范圍為82 mV~1.719 V,周期為366μs,如圖7所示。

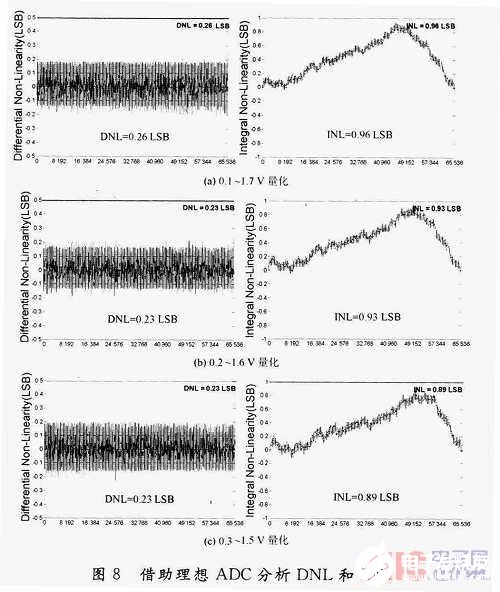

對該三角波信號進行多個周期的采樣,利用16 b理想ADC分別對0.1~1.7 V,0.2~O.6 V,0.3~1. 5 V這三個不網的電壓范圍進行量化轉換,并做相應的碼密度直方圖分析,得到各自的DNL和INL,如圖8所示。從圖8中可以看到,對于16 b理想ADC的量化,這三種不同的電壓范圍INL都在1 LSB以下(等價于INL《24μV),可以滿足14 b ADC靜態特性的測試。

5 結語

本文設計了一款應用于高精度ADC片上測試的高精度高線性度模擬三角波信號發生器,可為高達14 b的ADC靜態參數片上測試提供有效的激勵。仿真結果表明,該信號發生器所生成的三角波電壓信號范圍為82 mV~1.719 V,周期為366μs,INL《24 μV,等效精度達到16b以上,其幅值和頻率可根據具體的設計要求進行調節,而且其線性度表現良好,可滿足14 b高精度ADC靜態參數的測試需求。

編輯:jq

-

芯片

+關注

關注

454文章

50460瀏覽量

421971 -

adc

+關注

關注

98文章

6452瀏覽量

544147 -

soc

+關注

關注

38文章

4124瀏覽量

217966 -

信號發生器

+關注

關注

28文章

1456瀏覽量

108662

發布評論請先 登錄

相關推薦

一種用于高精度ADC片上測試的信號發生器

一種用于高精度ADC片上測試的信號發生器

評論