基于SRAM結構的FPGA容量大,可重復操作,應用相當廣泛;但其結構類似于SRAM,掉電后數(shù)據(jù)丟失,因此每次上電時都需重新加載。

目前實現(xiàn)加載的方法通常有兩種:一種是用專用Cable通過JTAG口進行數(shù)據(jù)加載,另一種是外掛與該FPGA廠商配套的PROM芯片。前者需要在PC機上運行專用的加載軟件,直接下載到FPGA片內(nèi),所以掉電數(shù)據(jù)仍然會丟失,只適用于FPGA調(diào)試階段而不能應用于工業(yè)現(xiàn)場的數(shù)據(jù)加載。

后者雖然可以解決數(shù)據(jù)丟失問題,但這種專用芯片成本較高,供貨周期也較長(一般大于2個月),使FPGA產(chǎn)品的開發(fā)時間受到很大約束。因此希望找到一種更簡便實用的FPGA芯片數(shù)據(jù)加載方法。根據(jù)FPGA芯片加載時序分析,本文提出了采用通過市面上常見的Flash ROM芯片替代專用PROM的方式,通過DSP的外部高速總線進行FPGA加載;既節(jié)約了系統(tǒng)成本,也能達到FPGA上電迅速加載的目的;特別適用于在FPGA調(diào)試后期,待固化程序的階段。下面以兩片Xilinx公司Virtex-4系列XC4VLX60芯片為例,詳細介紹采用TI公司的TMS320C61416DSP控制FPGA芯片數(shù)據(jù)加載的軟硬件設計。

1 Xilinx FPGA配置原理

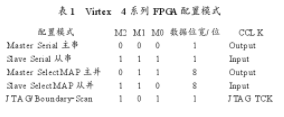

Virtex-4系列的FPGA芯片外部配置引腳MODE PIN(M0、M1、M2),有5種配置模式,如表1所列。

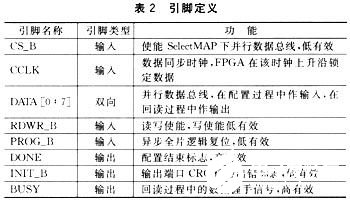

FPGA在Slave SelectMAP方式下,共用了表2所列的15個配置引腳。

1.1 配置流程

FPGA加載時序如圖1所示。各配置信號必須滿足其時序關系,否則配置工作無法正常完成。

圖1中,Slave SelelctMAP加載主要包括以下3個步驟:

①啟動和初始化。FPGA上電正常后,通過PROG_B引腳低脈沖進行FPGA異步復位,使得FPGA內(nèi)部邏輯清零。其次PROG_B上拉高,停止外部復位,INIT_B引腳會在TPOR時間段內(nèi)自動產(chǎn)生一個由低到高的跳變,指示FPGA內(nèi)部初始化完成,可以進行數(shù)據(jù)下載;同時FPGA在INIT_B的上升沿采樣其模式引腳MODE PIN,決定其模式配置。

②比特流加載。INIT_B信號變高后,不需要額外的等待時間,Virtex器件就可以立即開始數(shù)據(jù)的配置。比特流數(shù)據(jù)在外部CCLK信號上升沿按字節(jié)方式置入。該過程包括同步初始化字、器件ID號校驗、加載配置數(shù)據(jù)幀、CRC校驗4個部分。

③STARTUP啟動。在成功校驗CRC碼位后,比特流命令使得FPGA進入STARTUP狀態(tài)。它是由8相狀態(tài)機實現(xiàn)的。中間包括等待DCM鎖相、DCI匹配等幾個狀態(tài),最后FPGA釋放外部DONE引腳,對外輸出高阻態(tài),由外部上拉高,指示FPGA加載成功。

1.2 文件生成

ISE生成數(shù)據(jù)文件主要有3種:BIT文件,由二進制格式進行表征邏輯設計,包括文件頭和配置數(shù)據(jù),主要用于JTAG下載電纜模式;MCS文件,為外部PROM燒寫生成的下載文件,ASCII碼,與前者不同的是它含有在PROM中的數(shù)據(jù)地址和校驗值;BIN文件格式,由二進制表示,完全由配置數(shù)據(jù)組成,不需要作其他的提取和進制轉換,只是配置前的Byte-Swapped是在CPLD中實現(xiàn)的。本設計采用的是BIN文件格式。

2 硬件實現(xiàn)

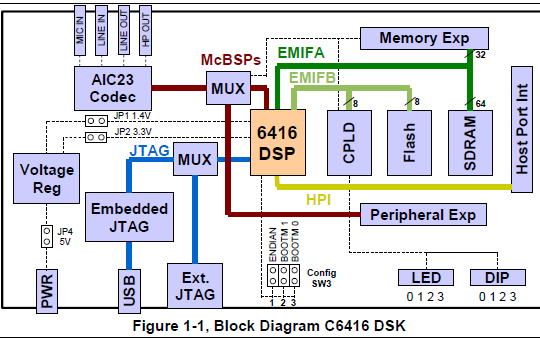

系統(tǒng)采用2片Xilinx Virtex-4系列的600萬門的FPGA XC4VLX60。主MCU是TI公司高性能定點處理器TMS320C6416,對外有2個EMIF總線接口,分別是64位寬EMIFA和16位寬EMIFB。EMIFB上掛有8位8MB的Flash和16位CPLD:Flash做2片F(xiàn)PGA的BIN文件保存,之前由仿真器燒寫;CPLD用于2片F(xiàn)PGA地址譯碼和DSP與FPGA配置部分的邏輯接口。整個數(shù)據(jù)流程是在DSP上電啟動后,Bootloader自行引導用戶程序運行。該程序負責由EMIFB總線搬移Flash空間中BIN文件,通過CPLD分別對2片F(xiàn)PGA進行配置加載。硬件系統(tǒng)拓撲圖如圖2所示。

3 軟件設計

軟件包括3部分:引導Bootloader代碼,加載FPGA用戶程序以及接口部分的CPLD Verilog代碼。

3.1 DSP Bootloader

本系統(tǒng)中目標板處于FPGA調(diào)試后期,需要固化其加載程序。整板上電后,要求脫離仿真器自行加載FPGA,因此這里采用DSP的EMIF BooT方式。它是由DSP上電復位后,以默認ROM時序通過EDMA自行搬移BCE1的ROM空間前1 KB內(nèi)容到片內(nèi),在其0x0地址開始運行。

一般由C編寫的程序代碼長度都遠大于1 KB,如果只是純粹由DSP搬移Flash前1 KB空間,這樣便會丟失數(shù)據(jù),程序無法正常運行。這里采用由匯編語言寫的一個兩次搬移的Bootloader程序,來引導較大的用戶程序。使用匯編語言是因為其代碼效率高,代碼長度短(本系統(tǒng)中只有256字節(jié))。兩次搬移是因為第一次DSP自行搬移后的Bootloader會占用片內(nèi)的0x0地址前1 KB空間,與下一步的用戶程序0x0地址拷貝沖突(中斷向量表必須放在0x0地址,否則會丟失中斷跳轉的絕對地址),且運行中的Bootloader不能覆蓋自身。所以把拷貝用戶程序的那部分代碼放在片內(nèi)較底端運行,騰出了用戶空間的0x0地址。最后整體拷貝結束后,Bootloader再跳轉到用戶程序入口地址c_int00運行。

3.2 用戶程序和CPLD程序

本系統(tǒng)中2片F(xiàn)PGA加載的原理一樣。為避免繁瑣,這里以1片F(xiàn)PGA_A為例來作介紹。

CPLD在系統(tǒng)中負責2項工作。

①映射DSP端Flash分頁寄存器:控制Flash的高3位地址線,分8頁,每頁1 MB空間。

②映射DSP端2片F(xiàn)PGA的加載寄存器:

a.配置寄存器FpgaA(B)_config_Reg[8:O]。負責配置數(shù)據(jù)和時鐘,高8位為Byte-Swapped前的數(shù)據(jù)位,輸出到配置引腳時進行字節(jié)交換,最低位為CCLK位。

b.控制寄存器FpgaA(B)_Prog_Reg[2:O]。負責外部控制引腳,分別為CS_B、RDWR_B和PROG_B。

c.狀態(tài)寄存器FpgaA(B)_State_Reg[2:0]。負責回讀配置中的握手信號,分別為BUSY、DONE和INIT_B。

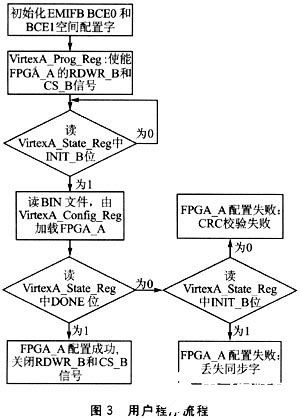

由Bootloader引導的用戶程序由C語言開發(fā),在CCS下調(diào)試通過。它主要實現(xiàn)Flash翻頁,把之前燒寫在Flash中的BIN文件,通過上述CPLD中3個加載寄存器對FPGA進行上電配置。具體流程如圖3所示。

當前FPGA配置時鐘CCLK是在用戶程序中通過DSP寫命令產(chǎn)生的,即寫FpgaA(B)_Config_Reg的CCLK位高低電平;同時8位配置數(shù)據(jù)也連續(xù)寫2次,由CPLD鎖存到FPGA總線上,便能充分保證圖1中該有效數(shù)據(jù)在CCLK上升沿上被鎖。

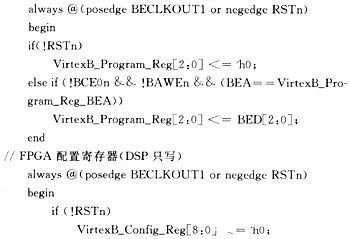

以下是CPLD中動態(tài)加載部分的Verilog代碼:

//FPGA控制寄存器(DSP只寫)

結 語

該系統(tǒng)已成功用于某公司一款軟件無線電平臺中,通過反復軟硬件調(diào)試,現(xiàn)已投放市場。此外,由于該系統(tǒng)中的DSP芯片TMS320C6416自帶PCI橋,因此該平臺設計有與主機通信的CPCI接口,支持32位的PCI總線帶寬,最大數(shù)據(jù)吞吐率能達到133 MB/s。所以,此平臺不僅可以實現(xiàn)上述提到的上電Flash自行加載FPGA的目的,還可在其配置完以后通過主機端對FPGA實現(xiàn)動態(tài)加載,充分滿足了軟件無線電中可重構化、實時靈活的指導思想。

責任編輯:gt

-

dsp

+關注

關注

552文章

7962瀏覽量

348310 -

FPGA

+關注

關注

1626文章

21678瀏覽量

602044 -

FlaSh

+關注

關注

10文章

1623瀏覽量

147787

發(fā)布評論請先 登錄

相關推薦

急需TMS320C6416的板級支持包bsp/bsl,求助

請問有TMS320C6416和TMS320C6747的對比表嗎?原來用的TMS320C6416,現(xiàn)在想換TMS320C6747 或TMS320C6747

tms320c6416的TCK、TDO、 TDI、TRST、TMS、EMU等能否直接接到JTAG上?

TMS320C6416 pdf datasheet

TMS320C6416 的軟件編程優(yōu)化

基于TMS320C6416的拓片圖像處理與優(yōu)化

基于DSP TMS320C6416的實時圖像處理系統(tǒng)

基于DSP TMS320C6416的數(shù)字下變頻技術

基于TMS320C6416的語音凈化系統(tǒng)

TMS320C6416 DSK技術參考詳細資料免費下載

TMS320C6414/TMS320C6415/TMS320C6416定點數(shù)字信號處理器數(shù)據(jù)表

基于DSP芯片TMS320C6416實現(xiàn)上電Flash自行加載FPGA的應用設計

基于DSP芯片TMS320C6416實現(xiàn)上電Flash自行加載FPGA的應用設計

評論