在過去幾年里,由于數(shù)據(jù)輸入/輸出的要求不斷提高,使用戶對(duì)數(shù)據(jù)總線帶寬提出更高的要求,由此產(chǎn)生了很多基于高速序列構(gòu)架的傳輸標(biāo)準(zhǔn)。包括PCI Ex-press,HyperTransport,InfiniBand,RapidIO和Star-Fabric等。

2002年第2季度PCISIG組織發(fā)布了PCI Express1.0規(guī)范,定位于設(shè)計(jì)成一種系統(tǒng)互連接口。該組織又于2005年第3季度發(fā)布PCI Express規(guī)范在工業(yè)控制領(lǐng)域的規(guī)范PICMG EXP.0 CompactPCI Express Specification R1.0,被稱之為CompactPCI Express(在下文中簡(jiǎn)稱為CPCIe)規(guī)范。

CPCIe系統(tǒng)可以兼容CPCI模塊,具體的實(shí)現(xiàn)方法是在系統(tǒng)中加入CPCIe到CPCI的橋接模塊,該模塊被稱為混合橋接模塊。

進(jìn)行混合橋接電路的設(shè)計(jì)主要實(shí)現(xiàn)以下內(nèi)容:

(1)PCI部分接口的設(shè)計(jì)實(shí)現(xiàn);

(2)PCIe總線接口設(shè)計(jì)實(shí)現(xiàn)。

1 設(shè)計(jì)原理

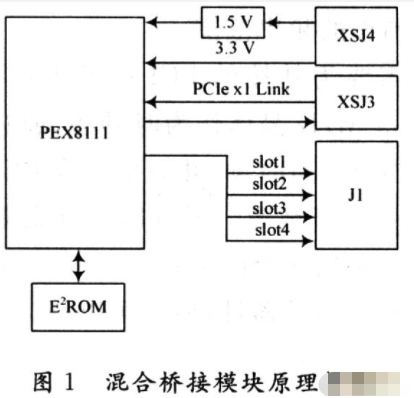

如圖1所示,該模塊由XSJ4連接提供3.3 V電源,在板上使用DC-DC電壓轉(zhuǎn)換模塊,將3.3 V電壓轉(zhuǎn)換為1.5 V電壓,提供給PEX8111使用。PEX8111的上行端口(Upstream)為x1的PCI Express接口,下行接口(Downstream)為32位/33 MHz的PCI總線,該P(yáng)CI接口可以實(shí)現(xiàn)PCI總線的Host功能。

2 實(shí)現(xiàn)方法

2.1 主要原器件選擇

在該設(shè)計(jì)中采用成熟技術(shù),選用常用、可靠的控制芯片,結(jié)合一些常用的外圍電路和專用電路實(shí)現(xiàn)全部的功能,即選擇PEX8111作為接口芯片,利用功能芯片實(shí)現(xiàn)硬件邏輯。

PEX8111是PLX公司推出的專門用于PCI Ex-press和PCI總線之間橋接的芯片,它包含1個(gè)x1的PCI Express端口和1路32位PCI接口。它的外圍電路少,設(shè)計(jì)簡(jiǎn)單。

2.2 PCI Express硬件接口實(shí)現(xiàn)

每個(gè)PCI Express的端口包括兩部分信號(hào),端口控制信號(hào)和通信信號(hào)。端口控制信號(hào)包括熱插拔控制信號(hào)、時(shí)鐘使能信號(hào)、電源使能信號(hào)等。通信信號(hào)主要由lane 信道組成,每個(gè)lane信道包含收發(fā)差分信號(hào)對(duì)各一個(gè),每個(gè)PCI Express的端口包含的lane信道數(shù)是可以伸縮配置的,也就是說包含lane信道的數(shù)目是可變的,在該模塊中單個(gè)端口包含1個(gè)lane信道。在 lane信道上傳輸?shù)氖歉咚俨罘中盘?hào),在每個(gè)信號(hào)差分對(duì)上信號(hào)的最高的傳輸速率可以達(dá)到2.5 Gb/s。在兩個(gè)設(shè)備之間互連的lane信道需要加入電容隔離直流信號(hào),考慮到傳輸信號(hào)的頻率,電容的封裝尺寸一般為0402,小的尺寸可以降低電容的串聯(lián)等效電感,提高電容在高頻信號(hào)區(qū)域的使用性能。

2.3 時(shí)鐘設(shè)計(jì)

發(fā)送器以2.5 Gb/s的速率定時(shí)輸出數(shù)據(jù)。實(shí)現(xiàn)該速率的時(shí)鐘必須精確在中心頻率±300 ppm內(nèi),它最大允許每1 666個(gè)時(shí)鐘偏離1個(gè)時(shí)鐘。設(shè)備獲取時(shí)鐘輸入的方式有兩種:采用本板時(shí)鐘和使用外部輸入時(shí)鐘,該設(shè)計(jì)使用外部時(shí)鐘。如果使用擴(kuò)展頻譜定時(shí)(Spread Spectrum Clocking,SSC)功能,一般都要求鏈路上的發(fā)送器和接收器必須使用同一參考時(shí)鐘,SSC是一種用于緩慢調(diào)制時(shí)鐘頻率的技術(shù),以便降低時(shí)鐘中心頻率處的EMI輻射噪音。有了SSC,輻射的能量就不會(huì)產(chǎn)生2.5 GHz的噪音尖峰信號(hào),因?yàn)檩椛淠芰勘环稚⒌?.5 GHz周圍小的頻率范圍。

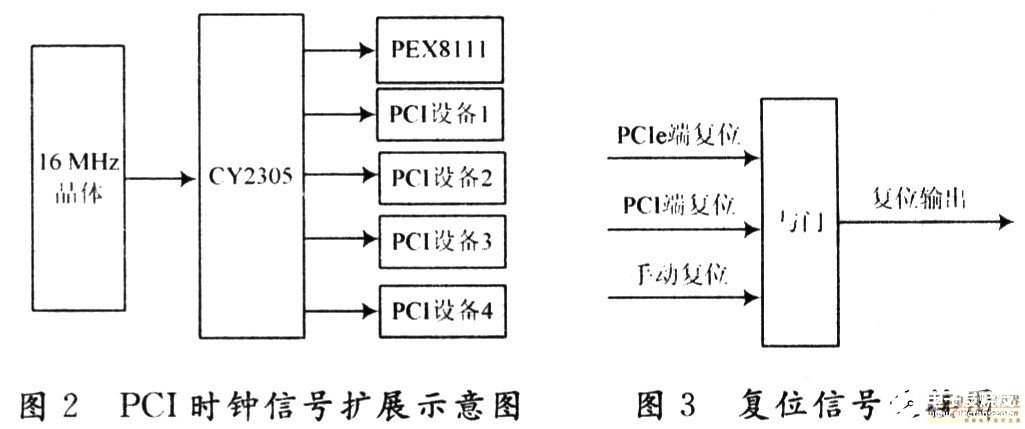

本模塊需要為外接的PCI設(shè)備提供時(shí)鐘信號(hào),如圖2所示。33 MHz晶體作為時(shí)鐘源,通過零延時(shí)緩沖器CY2305輸出5路時(shí)鐘,并分別作為PEX8111和4個(gè)外接PCI設(shè)備的時(shí)鐘源。零延時(shí)緩沖器是一種可以將一個(gè)時(shí)鐘信號(hào)扇出多個(gè)時(shí)鐘信號(hào),并使這些輸出之間有零延時(shí)和很低偏斜的器件,所以可以認(rèn)為4個(gè)外接PCI設(shè)備工作在同一時(shí)鐘下。

2.4 PCI接口設(shè)計(jì)

該P(yáng)CI接口實(shí)現(xiàn)的功能為PCI的HOST功能,包含總線信號(hào)和仲裁信號(hào)。在進(jìn)行該模塊設(shè)計(jì)時(shí)需要注意連接器J1的信號(hào)定義與標(biāo)準(zhǔn)的J1接口有一些差別。因?yàn)槿绻麑CI總線信號(hào)完整的引出需要兩個(gè)連接器J1,J2配合使用,但是因?yàn)楦咚龠B接器XSJ3處于原本J2的位置上,因此在缺少部分信號(hào)針的情況下無法實(shí)現(xiàn)完整PCI host功能,采取使用了特殊的CPCIJ1連接器的方法解決這個(gè)問題,這種連接器比普通J1連接器多出15個(gè)信號(hào)引腳,可以使用這些多余的引腳引出 REQn,ACKn信號(hào)。

2.5 電源設(shè)計(jì)

PEX8111芯片需要用到3種電源。其中PCI總線信號(hào)為5 V,I/O供電電壓為3.3 V,串行收發(fā)器的電源電壓為1.5 V,所以本模塊需要提供5 V,3.3 V和1.5 V三種電壓源。

5 V, 3.3 V電壓由系統(tǒng)提供,1.5 V由3.3 V電壓轉(zhuǎn)換獲得,選取國(guó)家半導(dǎo)體公司的LP2992作為3.3~1.5 V電壓轉(zhuǎn)換模塊。該模塊具有90%以上的轉(zhuǎn)換效率、簡(jiǎn)單的外圍電路、更小的封裝、2.5%以下的紋波電壓等特點(diǎn)。

2.6 復(fù)位設(shè)計(jì)

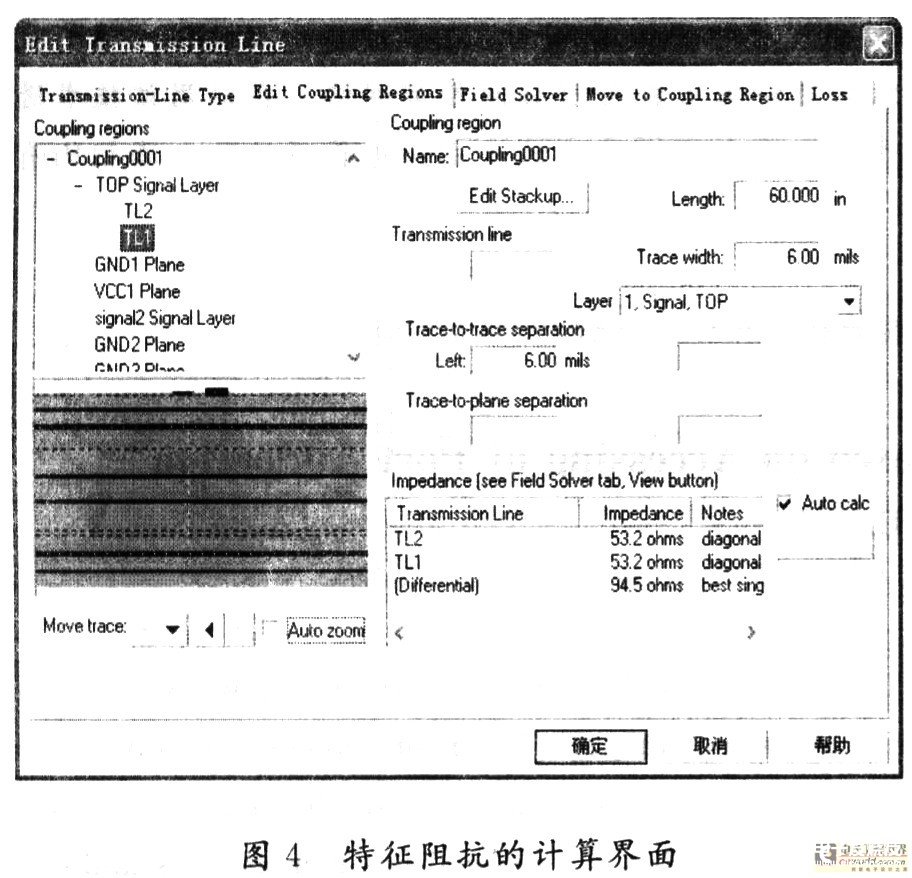

復(fù)位輸入有三個(gè),來自PCIe端的復(fù)位,來自PEX8111復(fù)位輸出,手動(dòng)復(fù)位信號(hào),保證在主機(jī)側(cè)出現(xiàn)冷復(fù)位和要求本板單獨(dú)復(fù)位的情況下,可以將復(fù)位信號(hào)向下傳遞,如圖3所示。

3 高速電路設(shè)計(jì)

基于CPCIe總線的電路屬于高速電路,在電路設(shè)計(jì)之初就采用仿真工具進(jìn)行驗(yàn)證,并根據(jù)仿真結(jié)果不斷調(diào)整自己的設(shè)計(jì)。

對(duì)所設(shè)計(jì)的電路進(jìn)行仿真是該設(shè)計(jì)的關(guān)鍵點(diǎn)。PEX8111芯片信號(hào)的種類和數(shù)目都比較少,在芯片外圍沒有復(fù)雜的邏輯設(shè)計(jì),在電路設(shè)計(jì)上對(duì)時(shí)鐘和電源的要求也比較簡(jiǎn)單,但是對(duì)傳輸在PCB上高速差分信號(hào)的質(zhì)量有很高的要求,這個(gè)要求也是當(dāng)前所有高速設(shè)計(jì)面臨的共性問題。由于高速PCB設(shè)計(jì)需要考慮的因素很多,比如介質(zhì)、平面分割、信號(hào)的等長(zhǎng)等,傳統(tǒng)的設(shè)計(jì)準(zhǔn)則已經(jīng)不再準(zhǔn)確,所以需要依靠仿真工具來提供設(shè)計(jì)依據(jù)。在該設(shè)計(jì)中采用的仿真工具是Mentor公司 Hyperlynx GHz,Hspice仿真模型,由器件的生產(chǎn)廠家提供。

仿真的過程主要包括前仿真和后仿真,以下敘述兩種仿真的具體內(nèi)容。

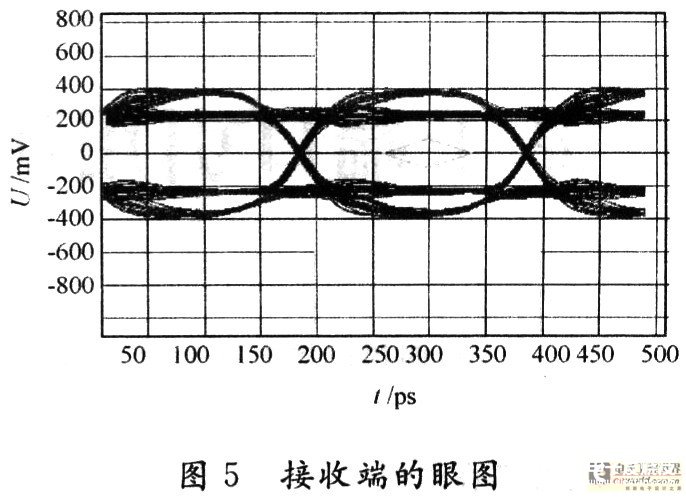

3.1 阻抗控制

PCI Express規(guī)范要求走線阻抗為100 Ω,差分阻抗、單端阻抗為50 Ω。阻抗主要由線寬、線間距、銅皮厚度、介質(zhì)層厚度、介質(zhì)材料等決定。特征阻抗的計(jì)算界面如圖4所示,經(jīng)計(jì)算特征阻抗為94.5 Ω,滿足要求。

PCI信號(hào)的特征阻抗為75 Ω,為了同時(shí)滿足PCIe和PCI的阻抗要求,可以采用兩種手段,首先可以將兩種信號(hào)線的寬度設(shè)置為不同寬度;其次是將兩種信號(hào)放置在不同信號(hào)平面上。兩種方法各有優(yōu)劣,前者由于制作工藝限制線寬有下限,所以需要將PCIe信號(hào)線寬設(shè)置得比較寬,不利于走線。后者需要增加信號(hào)層,直接增加成本。采取什么方法需要綜合考慮。

3.2 后仿真的實(shí)現(xiàn)

后仿真主要是在PCB繪制完成后,在前仿真的基礎(chǔ)上將PCB相關(guān)的數(shù)據(jù)導(dǎo)入后再進(jìn)行的仿真。由于PCI部分的信號(hào)電路設(shè)計(jì)已經(jīng)非常成熟,有大量的經(jīng)驗(yàn)法則可以借用,并且信號(hào)的速度比較慢,因此不對(duì)這部分信號(hào)進(jìn)行仿真,只對(duì)PCIe差分信號(hào)對(duì)進(jìn)行仿真。圖5給出導(dǎo)入PCB參數(shù)后,接收端眼圖的仿真結(jié)果。可見,所有時(shí)間點(diǎn)上的信號(hào)電壓均在接收器可以識(shí)別的范圍之內(nèi)。

4 結(jié) 語

隨著技術(shù)的發(fā)展。基于CPCIe總線接口的模塊會(huì)被越來越多的使用,但是從成本考慮,CPCI接口的模塊不會(huì)被立即完全的替換,CPCIe模塊和CPCI模塊在機(jī)箱中共存的情況將長(zhǎng)期存在,混合橋接模塊是將兩者聯(lián)系起來的紐帶,它將作為一個(gè)重要的插件模塊在工業(yè)控制計(jì)算機(jī)系統(tǒng)中廣泛應(yīng)用。

責(zé)任編輯:gt

-

電源

+關(guān)注

關(guān)注

184文章

17586瀏覽量

249502 -

芯片

+關(guān)注

關(guān)注

453文章

50407瀏覽量

421848 -

總線

+關(guān)注

關(guān)注

10文章

2867瀏覽量

87990

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

功放橋接電路中,為什么很多模擬功放的規(guī)格書中給的橋接電路都有那顆680歐電阻呢?

realtek 8111c找不到

PEX8111 pdf datasheet

基于SPI串行總線的語音接口電路的軟硬件設(shè)計(jì)

非多路復(fù)用與多路復(fù)用總線轉(zhuǎn)換橋的設(shè)計(jì)與實(shí)現(xiàn)

基于FPGA的PEX8311的LBS控制器的實(shí)現(xiàn)

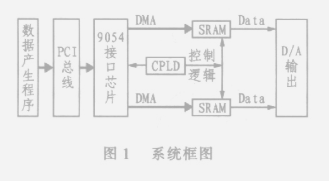

采用PCI橋接口芯片PLX9054和CPLD器件實(shí)現(xiàn)任意波形發(fā)生器的設(shè)計(jì)

CPCIe-BP6606硬件使用說明書

通過PLX PCI9080橋接芯片實(shí)現(xiàn)TMS320C6000擴(kuò)展總線與PCI總線的接口

基于PEX8111芯片和CPCIe總線實(shí)現(xiàn)混合橋接電路的設(shè)計(jì)

基于PEX8111芯片和CPCIe總線實(shí)現(xiàn)混合橋接電路的設(shè)計(jì)

評(píng)論