毫無疑問,多核多線程是未來處理器的發(fā)展方向。回首處理器的發(fā)展歷程,并行技術從指令級的超標量發(fā)展到線程級的超線程或者并發(fā)多線程,再到今天處理 器級的多內(nèi)核,總的趨勢都沒有改變。英特爾、Sun和IBM等大公司目前已經(jīng)投身到多核或者多線程技術的浪潮之中。當今的網(wǎng)絡應用日趨復雜,對性能的要求 不斷提高,無論是需求推動技術,還是技術激發(fā)了新的需求,并行技術都將是未來信息基礎設施建設的必然選擇。

對于嵌入式裝置而言,多核技術可以提供更高的處理器性能、更有效的電源利用率,并且占用更少的物理空間,因而具有許多單核處理器無法具備的優(yōu)勢。與多核解決方案如影隨形的,就是多處理器技術,也就是在同一塊電路板或同一個集成系統(tǒng)中包含多個處理器。

要想充分發(fā)揮多核以及多處理器解決方案的潛能,僅僅依靠強有力的芯片是不夠的,還需要采用新的編程方法。伴隨著新的編程方法,同樣也需要新 的調(diào)試方法和工具,才能確保軟件和硬件開發(fā)人員在完整的多核系統(tǒng)環(huán)境中展開調(diào)試工作,同時對“編譯—編輯—調(diào)試 ”的流程進行優(yōu)化。

在傳統(tǒng)上,JTAG調(diào)試技術主要是用于硬件Bring-Up,如今也常常被用于配合基于代理的調(diào)試(agent-based debugging)。然而,在多核和多處理的環(huán)境中,片上調(diào)試(on-chip debugging)正在扮演著越來越重要的角色,因為這種技術更便于隔離運行在單個或者多個內(nèi)核中不同軟件之間復雜的交互活動,從而幫助開發(fā)人員對操作 系統(tǒng)或者中間件實施更加有效的調(diào)試。

認識多核基本架構(gòu)

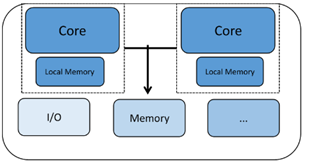

多核處理器在同一個芯片中植入了多個處理器引擎,這就可以提供更高的CPU性能、功能特性和分區(qū)能力。一般說來,多核有兩種實現(xiàn)形式。

第一,SMP( Symmetric multiprocessing,對稱多處理)。在這種情況下,開發(fā)人員面對的是單一的抽象化硬件平臺,由SMP操作系統(tǒng)來決定具體由哪一個內(nèi)核來運行哪 個任務,其中每個內(nèi)核都是相同的,而且在同一個操作系統(tǒng)的管理控制之下,共享同一個內(nèi)存。

第二,AMP (Asymmetric multiprocessing,非對稱多處理)。在這種情況下,各個處理器內(nèi)核都運行著各自獨立的操作系統(tǒng)。這種獨立性意味著,其中各個處理器內(nèi)核既可 以是同構(gòu)的,并且運行同樣的操作系統(tǒng),也可以是異構(gòu)的并運行各自不同的操作系統(tǒng)。

多核環(huán)境顯著增加了系統(tǒng)復雜度,因而在對操作系統(tǒng)和與多核相關的硬件進行調(diào)試的時候,就必須采用一整套更有效的工具。另外,盡管大家都認為 多核就是指在同一個芯片中放入多個內(nèi)核,但是在實際開發(fā)工作中所遇到的多處理問題,實際上不僅僅局限于在單一芯片中的多個內(nèi)核。事實上,不論這些處理器內(nèi) 核是在同一個芯片之中,或者分布在同一個電路板中的多個芯片之中,甚至同一個系統(tǒng)中的多個電路板之中,開發(fā)人員都必須解決好多處理環(huán)境中的調(diào)試問題。相對 于最近出現(xiàn)的單一芯片多核架構(gòu),有多個處理器芯片和多個處理器電路板組成的復雜系統(tǒng)已經(jīng)存在很多年了。因此,多處理架構(gòu)的調(diào)試問題其實早已存在,只是單一 芯片內(nèi)多核架構(gòu)的普及將多處理系統(tǒng)調(diào)試問題更加尖銳地擺在了開發(fā)人員面前。

從這個意義上,多年前就開始從事多處理環(huán)境軟件開發(fā)的廠商就積累了更豐富的經(jīng)驗,在應對多核軟件開發(fā)方面站在了更為有利的地位。例如 Wind River公司經(jīng)典的實時操作系統(tǒng)VxWorks在多年前最初的設計思路就是基于多處理架構(gòu)的,因此不論從運行環(huán)境還是開發(fā)調(diào)試工具任何一方面看,對于多 核環(huán)境的適應能力都比其他工具要強得多。

認識多核調(diào)試難點

多核與多處理技術的融合為系統(tǒng)調(diào)試帶來了許多新的挑戰(zhàn),因為系統(tǒng)復雜度不斷增加,要通過優(yōu)化硬件和軟件來充分發(fā)揮其中的性能潛力,難度就更大了。其中最主要的難點有以下幾個方面。

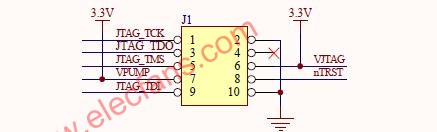

對于多核JTAG調(diào)試來說,有三種主要的技術選擇:第一,以單一JTAG接口支持所有內(nèi)核的調(diào)試器;第二,在單一JTAG調(diào)試接口中采用獨 立調(diào)試器的JTAG多路(Muxing)技術;第三,JTAG鏈接器或者可編址掃描端口(Addressable Scan Port)。

在多核調(diào)試中,上述三個技術途徑都是在處理同一個核心問題——由SoC廠商所提供的JTAG接口所造成的局限性。 為了節(jié)省成本,許多SoC廠商都只為芯片提供單一的JTAG接口,而不理會其中包含了多少個內(nèi)核。對于開發(fā)者來說,最大的挑戰(zhàn)就是經(jīng)濟有效地使用這些接口 來同步多核以及多處理的調(diào)試工作。其中,單一調(diào)試器方式采用IEEE 1149.1標準daisy-chain方法。

認識多核調(diào)試方法

對于多核架構(gòu)來說,單一調(diào)試器的主流選項仍然是JTAG多路技術。這種技術對IEEE JTAG技術規(guī)范進行了拓展,以便為通過共享JTAG接口連接起來的每個內(nèi)核提供獨立的調(diào)試器。在多路技術的支持下,通過對希望調(diào)試的內(nèi)核進行注冊登記 (Registering),開發(fā)人員可經(jīng)由單一JTAG接口訪問多個離散狀態(tài)的內(nèi)核。這種解決方案的最大優(yōu)勢在于它的連接和調(diào)試性能。因為多路技術單獨 連接到每個內(nèi)核,因而避免了daisy-chaining方法中所遇到的比特位移(bit shifting)方面的麻煩,因而在單芯片中的多核系統(tǒng)中具有更高的性能。這種方式的另一個好處是不需要對開發(fā)工具進行修改,從而可以順暢地應用在多個 開發(fā)項目之中。

多路技術(Muxing)方法所存在的主要問題是在多內(nèi)核調(diào)試過程中無法同時啟動和停止內(nèi)核來同步應用。如果要停止全部內(nèi)核,開發(fā)人員只能 順序地逐個進行,這就導致了調(diào)用延遲問題。在調(diào)試過程中的延遲問題,會導致很難在內(nèi)核之間的操作系統(tǒng)、中間件和應用中找到發(fā)生問題的確切位置,特別是當運 行在不同內(nèi)核之中的應用存在相互依賴性的時候,這個問題就更為突出。例如,某個產(chǎn)品包含DSP功能和ARM 9內(nèi)核,其中DSP用來處理視頻流,ARM 9內(nèi)核提供文件系統(tǒng),那么內(nèi)核的啟動與停止同步將會十分關鍵。如果調(diào)試過程中在ARM內(nèi)核的啟動和DSP的停止之間出現(xiàn)過多的延遲,DSP視頻流數(shù)據(jù)很快 就會溢滿ARM文件緩沖區(qū),而視頻流也將會中止。如果出現(xiàn)這種情況,就很難判斷系統(tǒng)中的問題出在哪里。而且,多路進程也給開發(fā)人員在故障排除時帶來了許多 新的問題,將會大幅度增加調(diào)試時間。

另外,如果在有多個廠商產(chǎn)品組成的異構(gòu)多核環(huán)境中進行調(diào)試工作,例如處理器來自一個廠商,而DSP器件來自另一個廠商,還會有更復雜的問題 需要處理。因為這種情況下的多路(Muxing)機制更為復雜,如果各部分之間的兼容性沒有得到保證,也就很難保證系統(tǒng)正常運行。此時,僅僅依靠多路技術 是無法解決問題的,開發(fā)人員就需要采用可編址掃描端口(addressable scan port),這也可能是最后僅有的方法了。這種架構(gòu)需要用到非常特殊的組件,這些組件可以讓開發(fā)人員把JTAG掃描鏈分割成多個功能組,并通過唯一的地址 來訪問每個功能組。這是一種多支路(multi-drop)架構(gòu),經(jīng)常被用于底板(Backplane)環(huán)境之中。在這里,有一個分別可編址的掃描鏈在底 板內(nèi)實現(xiàn)路由(Routed),從而使機箱中的每個底板都擁有自己專屬的掃描鏈。這種架構(gòu)的運行速度受限于可編址掃描端口的速度,最典型的情況是 25MHz。

擁有先進多核調(diào)試工具

Wind River擁有的JTAG加速器和服務器技術可以顯著降低JTAG序列包之間的空閑時間,完全充分地利用了可用的JTAG帶寬。與JTAG有關的另一個問 題涉及到調(diào)試能力,例如用停止請求信號來立即停止某個內(nèi)核,或者用停止指示信號來停止某個內(nèi)核并同步其他的內(nèi)核的停止。與其他所有的局限性一樣,這類問題 也依賴于廠商的實現(xiàn)方法。

Wind River on-chip debugging(片上調(diào)試)解決方案可以同時啟動和停止多個內(nèi)核。實際上,Wind River提供的JTAG解決方案,也就是Workbench On-Chip Debugging,是以集中化的方式來實現(xiàn)多核和多處理的調(diào)試功能。這個解決方案可以在單一掃描鏈(Scan Chain)中同時調(diào)試多達8個內(nèi)核。而且,不管這些內(nèi)核處于同一個芯片之中、分布在線路板中的多個芯片或者分布在復雜系統(tǒng)中的多個線路板之中, Workbench On-Chip Debugging都能夠應付自如。

在Wind River的多核解決方案中,開發(fā)人員可以同時停止或者啟動任何內(nèi)核,在一個或者多個內(nèi)核上設置斷點,其中還可以包括條件斷點。此外,Workbench Eclipse框架和基于代理的調(diào)試方式使開發(fā)人員在單一控制臺上即可管理多內(nèi)核/多處理應用的開發(fā)。開發(fā)人員可以在JTAG調(diào)試和基于代理調(diào)試二者之間 靈活地選擇,例如在硬件Bring-Up、內(nèi)核、中間件和其他應用功能調(diào)試的時候采用JTAG連接,然后在自己認為適當?shù)臅r機平滑地轉(zhuǎn)移到基于代理的調(diào) 試,而這些調(diào)試工作都是圍繞著同一個應用的。這些能力都會增加不同開發(fā)人員之間的協(xié)同能力,同時改善異常問題的判定效率。

結(jié)論

在多核開發(fā)中,JTAG調(diào)試可以承擔非常有價值的角色,有效地改善“編輯-編譯-調(diào)試”周期時間。然而,實現(xiàn)這一 點的前提是把JTAG調(diào)試與基于標準的集成化開發(fā)環(huán)境(例如Eclipse)緊密地集成起來。最理想的技術方案是,在Daisy Chain中采用遵從IEEE 1149.1 JTAG標準的單一的JTAG調(diào)試器,而JTAG的主要作用是改善系統(tǒng)的吞吐能力和性能。

責任編輯:gt

-

處理器

+關注

關注

68文章

19160瀏覽量

229116 -

接口

+關注

關注

33文章

8497瀏覽量

150834 -

JTAG

+關注

關注

6文章

398瀏覽量

71597

發(fā)布評論請先 登錄

相關推薦

ARM JTAG調(diào)試的基本原理

ARM JTAG 調(diào)試原理

嵌入式JTAG調(diào)試方法步驟

JTAG調(diào)試快速入門

基于ARM開發(fā)的JTAG仿真器的調(diào)試設計

《ARM JTAG 調(diào)試原理》下載

多核專家系列:多核軟件遷移與開發(fā):挑戰(zhàn)與解決方案

多核軟件調(diào)試方法與困難

多核軟件調(diào)試的難點和新方法分析

多核處理器的基本架構(gòu)是什么?有哪些調(diào)試方法?

掌握多核編程和調(diào)試的挑戰(zhàn)

多核JTAG調(diào)試方法的特點及應用挑戰(zhàn)

多核JTAG調(diào)試方法的特點及應用挑戰(zhàn)

評論