作者:伍冬,潘立陽,段志剛,朱鈞

為了減少芯片面積,提高電荷泵的增益,提出一種基于共享技術的電荷泵電路。通過改變兩個子電荷泵的串并連接關系,既可以產生一種電壓較高而電流驅動能力較小的負高壓,也可以產生一種電壓較低但是電流驅動能力很大的負高壓,這不僅滿足了系統在編程和擦除時對高壓的不同需求,而且還節省了大約50%的芯片面積。電荷泵電路還采取了對其中P型MOS管的襯底電壓進行動態控制的方法。模擬結果表明,該電荷泵的增益提高了大約14%。該電路特別適用于需要兩種以上負高壓以完成編程和擦除操作的快閃存儲器。

電子可擦除可編程存儲器(electrically-erasableprogrammable read-only memory,EEPROM)和快閃存儲器在編程和擦除操作時都需要高壓,因此電荷泵電路在單電源的嵌入式存儲器芯片中扮演著極其重要的作用,其功耗,面積和在低電源電壓下的工作能力等直接影響到整個存儲芯片的性能。而且在實際應用中,一個存儲器芯片內部一般會需要不止一種正高壓和負高壓,所以系統中會需要多個正高壓電荷泵和負高壓電荷泵,這使得電荷泵所占芯片面積超過整個存儲器芯片中外圍電路的一半。對于采用帶帶隧穿熱電子注入(band-to-bandtunneling induced hot electron,BBHE)進行編程的p溝道DINOR(p-channeldivided bit-line NOR)結構的快閃存儲器,它需要至少一個正高壓電荷泵和兩個負高壓電荷泵。對于采用源極誘導帶帶隧穿熱電子注入(source induced band-to-band hotelectron_,SIBE)方式進行編程的新型快閃存儲器,系統總共需要2個正高壓電荷泵和3個負高壓電荷泵。

由于電荷泵電路所占據的面積很大,尤其當電源電壓逐漸從5V降到1.8V甚至1.2V時,要產生足夠的高壓,電荷泵必須要增加級數或者增大耦合電容的大小,這使得電荷泵電路占據的面積不斷增加。因此電荷泵的共享技術在減少芯片面積上非常重要,但是這要么會增加工藝的難度,要么使得電路結構變得非常復雜。

本文通過改變電荷泵的串并連接關系,在不增加任何工藝難度和電路復雜度的情況下,實現了電荷泵的共享,使得電荷泵電路所占據的面積大大減少。

1 共享技術電荷泵的結構和工作原理

表1給出SIBE結構快閃存儲器的典型操作模式,其中編程時加到位線上的-3.3 V高壓需要提供大于100μA的驅動能力,以實現多位數據同時編程。

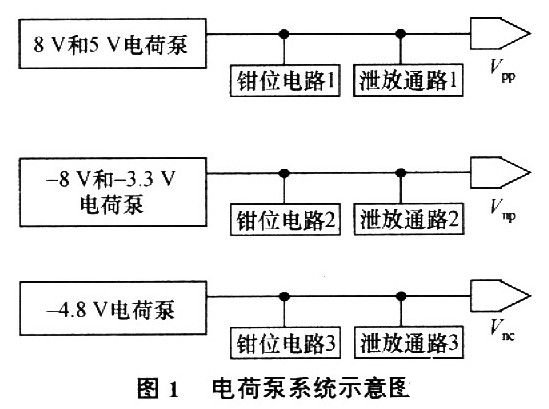

圖l是本文采用的電荷泵系統示意圖,其中8V和5V電荷泵用于產生一個8V的編程字線電壓和5V的擦除源線電壓Vpp,-8V和-3.3V電荷泵是一個基于共享技術的電荷泵電路,它可以產生-8V(驅動能力大于10μA)的字線擦除電壓和-3.3 V(驅動能力大于l00μA)的位線編程電壓Vnp。而-4.8V電荷泵則產生加到選擇柵上的-4.8V高壓Vnc,用于把-3.3V的編程電壓傳遞到選中的存儲單元上,以及用在位線電壓轉換模塊中。鉗位電路的作用是對輸出高壓進行鉗位,使得輸出高壓穩定在所需要的電壓值上。而在電路停止工作時,通過泄放通路可以把輸出端的電壓置為OV。

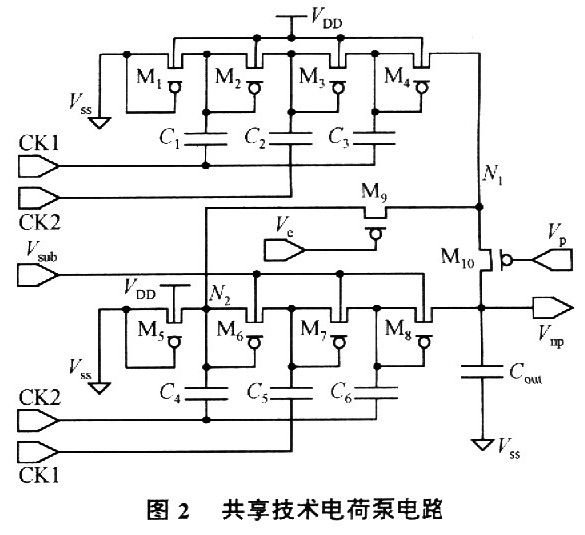

為了降低芯片面積而提出的基于共享技術的負高壓電荷泵電路見圖2,它可以產生-8V和-3.3V兩種負高壓,其中Ve和Vp是高壓控制信號,Ve可以在Vnp和電源電壓VDD之間轉換,而Vp可以在-4.8V和VDD之間轉換,其中-4.8V來源于-4.8V電荷泵。其輸入輸出關系如表2所示。當需要產生-3.3V電壓時,讓Ve等于VDD,而置Vp為 -4.8 V,系統可以看作是兩個三級的子電荷泵

(分別由PMOS管M1-M4,耦合電容C1-C3和PMOS管M5-M8,耦合電容C4-C6組成)的并聯,在兩相非重疊時鐘CKl和CK2的驅動下,Vnp輸出-3.3V電壓,由于連接到C3和C6上的時鐘信號分別為CKl和CK2,所以兩個子電荷泵在一個時鐘周期內將分別對輸出端Vnp充電一次。這不僅大大降低了輸出端電壓的波動性,同時還增加了輸出端的驅動能力,滿足了多位同時編程時對大驅動電流的需求。如果系統需要-8V的高壓,把Vp置為VDD,而把Ve連接到高壓輸出端Vnp,這樣M10將被關斷,而剛開始時由于Vnp為0V,所以M9不會導通,電路仍舊處于兩個子電荷泵并聯工作狀態,只是它們的輸出端被M10隔開。隨著Vnp由0V逐漸變小,它的電壓將低于節點N2的電壓,M9會逐漸導通,此時系統可以看作是一個六級的電荷泵(由M1-M4和M6-M8以及C1-C6組成),最終系統將產生-8V的高壓。這樣,和采用兩個獨立電荷泵分別產生-8V和-3.3V的方法相比,該電荷泵可以節省大約50%的芯片面積。需要注意的是M6-M8的襯底電壓由Vsub控制,這主要是為了降低它們的襯偏效應,增加電荷泵的增益。

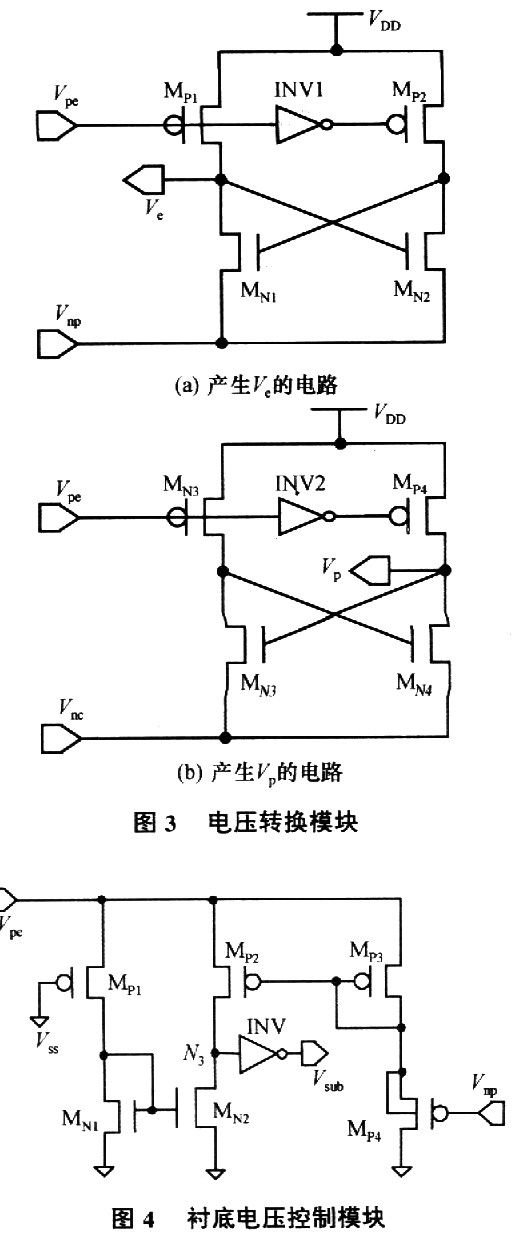

共享技術電荷泵的Ve、Vp時序由圖3所示的電壓轉換模塊產生。圖3a可以實現Ve在VDD和vnp之間的轉換,而圖3b實現Vp在VDD和- 4.8V之間的轉換。結合圖2,其工作模式見表2。當控制信號Vpe為高時,電荷泵產生-8V高壓,而當Vpe為低時,電荷泵產生-3.3V高壓。

為了降低共享電荷泵中PMOS管的襯偏效應,提高電荷泵的增益,本文采用了一個襯底電壓控制模塊,見圖4所示。其中Vnp連接到-8V和-3.3V電荷泵的輸出端,Vpe是控制信號。其中NMOS管Mw1和MN2以及PMOS管Mp2和MP3構成兩對電流鏡。當Vpe為OV時,該模塊將不工作,節點V3等于OV,輸出端Vsub的電壓等于VDD,并送到圖2中的Vsub端,且電荷泵將產生-3.3V高壓。當Vpe為高時,該模塊開始工作,隨著圖2中電荷泵的工作,Vnp將由0V逐漸降低,PMOs管MH的導通能力逐漸增大,Mp3和Mp2的柵極電壓將逐漸降低,這樣Mp2的導通能力逐漸增大,倒相器輸入端的電壓將由OV逐漸上升,最終倒相器INV開始翻轉,Vsub的電壓將由初始的VDD變成OV。通過調整圖中PMOS和NMOS管的尺寸就可以保證當Vsub變成OV時,圖2中PMOS管Mp6-Mp8的p-n結不會正偏。這樣就減輕了Mp6-Mp8的襯偏效應,提高了電荷泵的增益。

2 模擬結果

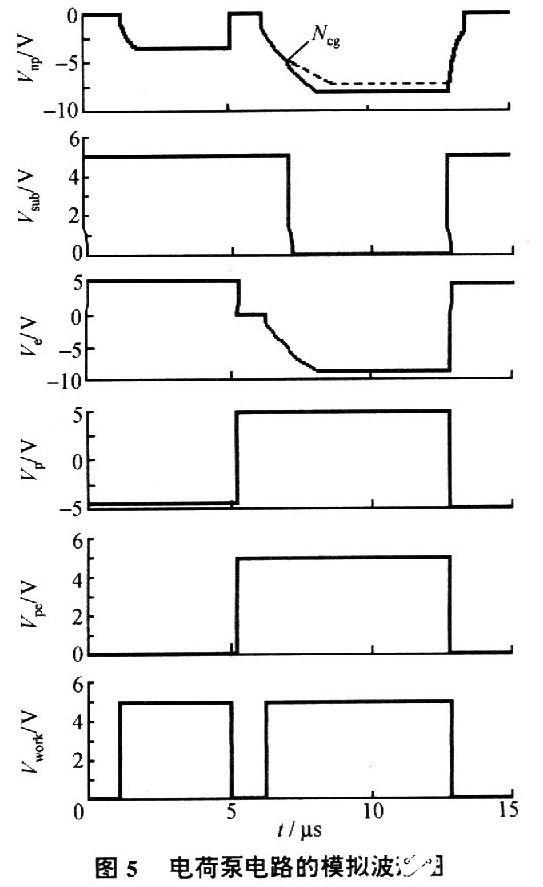

為了驗證本文所述電荷泵的性能,采用清華大學微電子所開發的1.4 μm高壓工藝參數,用軟件HSPICE對其進行了模擬。其中高壓NMOS管的閾值電壓為0.7 V,高壓PMOS管的閾值電壓為-0.8V。優化后的耦合電容C1到C6均為12pf,所用的時鐘頻率為20MHz,電源電壓VDD為5.0V。

圖5是電荷泵電路的模擬波形圖。其中Vwkrk是控制信號,當Vwork為高時,輸入時鐘CKl和CK2,電荷泵電路開始工作。當Vwork為低時,時鐘停止輸入,電荷泵電路不工作,只是通過泄放通路把輸出端Vnp的電荷泄放到地。從圖5可以看到,當Vpe為低時,Vp為-4.8V,而Ve等于5.OV,電荷泵電路的輸出電壓Vnp等于-3.3V。當Vpe為高時,Vp等于5.0V,而Ve和Vnp的電壓一致,最終系統輸出電壓Vnp等于-8V。而且可以看到,當負高壓電荷泵工作一段時間,Vnp達到-5V后,Vsub的電壓將由5.0V變為0V,這降低了PMOS管Mp6-Mp8的襯偏效應,使得高壓輸出端Vnp的波形上出現一個拐點Ncg,而且拐點后的電壓下降的速度明顯加大并最終達到-8V(其中虛線部分是沒有采用襯底電壓控制模塊時Vnp的波形,其電壓最終只能下降到-7V),這使得電荷泵的增益提高了大約14%。

3 結 論

本文提出一種基于共享技術的電荷泵電路,通過改變兩個子電荷泵的串并連接關系,可以在同一個電路中產生所需的兩種負高壓,從而節省了大約50%的芯片面積。通過一個襯底電壓控制模塊對電荷泵中PMOS管的襯底電壓進行動態控制,使電荷泵的增益提高了大約14%。該電路特別適用于需要兩種以上負高壓以完成編程和擦除操作的快閃存儲器。

責任編輯:gt

-

芯片

+關注

關注

450文章

49622瀏覽量

417086 -

存儲器

+關注

關注

38文章

7365瀏覽量

163084

發布評論請先 登錄

相關推薦

電荷泵設計原理及在電路中的作用

如何選擇合適的電荷泵

電荷泵電路的基本原理

電荷泵解決方案

一種新型低電荷共享電荷泵電路

應用于深亞微米存儲器的電荷泵設計

共享技術思維電荷泵滿足系統在編程和擦除時對高壓的不同需求

共享技術思維電荷泵滿足系統在編程和擦除時對高壓的不同需求

評論