采樣保持(THA)輸出噪聲有兩個關鍵噪聲分量:采樣噪聲和輸出緩沖放大器噪聲。

采樣噪聲分量

噪聲的第一個分量是采樣過程中產生的采樣噪聲,它用外差法將THA的前端噪聲轉化到頻域的每個奈奎斯特區間中。整個前端帶寬產生的噪聲是在每個時域樣本中捕獲,然后將該噪聲大致均勻地分布在每個奈奎斯特區間上。此噪聲由前端熱噪聲和采樣抖動噪聲組成,無法被濾除,除非在輸出端使用低通濾波器轉折頻率來顯著降低奈奎斯特帶寬。通常不使用這種濾波,因為它會損壞時鐘速率所提供的可用帶寬,并導致輸出波形的建立時間性能降低。

輸出緩沖放大器噪聲分量

噪聲的第二個分量是THA輸出緩沖放大器噪聲貢獻。THA不會對此噪聲采樣,但濾波可以降低此噪聲。可以承受的輸出濾波量取決于所用特定時鐘頻率的建立時間要求。關于容差限制的大致原則是輸出路徑的帶寬(包括模數轉換器(ADC)輸入帶寬)至少為時鐘速率的2倍,以支持下游ADC所采樣的THA波形的精確(例如線性)建立。高速ADC的輸入帶寬通常在2倍時鐘速率指標附近;因此,使用高速ADC時通常不需要額外的濾波。

采樣放大器的噪聲密度

與常規非采樣放大器不同,THA頻域中的有效等效輸入噪聲譜密度取決于模數轉換之前的輸出濾波帶寬。出于這個原因,采樣器件通常不會用這些項來指定噪聲,因為實際輸出噪聲是采樣輸入緩沖器噪聲的復雜函數,其將整個輸入帶寬中的噪聲混疊到第一奈奎斯特區間,輸出緩沖放大器噪聲響應輸出限帶的方式與常規放大器相似。采樣系統的重要指標量是所保持輸出樣本中的時域輸出噪聲,因為ADC會轉換此輸出噪聲。

折合到輸入端的頻域噪聲密度最好通過下式確定:輸出時域采樣噪聲除以輸入采樣帶寬與π/2的乘積的平方根。

單極點帶寬和輸出時域噪聲相同時,該定義給出的折合到輸入端噪聲密度與單位增益連續波(CW)放大器(未采樣)相同。之所以有π/2,是因為單極點低通傳遞函數的有效噪聲帶寬為BW3dB×π/2。對于沒有輸出限帶的HMC661LC4B(例如輸出緩沖放大器的全部7 GHz帶寬),當使用1.05 mV rms時域采樣噪聲和18 GHz 3 dB輸入帶寬時,此噪聲帶寬對應于約6.2 nV/(√Hz)的等效輸入噪聲密度。

由于熱本底噪聲為0.64 nV/(√Hz),所以有效噪聲指數約為19.7 dB。此噪聲指數很高,這是因為THA中有好幾級,所有級均以單位增益工作,故每級都會增加噪聲。

非采樣放大器的噪聲密度

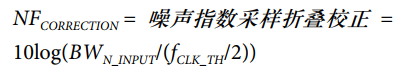

就等效輸入噪聲性能而言,有效采樣噪聲指數的這種定義對普通非采樣放大器是一個合理的比較。這并未考慮采樣引起的噪聲折疊,而典型混頻器噪聲指數定義可能會使用噪聲折疊。要獲得混頻器噪聲指數定義,須添加一個噪聲折疊修正系數,它由輸入采樣噪聲帶寬與奈奎斯特帶寬的比值給出,如下式所示:

其中,BWN_INPUT表示輸入采樣帶寬的有效噪聲帶寬。

例如,當HMC661LC4B以4 GHz時鐘速率工作時,噪聲折疊(18 GHz×π/2)至2 GHz的奈奎斯特區間所導致的額外降級是由混頻器定義的,噪聲指數額外降低約11.5 dB ,產生19.7dB + 11.5dB = 31.2dB的混頻器定義總噪聲指數。

估算輸出噪聲頻譜

為了估算輸出噪聲頻譜,應利用如下事實:所有前端噪聲都被外差或折疊到一個奈奎斯特區間中,而輸出緩沖器噪聲分布在輸出緩沖器噪聲帶寬的大約7×π/2 GHz上。仿真表明,盡管小信號輸出緩沖器帶寬為7 GHz,HMC661LC4B和HMC760LC4B中的組合輸出緩沖放大器級的有效噪聲帶寬約為12.6 GHz,對應于8 GHz的有效-3 dB噪聲密度帶寬。

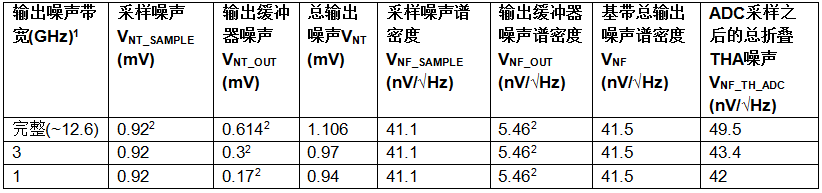

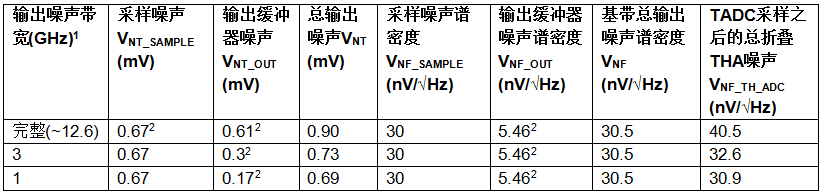

這種微小差異似乎是由噪聲在信號鏈中不同帶寬點的分布式貢獻造成的。表1和表2顯示了不同輸出噪聲帶寬濾波情況下HMC661LC4B和HMC760LC4B的輸出時域和頻域噪聲分量的明細,工作時鐘速率為1 GHz。

獲得完整輸出帶寬

完整輸出帶寬數據來自全布線寄生效應下的詳細芯片仿真,但結果與實驗室數據相當吻合(對于HMC661LC4B,測得的集成噪聲電壓VNT= 1.05 mV rms)。假定輸出緩沖器噪聲譜密度不變(因為濾波通常在外部進行),計算輸出帶寬減小的情況。表1和表2模擬了完整輸出帶寬情況下的VNT_SAMPLE、VNT_OUT和VNF_OUT。根據這些基本參數可直接導出所有其他量。

在采樣過程中,下游ADC將輸入帶寬(表1和表2中所示的濾波和ADC輸入帶寬的組合)上的所有THA噪聲外差到一個ADC奈奎斯特區間。因此,總折疊噪聲是ADC噪聲帶寬上的總THA輸出放大器時域噪聲的一部分。

表1.HMC661LC4B18 GHz帶寬THA仿真和計算得到的噪聲分量匯總,時鐘頻率為1 GHz

1. 針對任何濾波和ADC帶寬。

2. 仿真值,所有其他值均由仿真值計算。

表2.HMC760LC4B5.5 GHz帶寬THA仿真和計算得到的噪聲分量匯總,時鐘頻率為1 GHz

1. 針對任何濾波和ADC帶寬。

2. 仿真值,所有其他值均由仿真值計算。

作為參考,使用HMC661LC4B驅動National Semiconductor ADC12D1600 ADC的數據與表1和表2中的仿真值具有很好的一致性。特別是,針對ADC快速傅立葉變換(FFT)中的譜密度,測得THA噪聲分量約為37 nV/(√Hz)。National Semiconductor轉換器的輸入噪聲帶寬估計約為2.8(π/2) = 4.4 GHz。對于這種情況,總THA輸出時域噪聲約為0.98 mV rms,對應于43.9 nV/√Hz的噪聲譜密度(經ADC采樣后)。此值在ADC數字化噪聲頻譜中的實測THA分量的1.5 dB以內。

結語

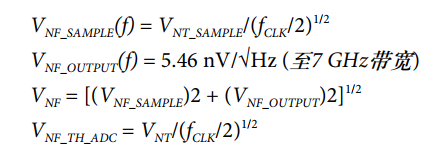

為了估算THA的輸出噪聲譜密度,用戶可以將樣本時域噪聲擴展到一個奈奎斯特帶寬上,并在下游ADC的有效噪聲檢測帶寬上對輸出緩沖器噪聲譜密度進行濾波。因此,必須獲得以下估算結果:

其中,VNT和VNT_x是時域噪聲量,VNF和VNF_x是頻域譜密度。

此計算假定僅測量輸出波形的保持模式部分的頻譜內容。如果ADC以相同時鐘速率對THA波形進行采樣,則在ADC輸入帶寬上發生的總時域噪聲(包括THA輸出端的任何額外輸出濾波)將擴展到一個ADC奈奎斯特區間上。原則上,這些計算可以針對任意時鐘頻率執行。很顯然,THA采樣噪聲占主導地位;因此,輸出濾波的影響和好處是有限的。

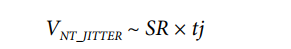

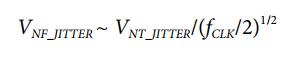

在較高信號頻率下,時鐘和信號的抖動會給采樣噪聲帶來一個額外的噪聲分量。在這種較高時鐘頻率下,抖動噪聲不可忽略,必須包含在總噪聲中。抖動噪聲通常通過引用數據手冊中的抖動規格進行量化,因為抖動產生的噪聲很容易計算,它取決于輸入頻率和抖動值。一般而言,采樣過程中抖動產生的噪聲均方根值近似等于

其中:

SR為采樣點處的信號壓擺率。

tj為均方根抖動。

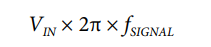

對于正弦信號,壓擺率(SR)峰值通過下式計算:

其中:

VIN為零到峰值信號電平。

fSIGNAL為信號頻率。

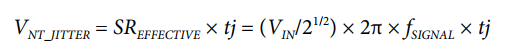

經過統計平均后,用于此計算的有效壓擺率基于VIN的均方根值,有效壓擺率

(SREFFECTIVE) = (VIN/21/2) × 2π × fSIGNAL

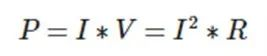

因此,總抖動噪聲(在時域樣本中)為

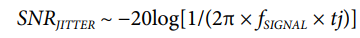

這種不可避免的噪聲分量隨著頻率線性增加。因此,受抖動限制的信噪比(SNR)為

要計算給定頻率時的總噪聲,須將抖動噪聲功率與熱噪聲功率相加。在HMC661LC4B數據手冊中,HMC661LC4B THA中的抖動值< 70 fs,這是僅對THA進行專門抖動測量得到的。在THA和ADC組合測量中測得的典型值與THA單獨測量的結果基本一致,約為65 fs。在給定奈奎斯特采樣間隔中,這種噪聲往往具有相對平坦的頻譜。要降低這種噪聲電平的均值,應使用多個獨立的數據記錄。為了實現這種水平的子系統總抖動,必須使用良好的信號和時鐘發生器并相互鎖相,信號和時鐘發生器的輸出必須進行濾波以消除非諧波雜散信號。

即便最先進的低相位噪聲合成信號發生器,也可能會給采用HMC661LC4B的采樣系統帶來顯著的抖動,特別是當整合信號與時鐘發生器之間的鎖相抖動時。對施加于THA的發生器輸出信號進行帶通濾波,可觀察發生器噪聲引起的抖動的影響。在此情況下,在THA輸出信號和任何經ADC FFT處理的輸出頻譜上可觀察到對應于帶通濾波器帶寬的相位噪聲邊帶。使用較小濾波器帶寬以消除來自發生器的寬帶噪聲,可獲得最佳性能。

此外還必須保持合理的時鐘擺率。對每個時鐘差分半電路輸入使用2 V/ns至4 V/ns,以實現HMC661LC4B數據手冊中說明的抖動性能。如果THA用在ADC之前,則THA決定抖動,ADC的抖動基本可以忽略不計,因為它是對THA輸出的穩定保持波形進行采樣。還可以通過多次記錄求平均或擴頻處理技術來處理抖動噪聲,從而提高SNR。THA抖動噪聲分量同樣分布在一個奈奎斯特區間內,因為它往往是寬帶噪聲。因此,抖動頻譜噪聲密度為

這三個噪聲貢獻(樣本熱噪聲、樣本抖動噪聲和輸出緩沖器噪聲)不具相關性,其功率線性相加。

責任編輯:lq

-

放大器

+關注

關注

143文章

13553瀏覽量

213127 -

濾波器

+關注

關注

160文章

7732瀏覽量

177704 -

噪聲

+關注

關注

13文章

1118瀏覽量

47369

原文標題:【世說設計】你知道嗎?采樣保持輸出噪聲有兩個關鍵分量!

文章出處:【微信號:Excelpoint_CN,微信公眾號:Excelpoint_CN】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ADS8328兩個通道分別采樣兩個電壓,輪流采樣時波動會有40mV左右,怎么解決?

AIC23B兩個音頻信號輸入有噪聲,為什么?

組合兩個 LMX2820 合成器輸出,以改善相位噪聲應用說明

采樣保持輸出噪聲有兩個關鍵分量!

采樣保持輸出噪聲有兩個關鍵分量!

評論