本系列文章主要針對(duì)FPGA初學(xué)者編寫,包括FPGA的模塊書(shū)寫、基礎(chǔ)語(yǔ)法、狀態(tài)機(jī)、RAM、UART、SPI、VGA、以及功能驗(yàn)證等。將每一個(gè)知識(shí)點(diǎn)作為一個(gè)章節(jié)進(jìn)行講解,旨在更快速的提升初學(xué)者在FPGA開(kāi)發(fā)方面的能力,每一個(gè)章節(jié)中都有針對(duì)性的代碼書(shū)寫以及代碼的講解,可作為讀者參考。

18

第十八章:function

function說(shuō)明語(yǔ)句

function說(shuō)明語(yǔ)句的用途就是要返回一個(gè)值,然后把這個(gè)值用在表達(dá)式中。本章講解function任務(wù)的用法。

不同點(diǎn)

任務(wù)和函數(shù)主要的不同點(diǎn)如下:

1、function中不能包含時(shí)序控制語(yǔ)句,而task任務(wù)可以包含時(shí)序控制語(yǔ)句;

2、function不能調(diào)用task任務(wù),而task任務(wù)能調(diào)用function語(yǔ)句;

3、function至少要有一個(gè)input類型的參數(shù),不能有output和inout類型的參數(shù)。而task任務(wù)可以沒(méi)有參數(shù),也可以有多個(gè)類型的參數(shù);

4、function返回一個(gè)值,而task任務(wù)則不返回值。

5、function只能對(duì)輸入值返回一個(gè)結(jié)果值,而task可以支持多種用途,可以計(jì)算并返回多個(gè)結(jié)果值。使用task時(shí),只能通過(guò)output和inout類型的參數(shù)把結(jié)果值傳遞回來(lái)。

function使用語(yǔ)法

定義任務(wù)的語(yǔ)法:

function<返回值的類型或范圍>(函數(shù)名);

<端口說(shuō)明語(yǔ)句>

<變量類型說(shuō)明語(yǔ)句>

begin

<語(yǔ)句1>

<語(yǔ)句2>

………

end

endfunction

函數(shù)通過(guò)關(guān)鍵詞 function 和 endfunction 定義。不允許輸出端口聲明(包括輸出和雙向端口),但可以有多個(gè)輸入端口。<返回值的類型或范圍>指定函數(shù)返回值的類型或位寬,是一個(gè)可選項(xiàng),若沒(méi)有指定,默認(rèn)缺省值為寬度 1 bit的寄存器數(shù)據(jù)。(函數(shù)名)為所定義函數(shù)的名稱,對(duì)函數(shù)的調(diào)用也是通過(guò)函數(shù)名完成的,并在函數(shù)結(jié)構(gòu)體內(nèi)部代表一個(gè)內(nèi)部變量,函數(shù)調(diào)用的返回值就是通過(guò)函數(shù)名變量傳遞給調(diào)用語(yǔ)句。函數(shù)定義在函數(shù)內(nèi)部會(huì)隱式定義一個(gè)寄存器變量,該寄存器變量和函數(shù)同名并且位寬也一致。函數(shù)通過(guò)在函數(shù)定義中對(duì)該寄存器的顯式賦值來(lái)返回函數(shù)計(jì)算結(jié)果。

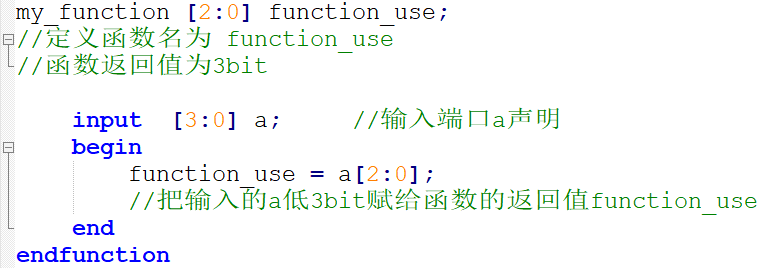

函數(shù)定義示例

函數(shù)的定義聲明了與函數(shù)同名的,函數(shù)內(nèi)部的寄存器。如在函數(shù)的聲明語(yǔ)句中<返回值的類型或范圍>為默認(rèn),則這個(gè)寄存器是1位的。否則是與函數(shù)定義中<返回值的類型或范圍>一致的寄存器。函數(shù)的定義把函數(shù)返回值所賦值寄存器的名稱初始化與函數(shù)同名的內(nèi)部變量。上述代碼示例定義了一個(gè)名為“function_use”的函數(shù),把輸入a的值低3bit賦給了返回值function_use。需要注意的是在函數(shù)定義時(shí)不能包含任何時(shí)間控制語(yǔ)句,即不能包含#,@,wait等。

函數(shù)調(diào)用

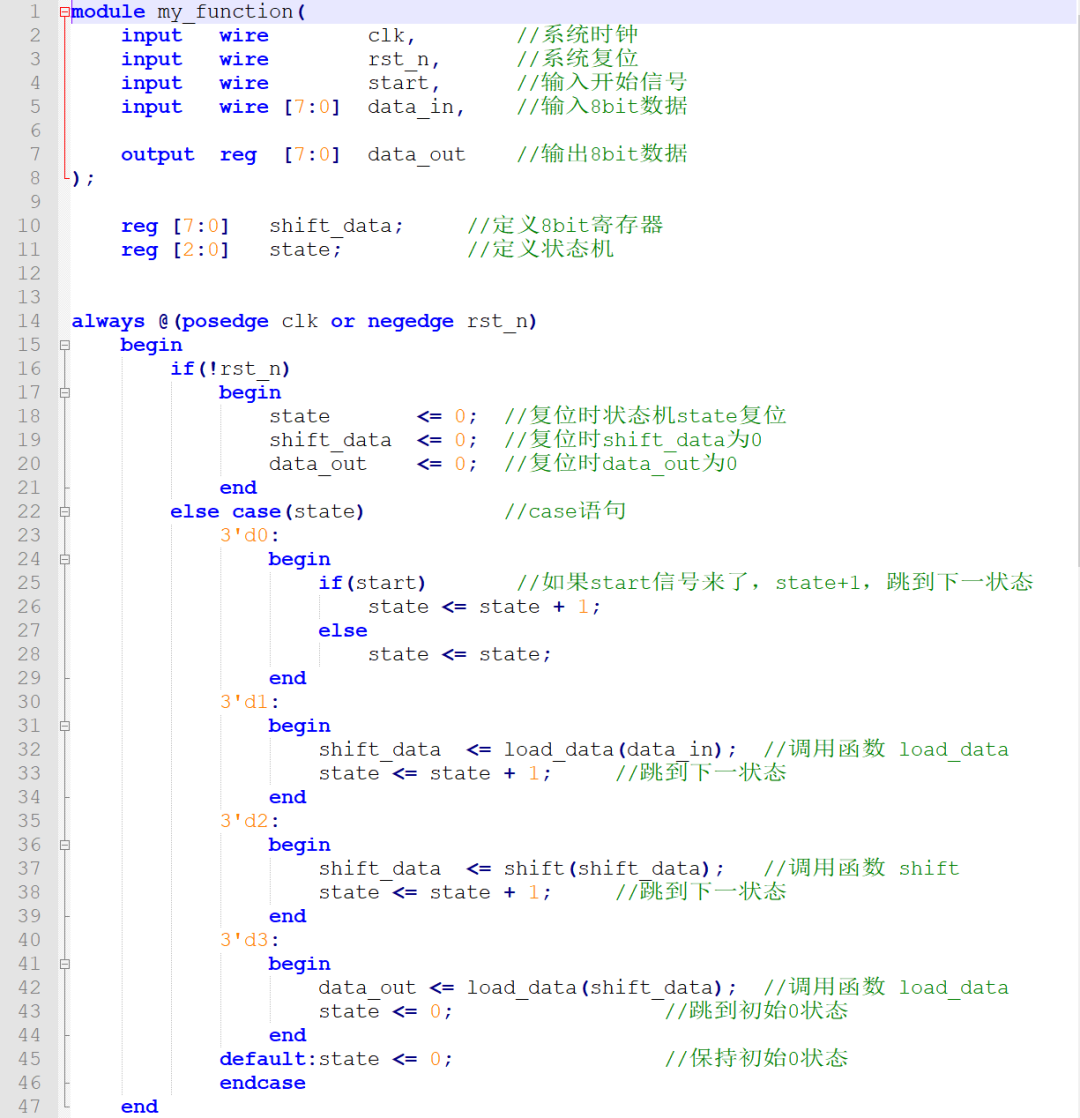

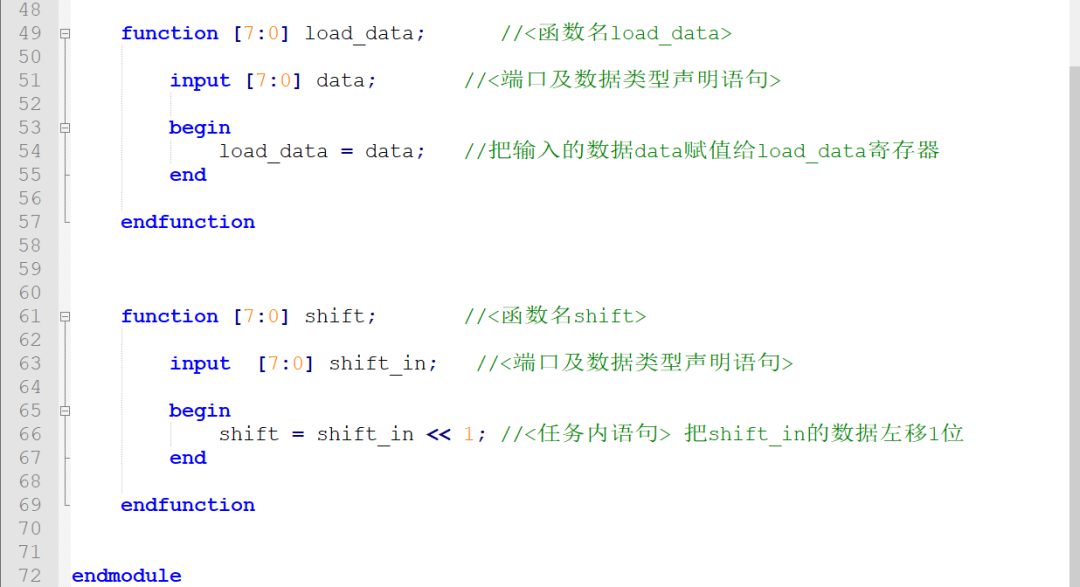

下面舉例說(shuō)明function 函數(shù)的定義與如何調(diào)用。

代碼示例

函數(shù)的調(diào)用時(shí)通過(guò)將函數(shù)作為表達(dá)式中的操作數(shù)來(lái)實(shí)現(xiàn)的。調(diào)用格式如下:

<函數(shù)名> (<表達(dá)式>,……<表達(dá)式>)

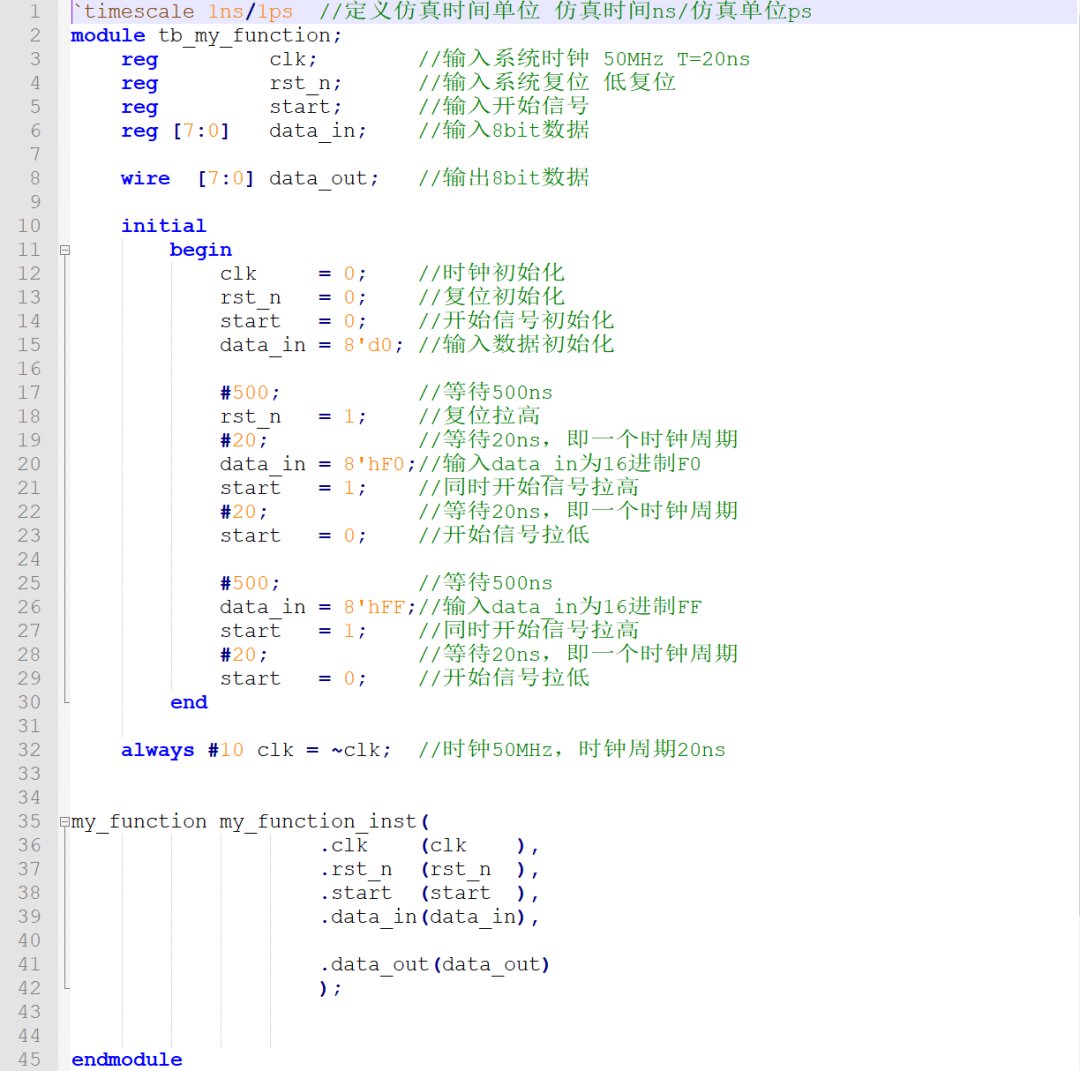

測(cè)試代碼如下:

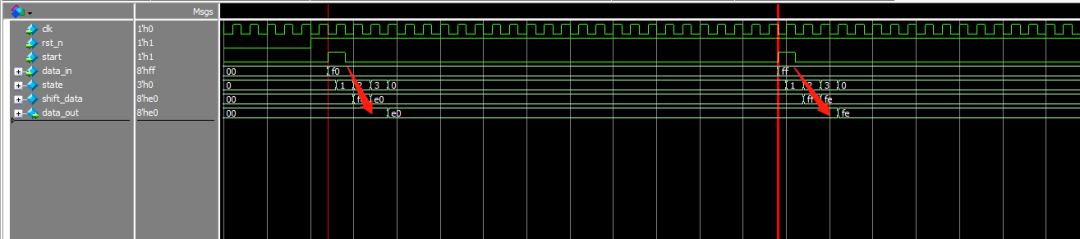

仿真波形如圖所示:

由仿真圖可以看:

1、當(dāng) start 信號(hào)變成高電平的時(shí)候,state 狀態(tài)由 0 跳變到 1 時(shí),此時(shí)調(diào)用 load_data 函數(shù),把 data_in 的值通過(guò)調(diào)用函數(shù)的方式賦給shift_data ,同時(shí)狀態(tài)機(jī)狀態(tài)跳轉(zhuǎn)到 2。

2、當(dāng)狀態(tài)跳轉(zhuǎn)到 2 的時(shí)候,此時(shí)調(diào)用shift 函數(shù),把 shift_data 的值通過(guò)調(diào)用函數(shù)的方式往左移一位后賦給shift_data ,同時(shí)狀態(tài)機(jī)狀態(tài)跳轉(zhuǎn)到 3。

3、當(dāng)狀態(tài)跳到 3 的時(shí)候,調(diào)用 load_data 函數(shù),把 shift_data 的值通過(guò)調(diào)用函數(shù)的方式賦值給data_out ,同時(shí)狀態(tài)機(jī)狀態(tài)跳轉(zhuǎn)到 0。

4、最終結(jié)果:

8‘hF0左移1位,data_out=8‘hE0。

8‘hFF左移1位,data_out=8‘hFE。

責(zé)任編輯:lq

-

FPGA

+關(guān)注

關(guān)注

1620文章

21471瀏覽量

597974 -

Function

+關(guān)注

關(guān)注

0文章

14瀏覽量

9865 -

變量

+關(guān)注

關(guān)注

0文章

604瀏覽量

28237

原文標(biāo)題:FPGA入門系列18--function

文章出處:【微信號(hào):gh_873435264fd4,微信公眾號(hào):FPGA技術(shù)聯(lián)盟】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

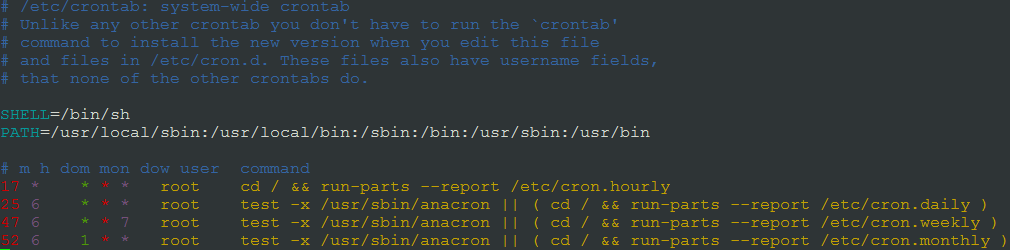

linux定時(shí)任務(wù)的用法總結(jié)

Allegro X 23.11 版本更新 I 原理圖設(shè)計(jì):變體及 function 的創(chuàng)建與管理

講解function任務(wù)的用法

講解function任務(wù)的用法

評(píng)論