一、SERDES介紹

隨著大數(shù)據(jù)的興起以及信息技術(shù)的快速發(fā)展,數(shù)據(jù)傳輸對(duì)總線(xiàn)帶寬的要求越來(lái)越高,并行傳輸技術(shù)的發(fā)展受到了時(shí)序同步困難、信號(hào)偏移嚴(yán)重,抗干擾能力弱以及設(shè)計(jì)復(fù)雜度高等一系列問(wèn)題的阻礙。與并行傳輸技術(shù)相比,串行傳輸技術(shù)的引腳數(shù)量少、擴(kuò)展能力強(qiáng)、采用點(diǎn)對(duì)點(diǎn)的連接方式,而且能提供比并行傳輸更高帶寬,因此現(xiàn)已廣泛用于嵌入式高速傳輸領(lǐng)域。

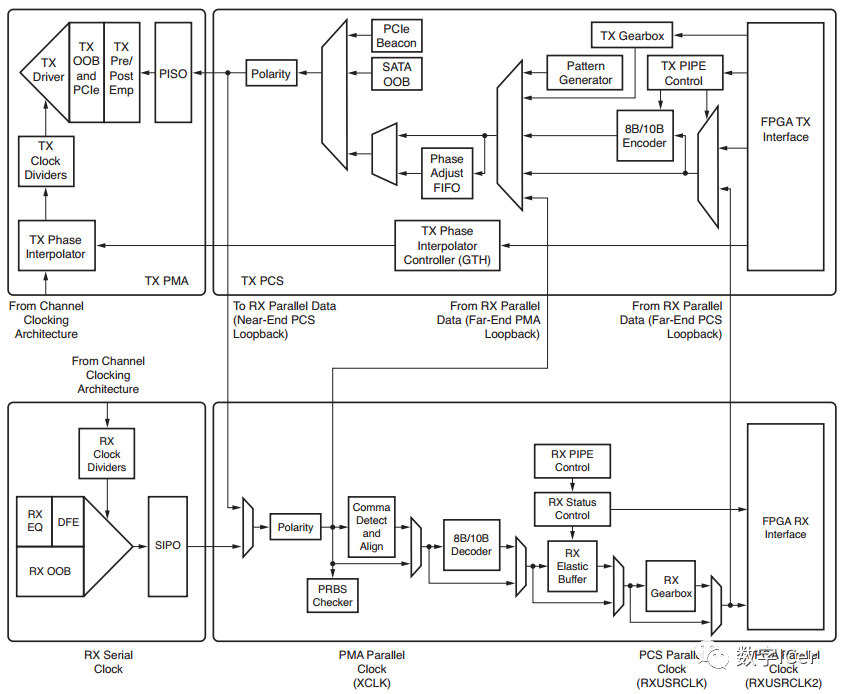

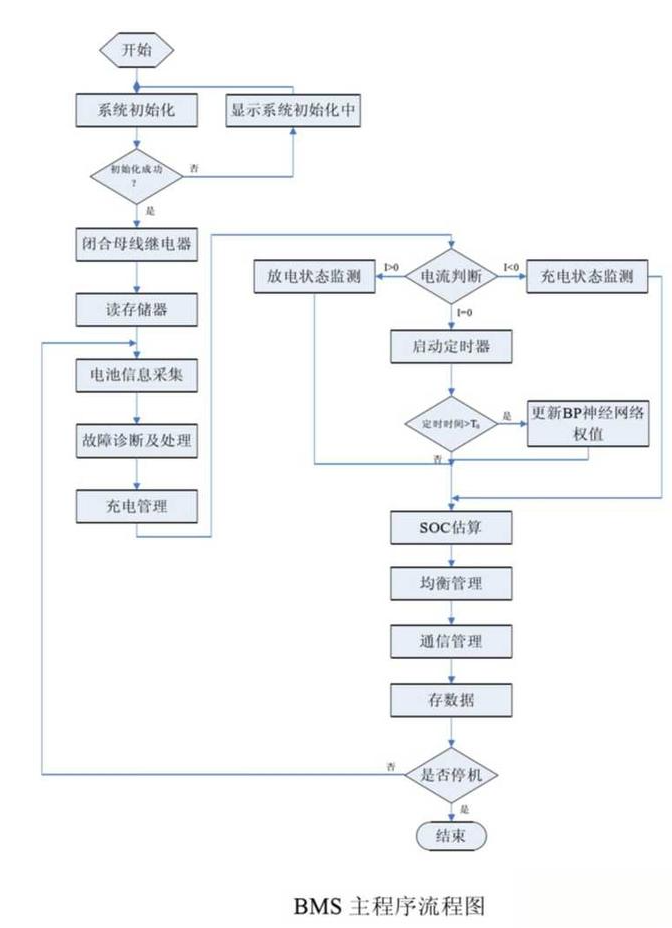

Xilinx公司的許多FPGA已經(jīng)內(nèi)置了一個(gè)或多個(gè)MGT(Multi-Gigabit Transceiver)收發(fā)器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收發(fā)器內(nèi)部包括高速串并轉(zhuǎn)換電路、時(shí)鐘數(shù)據(jù)恢復(fù)電路、數(shù)據(jù)編解碼電路、時(shí)鐘糾正和通道綁定電路,為各種高速串行數(shù)據(jù)傳輸協(xié)議提供了物理層基礎(chǔ)。MGT收發(fā)器的TX發(fā)送端和RX接收端功能獨(dú)立,而且均由物理媒介適配層(Physical Media Attachment,PMA)和物理編碼子層(Physical Coding Sublayer,PCS)兩個(gè)子層組成,結(jié)構(gòu)如下圖所示

PMA子層內(nèi)部集成了高速串并轉(zhuǎn)換電路,預(yù)加重電路、接收均衡電路、時(shí)鐘發(fā)生電路和時(shí)鐘恢復(fù)電路。串并轉(zhuǎn)換電路的作用是把FPGA內(nèi)部的并行數(shù)據(jù)轉(zhuǎn)化為MGT接口的串行數(shù)據(jù)。預(yù)加重電路是對(duì)物理連接系統(tǒng)中的高頻部分進(jìn)行補(bǔ)償,在發(fā)送端增加一個(gè)高通濾波器來(lái)放大信號(hào)中的高頻分量進(jìn)而提高信號(hào)質(zhì)量,但預(yù)加重電路會(huì)導(dǎo)致功耗和電磁兼容(Electro Magnetic Compatibility,EMC)增加,所以如非必要一般情況下都把它屏蔽掉。接收均衡電路主要用來(lái)補(bǔ)償由頻率不同引起的阻抗差異。時(shí)鐘發(fā)生電路與時(shí)鐘恢復(fù)電路在發(fā)送端把時(shí)鐘和數(shù)據(jù)綁定后發(fā)送,在接收端再?gòu)慕邮盏降臄?shù)據(jù)流中恢復(fù)出時(shí)鐘,這樣可以有效地避免在高速串行傳輸?shù)臈l件下時(shí)鐘與數(shù)據(jù)分開(kāi)傳輸帶來(lái)的時(shí)鐘抖動(dòng)問(wèn)題。

PCS子層內(nèi)部集成了8B/10B編/解碼電路、彈性緩沖電路、通道綁定電路和時(shí)鐘修正電路。8B/10B編/解碼電路可以有效的避免數(shù)據(jù)流中出現(xiàn)連續(xù)的‘0’或者‘1’,以保證數(shù)據(jù)傳輸?shù)钠胶庑浴Mǖ澜壎娐返淖饔檬峭ㄟ^(guò)在發(fā)送數(shù)據(jù)流中加入K碼字符,把多個(gè)物理上獨(dú)立的MGT通道綁定成一個(gè)時(shí)序邏輯上同步的并行通道進(jìn)而提高傳輸?shù)耐掏侣省椥跃彌_電路用來(lái)解決恢復(fù)的時(shí)鐘與本地時(shí)鐘不一致的問(wèn)題并可以通過(guò)對(duì)緩沖區(qū)中的K碼進(jìn)行匹配對(duì)齊來(lái)實(shí)現(xiàn)通道綁定功能。

下面將詳細(xì)討論SERDES用到的各種關(guān)鍵技術(shù)。

二、SERDES關(guān)鍵技術(shù)

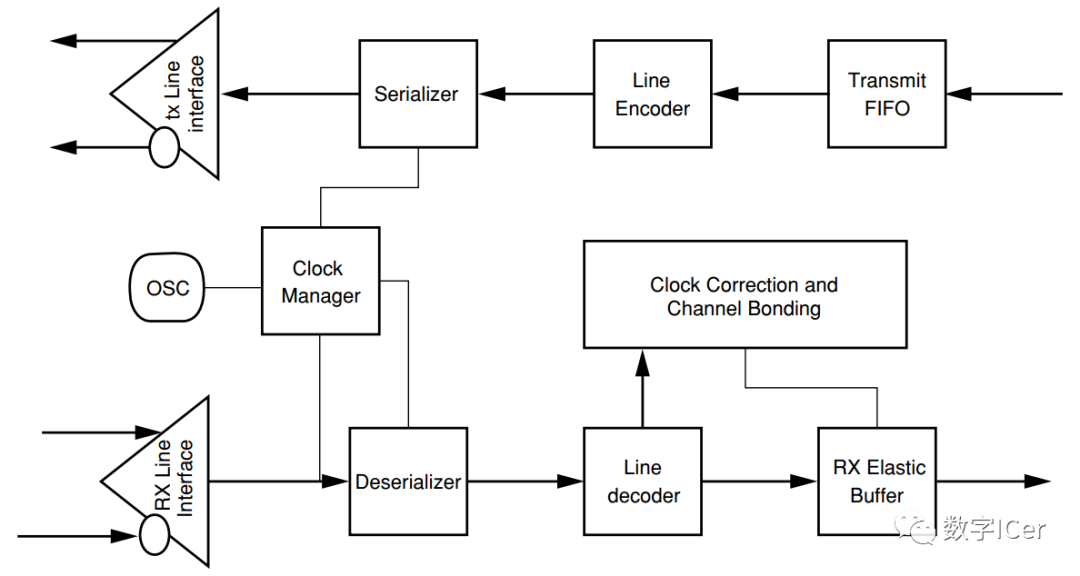

簡(jiǎn)化的SERDES結(jié)構(gòu)圖如下圖所示

SERDES的優(yōu)勢(shì)在于其帶寬很高,引腳數(shù)目較少而且支持目前多種主流的工業(yè)標(biāo)準(zhǔn),比如Serial RapidIO ,F(xiàn)iberChannel(FC),PCI-Express(PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。它的線(xiàn)速度能達(dá)到10Gb/s甚至更高,主要原因是因?yàn)樗捎昧硕喾N技術(shù)來(lái)實(shí)現(xiàn)這些功能。

2.1 多重相位技術(shù)

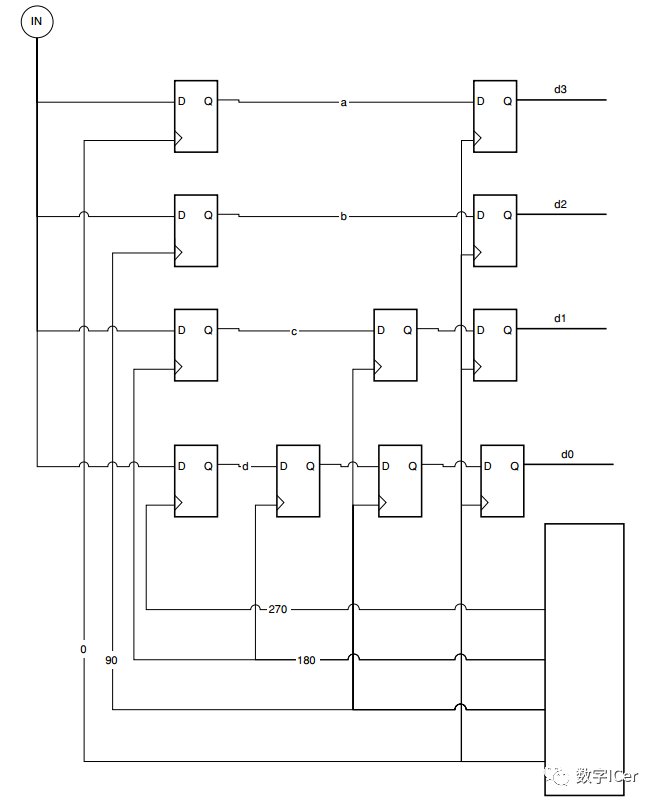

如果輸入的串行數(shù)據(jù)流比特率為x, 那么可以使用多重相位以x/4的低速時(shí)鐘來(lái)重新組織數(shù)據(jù)流。輸入的數(shù)據(jù)流直接連接到4個(gè)觸發(fā)器,每一個(gè)觸發(fā)器運(yùn)行在時(shí)鐘的不同相位上(0、90、180以及270)。多重相位技術(shù)的數(shù)據(jù)提取電路如下圖所示

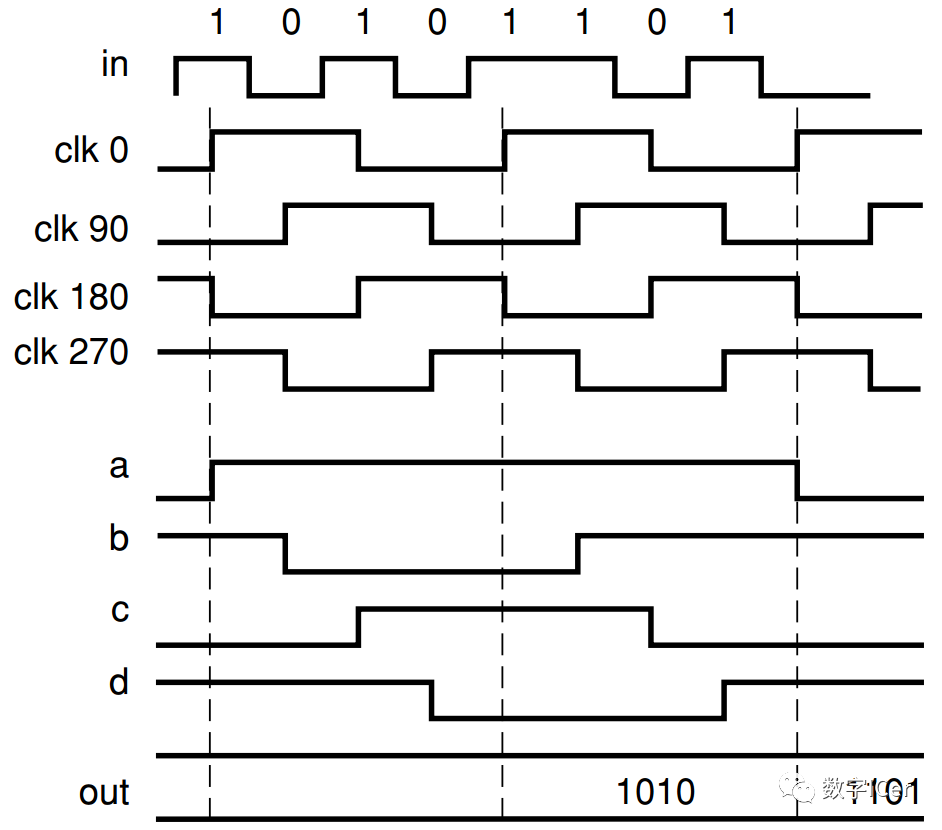

對(duì)應(yīng)的時(shí)序圖如下圖所示

每個(gè)觸發(fā)器的輸出連接到時(shí)鐘相位小90度的觸發(fā)器,直到到達(dá)時(shí)鐘相位為0 的觸發(fā)器。這樣,輸入數(shù)據(jù)流就被分解成了1/4輸入速率, 4bit寬度的并行數(shù)據(jù)流。

在上述的示例電路中,相位等差排列,時(shí)鐘頻率嚴(yán)格等于輸入數(shù)據(jù)流速率的1/4。怎樣才能實(shí)現(xiàn)呢?我們必須和輸入的數(shù)據(jù)流保持鎖定。我們可以使用典型的鎖相環(huán)來(lái)實(shí)現(xiàn)這一點(diǎn),但是鎖相環(huán)需要一個(gè)全速率的時(shí)鐘,這是很難滿(mǎn)足的。鎖相環(huán)是高速SERDES設(shè)計(jì)中最重大的改進(jìn)之一,它主要用于時(shí)鐘和數(shù)據(jù)恢復(fù)。一般的鎖相環(huán)需要有運(yùn)行在數(shù)據(jù)速率上的時(shí)鐘,不過(guò)可以通過(guò)多種技術(shù)來(lái)避免這種要求,包括分?jǐn)?shù)鑒相器、多重相位鎖相環(huán)、并行采樣以及過(guò)采樣數(shù)據(jù)恢復(fù)。

2.2 線(xiàn)路編解碼技術(shù)

線(xiàn)路編碼機(jī)制將輸入的原始數(shù)據(jù)轉(zhuǎn)變成接收器可以接收的格式,并保證有足夠的切換提供給時(shí)鐘恢復(fù)電路。編碼器還提供一種將數(shù)據(jù)對(duì)齊到字的方法,同時(shí)線(xiàn)路可以保持良好的直流平衡。線(xiàn)路編碼機(jī)制也可選擇用來(lái)實(shí)現(xiàn)時(shí)鐘修正、塊同步、通道綁定和將帶寬劃分到子通道。線(xiàn)路編碼機(jī)制主要有兩種方式,分別為數(shù)值查找機(jī)制和擾碼機(jī)制。

2.2.1 8B/10B編解碼

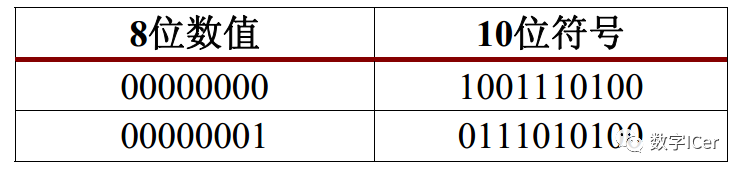

8b/10b編碼機(jī)制是由IBM開(kāi)發(fā)的,已經(jīng)被廣泛采用。8b/10b編碼機(jī)制是Infiniband,千兆位以太網(wǎng), FiberChannel以及XAUI 10G以太網(wǎng)接口采用的編碼機(jī)制。它是一種數(shù)值查找類(lèi)型的編碼機(jī)制,可將8位的字轉(zhuǎn)化為10位符號(hào)。這些符號(hào)可以保證有足夠的跳變用于時(shí)鐘恢復(fù)。下表是兩個(gè)8-bit數(shù)據(jù)編碼為10-bit數(shù)據(jù)的例子。

在上面的例子中8-bit數(shù)據(jù)會(huì)導(dǎo)致線(xiàn)路很長(zhǎng)時(shí)間不出現(xiàn)切換而丟失同步信息。所以8B/10B編解碼電路采用了一種叫做運(yùn)行不一致(Running Disparity)的技術(shù)來(lái)保證線(xiàn)路良好的直流平衡性能。

2.2.2 運(yùn)行不一致(Running Disparity)

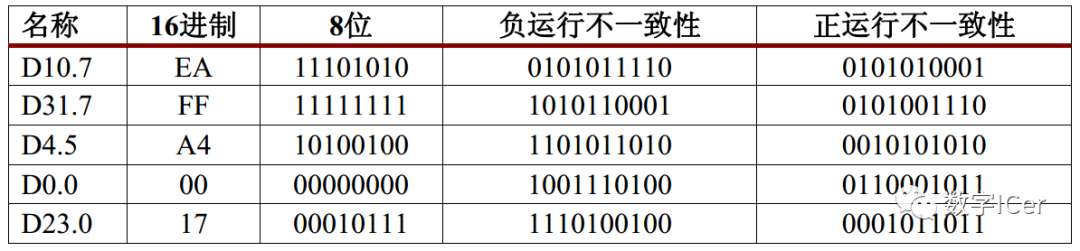

8B/10B編解碼機(jī)制中的直流平衡是通過(guò)一種稱(chēng)作“運(yùn)行不一致性”的方法來(lái)實(shí)現(xiàn)的。實(shí)現(xiàn)直流平衡的最簡(jiǎn)單辦法是:只使用有相同個(gè)數(shù)0和1的符號(hào),但是這將限制符號(hào)的數(shù)量。而8B/10B則為各個(gè)數(shù)值分配了兩個(gè)不同的符號(hào)。其中一個(gè)符號(hào)有6個(gè)0和4個(gè)1,這種情況稱(chēng)為正運(yùn)行不一致符號(hào),簡(jiǎn)寫(xiě)為RD+,另一個(gè)符號(hào)則有4個(gè)0和6個(gè)1,這種情況稱(chēng)為負(fù)運(yùn)行不一致符號(hào),簡(jiǎn)寫(xiě)為RD-。編碼器會(huì)檢測(cè)0和1的數(shù)量,并根據(jù)需求選擇下一個(gè)符號(hào),以保證線(xiàn)路的直流平衡。下表給出了一些符號(hào)示例

“運(yùn)行不一致性”技術(shù)的另一個(gè)優(yōu)點(diǎn)是如果數(shù)據(jù)違反了運(yùn)行不一致性規(guī)則,那么接收器可以通過(guò)監(jiān)控輸入數(shù)據(jù)的運(yùn)行不一致性規(guī)則來(lái)檢測(cè)數(shù)據(jù)中的錯(cuò)誤。

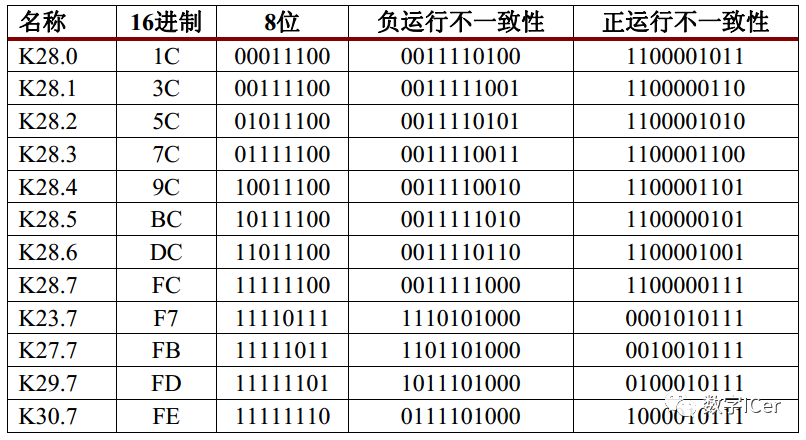

2.2.3 控制字符(Control Characters)

8B/10B編解碼技術(shù)將12個(gè)特殊字符編碼成12個(gè)控制字符,通常也稱(chēng)作“K”字符。這些控制字符用于數(shù)據(jù)對(duì)齊,控制以及將帶寬劃分成為子通道。下表是12種控制字符的編碼情況

2.2.4 Comma檢測(cè)

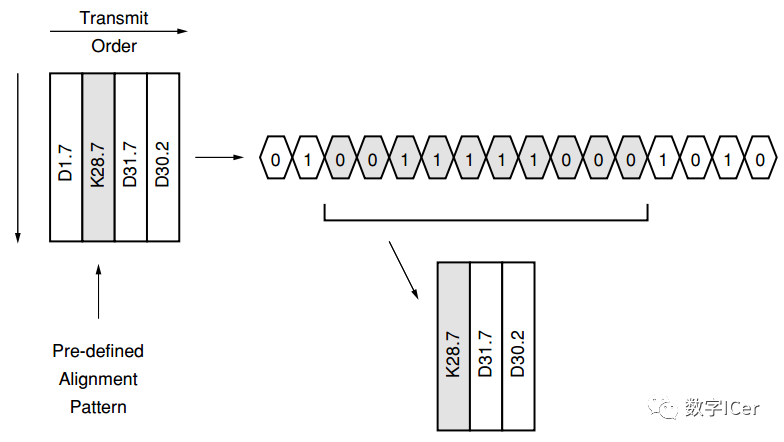

Comma指的是用于對(duì)齊序列的一個(gè)7-bit符號(hào)。數(shù)據(jù)的對(duì)齊是解串器的一項(xiàng)重要功能,下圖給出了串行流中的有效8B/10B數(shù)據(jù)示例。

在Serdes中,數(shù)據(jù)被Comma序列隔開(kāi),Comma序列可以自行設(shè)置,也可以預(yù)先定義好。接收器在輸入數(shù)據(jù)流中掃描搜尋特定的比特序列。如果找到序列,解串器調(diào)整字符邊界以匹配檢測(cè)到的Comma字符序列。掃描是連續(xù)進(jìn)行的,一旦對(duì)齊確定,所有后續(xù)的Comma字符均會(huì)發(fā)現(xiàn)對(duì)齊已經(jīng)確定。當(dāng)然,在任意的序列組合里comma字符序列必須是唯一的。

例如,如果我們使用符號(hào)K28.7作為Comma字符,則我們必須確保任意有序符號(hào)集xy中都不包含比特序列K28.7。使用預(yù)定義協(xié)議時(shí)是不會(huì)出現(xiàn)這個(gè)問(wèn)題的,因?yàn)镃omma字符都是已經(jīng)定義好的。

常用的K字符是全部控制字符中的一個(gè)或多個(gè)特定子集。這些子集中包含K28.1,K28.5,K28.7,這些字符的頭7位都是1100000。這種比特序列模式只可以在這些控制字符中出現(xiàn)。其他任意的字符序列或者其他K字符都不包含這一比特序列。因此,這些控制字符是非常理想的對(duì)齊序列。在使用自定義協(xié)議的情況下,最安全且最常用的解決方案是從比較著名的協(xié)議中“借”一個(gè)序列。千兆位以太網(wǎng)使用K28.5作為Comma字符。鑒于這個(gè)原因,盡管在技術(shù)上還有其他的選擇,這個(gè)字符還是經(jīng)常被當(dāng)作Comma字符。

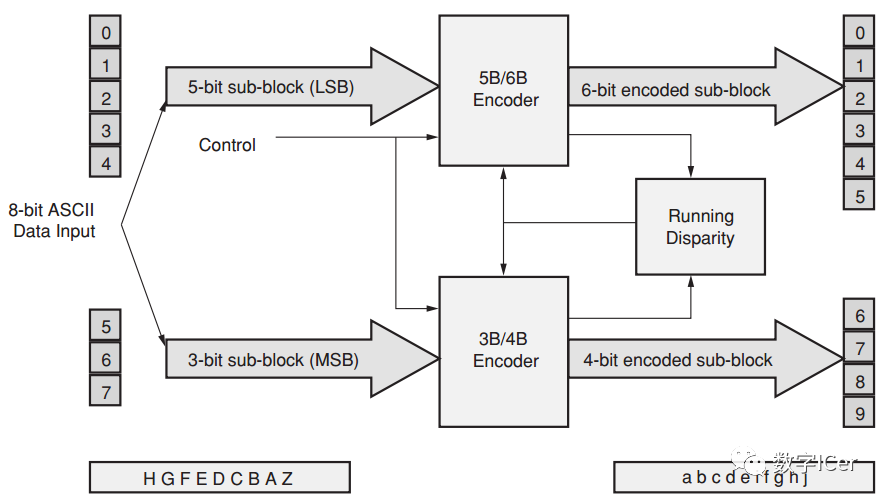

控制字符的命名方式源于編碼器和解碼器構(gòu)建方式,例如:D0.3和K28.5,下圖描述了這種方法。

輸入的8位比特被分成5位和3位的數(shù)據(jù)分別進(jìn)行5B/6B編碼和3B/4B編碼,這就是其名字的來(lái)源。舉例說(shuō)明, Dx.y表示最低5位的數(shù)值對(duì)應(yīng)十進(jìn)制值x,而最高3位的數(shù)值對(duì)應(yīng)十進(jìn)制值y的輸入字節(jié)。字母D表示數(shù)據(jù)字符,而字母K表示控制字符。另一種命名方式中, 8位比特對(duì)應(yīng)于HGF EDCBA,而10位比特對(duì)應(yīng)于abcdei fghj。開(kāi)銷(xiāo)是8b/10b機(jī)制的一個(gè)缺陷。為了獲得2.5Gbit的帶寬,需要3.125Gb/s的線(xiàn)路速率。但使用擾碼技術(shù)可以很容易地解決時(shí)鐘發(fā)送和直流偏置問(wèn)題,并且不需要額外的帶寬。

2.2.4 擾碼(Scrambling)

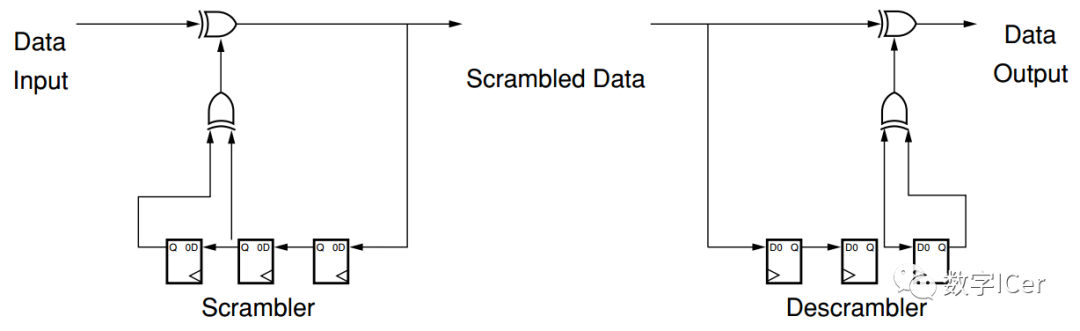

擾碼是一種將數(shù)據(jù)重新排列或者進(jìn)行編碼以使其隨機(jī)化的方法,但是必須能夠解擾恢復(fù)。我們希望打亂長(zhǎng)的連0和長(zhǎng)的連1序列,將數(shù)據(jù)隨機(jī)化。顯然,我們希望解擾器在解擾時(shí)不需要額外的對(duì)齊信息。具有這種特性的碼稱(chēng)作自同步碼。

一個(gè)簡(jiǎn)單的擾碼器包含一組排列好的觸發(fā)器,用于移位數(shù)據(jù)流。大部分的觸發(fā)器只需要簡(jiǎn)單地輸出下一個(gè)比特即可,但是某些觸發(fā)器需要和數(shù)據(jù)流中的歷史比特相與或者相或。下圖描述了此概念。

擾碼方法通常是伴隨著多項(xiàng)式出現(xiàn)的,因?yàn)閿_碼的數(shù)學(xué)原理中使用了多項(xiàng)式。多項(xiàng)式的選擇通常是基于擾碼的特性,包括生成數(shù)據(jù)的隨機(jī)度,以及打亂長(zhǎng)的連0、連1的能力。擾碼必須避免生成長(zhǎng)的連0或連1序列。

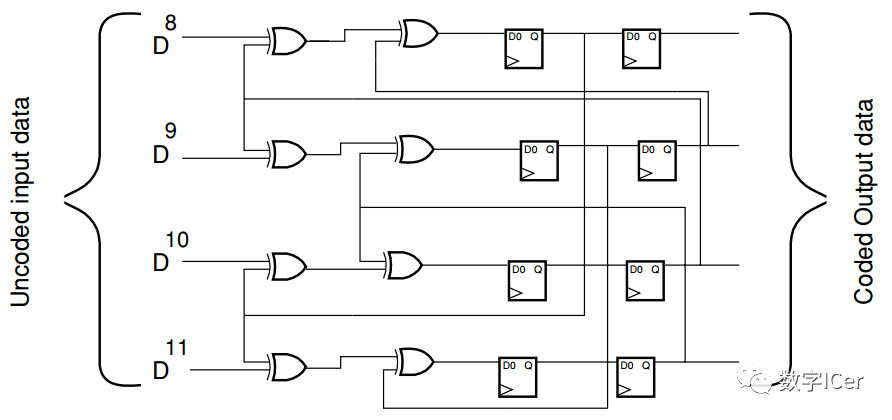

我們希望能夠加快觸發(fā)器的時(shí)鐘速率。但是想要達(dá)到諸如10Gb/s的高速率不是能輕易辦到的。但是,還是有方法可以將任意形式的串行數(shù)據(jù)并行化為y位寬度的并行數(shù)據(jù),從而加快進(jìn)程。如下圖所示。

擾碼器消除了長(zhǎng)連0、連1序列以及其他會(huì)對(duì)接收器接收能力有負(fù)面影響的序列。但是線(xiàn)路編碼機(jī)制(例如:8B/10B)的其他功能不是由擾碼器提供的,包括:

1、 字對(duì)齊(Word Alignment)

2、 時(shí)鐘修正機(jī)制(Clock Correction Mechanism)

3、 通道綁定機(jī)制(Channel Bonding Mechanism)

4、 子通道生成(Sub-Channel Creation)

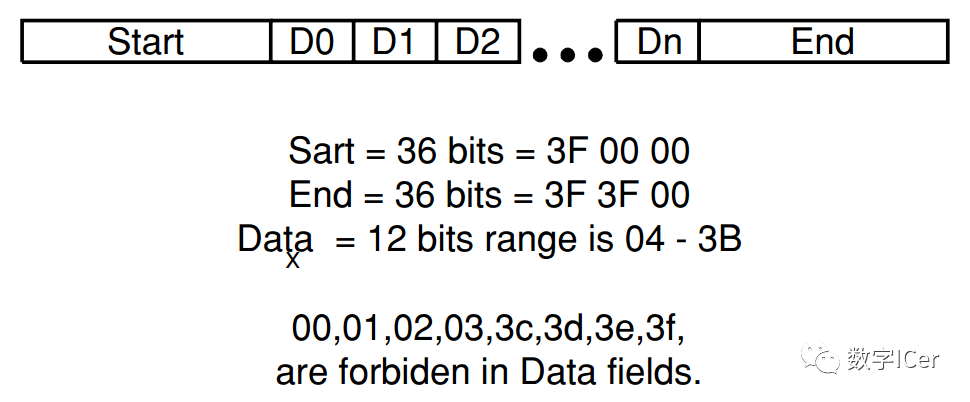

某些情況下后三種功能可能是不需要的,而字對(duì)齊通常是必要的。如果線(xiàn)路編碼使用了擾碼,那么字對(duì)齊也必須采用相應(yīng)的方法。例如,我們可以將某些數(shù)值排除在容許的數(shù)據(jù)(或者有效載荷)數(shù)值之外。此后,我們可以使用這些禁用的值來(lái)創(chuàng)建一個(gè)比特流,這個(gè)比特流不會(huì)在序列的數(shù)據(jù)部分中出現(xiàn)。如下圖所示

通常,因?yàn)榇嬖诓辉试S的數(shù)值,所以需要設(shè)計(jì)數(shù)據(jù)流中不能出現(xiàn)連0或連1的長(zhǎng)度。長(zhǎng)的連0、連1會(huì)被擾碼器打亂,并在解擾時(shí)進(jìn)行恢復(fù)。接收數(shù)據(jù)流的解擾邏輯在數(shù)據(jù)流中搜尋這些符號(hào)并對(duì)齊數(shù)據(jù)。類(lèi)似的技術(shù)還可用于建立其他特性。

2.2.5 4B/5B與64B/66B編解碼技術(shù)

4B/5B和8B/10B是類(lèi)似的。顧名思義,這種機(jī)制將4個(gè)比特編碼成5個(gè)比特。4B/5B的編碼器和解碼器要比8B/10B簡(jiǎn)單一些。4B/5B的控制字符要少一些,并且不能處理直流平衡和運(yùn)行不一致性問(wèn)題。由于編碼開(kāi)銷(xiāo)相同但是功能卻比較少,所以4B/5B編碼機(jī)制并不經(jīng)常使用。它的最大優(yōu)勢(shì)是設(shè)計(jì)的尺寸,不過(guò)隨著邏輯門(mén)價(jià)格的降低這個(gè)優(yōu)勢(shì)也不再明顯。4B/5B仍用在各種標(biāo)準(zhǔn)中,包括低速率版本的FiberChannel、音頻工程協(xié)會(huì)-10(AES-10)以及多通道數(shù)字音頻接口(MADI,一種數(shù)字音頻復(fù)接標(biāo)準(zhǔn))。

還有一種新的編碼方式稱(chēng)作64B/66B 。我們可以認(rèn)為64B/66B是8B/10B的簡(jiǎn)化版本,它具有更低的編碼開(kāi)銷(xiāo),但是實(shí)現(xiàn)細(xì)節(jié)相當(dāng)不同。在現(xiàn)有的技術(shù)用戶(hù)需求下,人們開(kāi)發(fā)出了64B/66B機(jī)制。10G以太網(wǎng)協(xié)會(huì)要求實(shí)現(xiàn)基于以太網(wǎng)的10Gb/s通信。他們可以通過(guò)使用4條有效載荷速率為2.5Gb/s、線(xiàn)路速率為3.125Gb/s的鏈路來(lái)實(shí)現(xiàn),但此時(shí)SERDES已經(jīng)可以在單個(gè)鏈路上實(shí)現(xiàn)10Gb的解決方案。此時(shí)新型SERDES的運(yùn)行速率已經(jīng)可以略高于10Gb/s了,但還不能達(dá)到12.5Gb/s以支持8B/10B的開(kāi)銷(xiāo)。

更多的64B/66B編解碼技術(shù)的實(shí)現(xiàn)細(xì)節(jié)請(qǐng)查看參考文獻(xiàn)1。

2.3 包傳輸技術(shù)

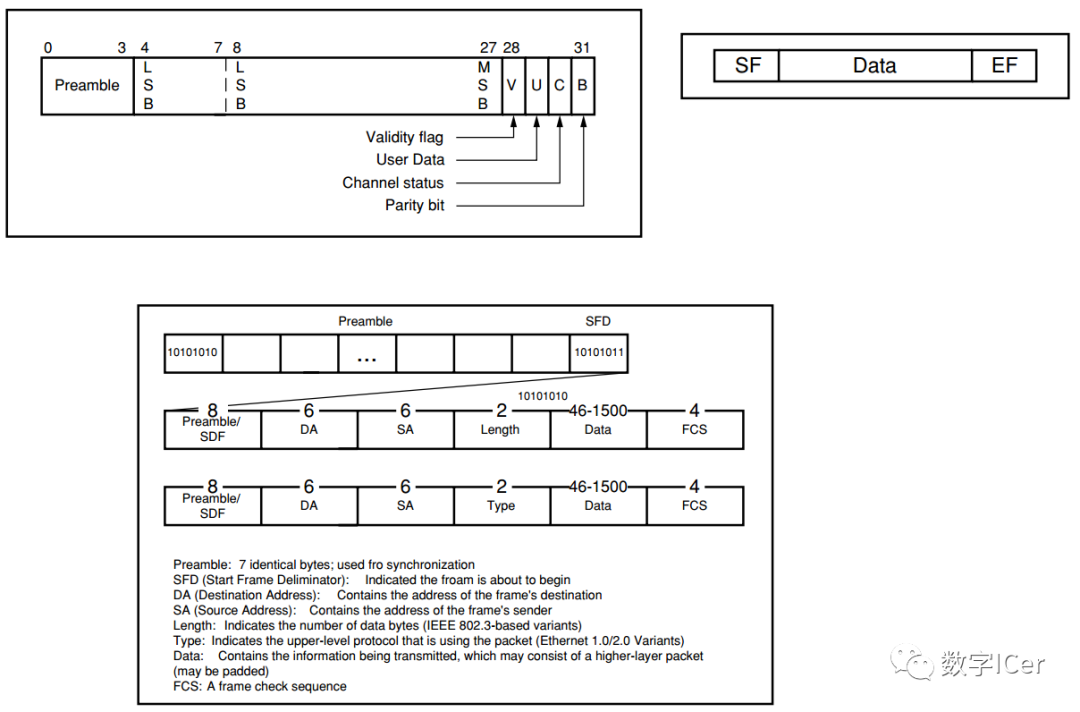

包是一種確切定義的字節(jié)集合,包括頭部、數(shù)據(jù)和尾部。

注意,定義中沒(méi)有包括源地址和目的地址、 CRC校驗(yàn)碼、最小長(zhǎng)度、或者開(kāi)放系統(tǒng)互連協(xié)議層。包只不過(guò)是一個(gè)定義了起點(diǎn)和終點(diǎn)的數(shù)據(jù)結(jié)構(gòu)。局域網(wǎng)的包通常有很多特性,但是其他用途的包則通常要簡(jiǎn)單得多。

包用于各種場(chǎng)合下的信息傳遞。例如汽車(chē)動(dòng)力布線(xiàn)、手機(jī)以及家庭娛樂(lè)中心等等。但是,包和千兆位串行鏈路有什么關(guān)系呢?

通過(guò)千兆位串行鏈路傳輸?shù)臄?shù)據(jù)多數(shù)都是嵌入在某種類(lèi)型的包中的。Serdes自然需要一種將輸入的數(shù)據(jù)流對(duì)齊成字的方法。如果系統(tǒng)需要時(shí)鐘修正,還必須發(fā)送特殊的比特序列或者Comma字符。Comma字符是指示幀的開(kāi)始和結(jié)束的天然標(biāo)識(shí)。如果需要時(shí)鐘修正,時(shí)鐘修正序列常常是比較理想的字符。加入有序集合用于指示包的開(kāi)始、結(jié)束以及包的特殊類(lèi)型之后,我們就有了一個(gè)簡(jiǎn)單而又強(qiáng)大的傳輸通道。

idle符號(hào)或序列是包的概念的另一要點(diǎn)。如果沒(méi)有信息需要發(fā)送,則發(fā)送idle符號(hào)。數(shù)據(jù)的連續(xù)傳輸保證鏈路能夠維持對(duì)齊,同時(shí)PLL可以保持恢復(fù)時(shí)鐘鎖定。下圖給出了一些不同標(biāo)準(zhǔn)的包格式。

2.4 參考時(shí)鐘要求

千兆位級(jí)收發(fā)器的輸入時(shí)鐘、或是參考時(shí)鐘的規(guī)格定義是非常嚴(yán)格的。其中包含非常嚴(yán)格的頻率要求,通常用每百萬(wàn)次容許頻率錯(cuò)誤的單位PPM來(lái)定義。抖動(dòng)要求也是十分嚴(yán)格的,通常用時(shí)間(皮秒)或者時(shí)間間隔(UI)定義。

如此嚴(yán)格的規(guī)定才使得PLL和時(shí)鐘提取電路能夠正常工作。通常系統(tǒng)的每一個(gè)印刷電路板都需要有一個(gè)精確石英晶體振蕩器供MGT使用。這些晶體振蕩器的精確度比大多數(shù)用在數(shù)字系統(tǒng)中的晶體振蕩器要高一個(gè)級(jí)別,而且價(jià)格也要高出一截。很多情況下,一般的時(shí)鐘發(fā)生芯片和PLL因?yàn)閹в泻艽蟮亩秳?dòng),而不能用于MGT。

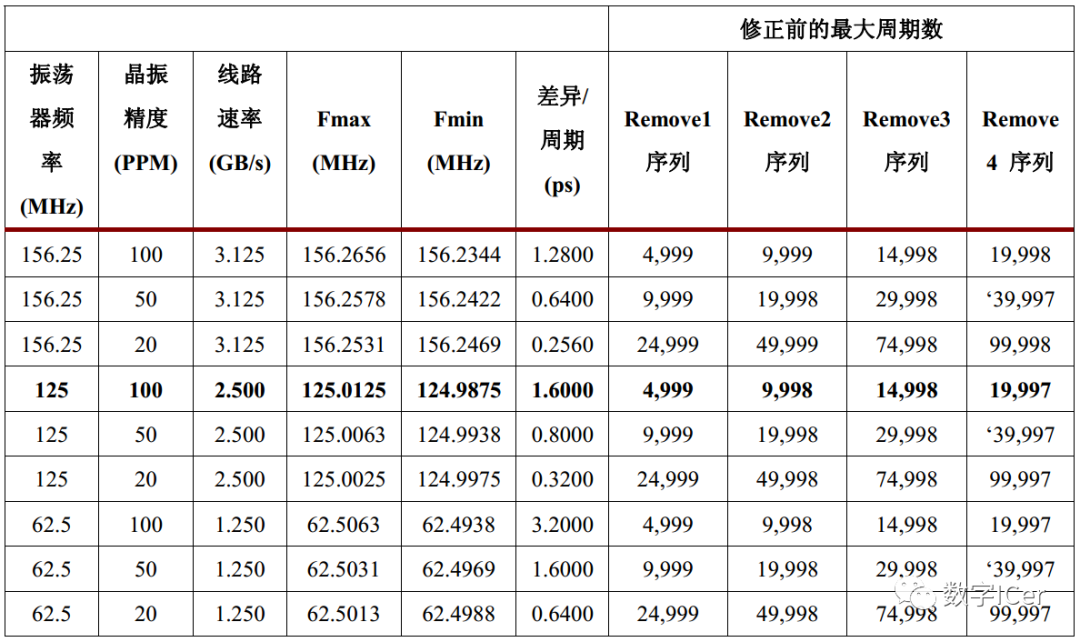

2.5 時(shí)鐘修正技術(shù)

千兆位Serdes對(duì)傳輸時(shí)鐘有非常嚴(yán)格的抖動(dòng)要求,所以通常不能將恢復(fù)時(shí)鐘作為傳輸時(shí)鐘。每一個(gè)PCB集合都有唯一的振蕩器和唯一的頻率。如果兩個(gè)1GHz的振蕩器僅僅有1PPM的頻差,同時(shí)提供1/20th的參考時(shí)鐘,則數(shù)據(jù)流的時(shí)鐘每秒鐘可能會(huì)增加或者缺失20,000個(gè)周期。因此,在8B/10B編碼的系統(tǒng)中,每秒將會(huì)額外增加或者損失2萬(wàn)個(gè)符號(hào)。

大多數(shù)的Serdes都有時(shí)鐘修正功能。時(shí)鐘修正需要使用唯一的符號(hào)或者符號(hào)序列,它們?cè)跀?shù)據(jù)流中是不會(huì)出現(xiàn)的。因?yàn)闀r(shí)鐘修正是對(duì)齊的后續(xù)處理,所以可以比較容易地通過(guò)保留一個(gè)K字符、或者一組有序的K字符、或者一個(gè)時(shí)鐘修正數(shù)據(jù)序列來(lái)實(shí)現(xiàn)。

某些情況需要使用4個(gè)符號(hào)的時(shí)鐘修正序列。時(shí)鐘修正通過(guò)檢測(cè)接收FIFO來(lái)完成其工作。如果FIFO接近于滿(mǎn),則查找下一個(gè)時(shí)鐘修正序列而不將數(shù)據(jù)序列寫(xiě)入FIFO。這種操作稱(chēng)作丟棄。相反地,如果FIFO接近于空,則查找下一個(gè)時(shí)鐘修正序列,同時(shí)它會(huì)被兩次寫(xiě)入FIFO。這種操作通常也稱(chēng)作重復(fù)。

時(shí)鐘修正進(jìn)行的頻數(shù)必須足夠多,從而可以通過(guò)丟棄或者重復(fù)來(lái)補(bǔ)償時(shí)鐘的差異。時(shí)鐘修正序列和idle序列通常也是一樣的。

有些系統(tǒng)并不需要時(shí)鐘修正。例如,在很多芯片到芯片(chip-to-chip) 的應(yīng)用中,同一個(gè)振蕩器為所有收發(fā)器提供參考時(shí)鐘。相同的參考時(shí)鐘和相同的速率意味著不需要進(jìn)行時(shí)鐘修正。同樣,如果所有接收電路的時(shí)鐘都來(lái)自恢復(fù)時(shí)鐘,那么時(shí)鐘修正也是不需要的。如果FIFO的寫(xiě)入速率和讀出速率相等,也沒(méi)有必要進(jìn)行時(shí)鐘修正。

如果所有的傳輸參考時(shí)鐘都是通過(guò)一個(gè)外部的PLL鎖定在一個(gè)公共的參考頻率上,那么也不需要時(shí)鐘修正。對(duì)于高精確度的串行數(shù)字視頻鏈路來(lái)說(shuō),這是常用的一種結(jié)構(gòu)。所有的傳輸時(shí)鐘都是從一個(gè)公共的視頻參考中獲取的。無(wú)法鎖定到這個(gè)信號(hào)往往將導(dǎo)致自由滑動(dòng)的視頻流,相對(duì)于其他的鎖定信號(hào)。在1G或2G速率上實(shí)現(xiàn)是比較簡(jiǎn)單的,但是設(shè)計(jì)一個(gè)能夠用于10Gb鏈路且有足夠精度的參考時(shí)鐘是非常有挑戰(zhàn)性的。

下表給出了在不同晶振頻率和晶振精度下時(shí)鐘修正序列之間的最大時(shí)鐘周期數(shù)。

2.6 接收和發(fā)送緩沖器

接收和發(fā)送緩沖器,即FIFO,是千兆位級(jí)收發(fā)器的主要數(shù)字接口。FIFO通常是數(shù)據(jù)寫(xiě)入和讀出的地方。發(fā)送端通常有一個(gè)小型的FIFO,它要求讀取和寫(xiě)入的時(shí)鐘是等時(shí)同步(isochronous)的(等時(shí)同步是指頻率匹配但相位不一定匹配)。

如果tx_write和tx_read選通信號(hào)不是工作在精確相同的頻率,則通常采用另外的方法。此時(shí),需要使用一個(gè)較大的FIFO,同時(shí)要求持續(xù)不斷地檢測(cè)FIFO的當(dāng)前狀態(tài)。如果FIFO被不斷地填充,將最終導(dǎo)致溢出。在這種情況下,必須在輸入數(shù)據(jù)流中檢測(cè)idle符號(hào)。如果檢測(cè)到idle符號(hào),則不把idle符號(hào)寫(xiě)入FIFO。

反過(guò)來(lái),如果FIFO運(yùn)行較慢則在輸出數(shù)據(jù)流會(huì)出現(xiàn)idle符號(hào),數(shù)據(jù)被傳送給用戶(hù)。此時(shí)寫(xiě)指針保持不動(dòng),不斷重復(fù)idle符號(hào)。使用idle符號(hào)而不使用字節(jié)對(duì)齊、 Comma字符、時(shí)鐘修正序列或者通道綁定序列,這一點(diǎn)是非常重要的。為了保證一定的發(fā)送速率,所有這些序列都是必需的。

相對(duì)于發(fā)送緩沖器而言, MGT內(nèi)建的接收FIFO通常需要有更深層次的考慮。它的主要目的是為了實(shí)現(xiàn)時(shí)鐘修正和通道綁定。

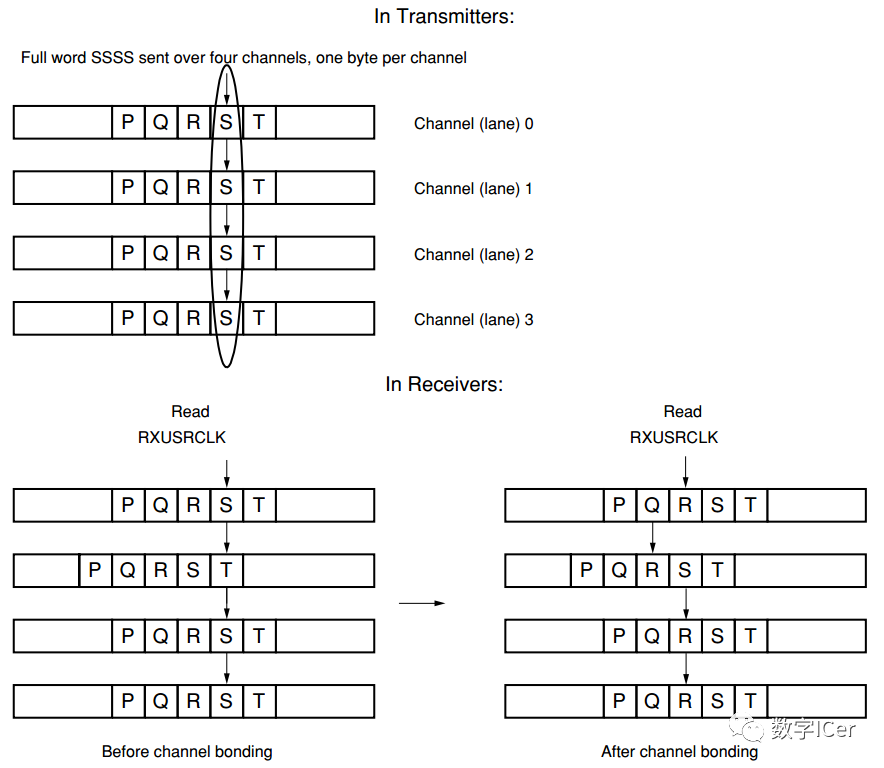

2.7 通道綁定

有時(shí)候我們需要傳送的數(shù)據(jù)會(huì)超過(guò)一條串行鏈路的承載能力。在這種情況下,可以同時(shí)使用多條鏈路來(lái)并行傳輸數(shù)據(jù)。如果使用這種方式,則輸入的數(shù)據(jù)流必須是對(duì)齊的。這個(gè)過(guò)程通常稱(chēng)作通道綁定。通道綁定可以吸收兩個(gè)或多個(gè)MGT之間的偏差,將數(shù)據(jù)提交給用戶(hù),就像只使用一條鏈路進(jìn)行傳送一樣。通道綁定的過(guò)程如下圖所示

不同MGT間數(shù)據(jù)偏差的一些主要原因:

1、 傳輸通道長(zhǎng)度的偏差

2、 傳輸通道的有源中繼器

3、 時(shí)鐘修正引起的偏差

4、 鎖定和字節(jié)對(duì)齊引起的時(shí)間偏差

因?yàn)橥ǖ澜壎ㄐ枰婕暗绞瞻l(fā)器之間的通信,所以具體的細(xì)節(jié)因廠家、器件而異。但是它們有一些共同的特性,例如:指定一個(gè)通道作為主通道,指定從通道,還可能需要指定前向從通道。三級(jí)通道綁定包括一個(gè)主通道和前向從通道,所以通常也稱(chēng)為兩-跳通道綁定。

通道綁定序列必須是唯一的而且是可擴(kuò)展的,因?yàn)榭赡軙?huì)添加或丟棄通道綁定序列,所以下行鏈路中必須忽略。通常時(shí)鐘修正序列和通道綁定序列之間會(huì)有最小間隔符號(hào)數(shù)。很多基于8B/10B的標(biāo)準(zhǔn)協(xié)議規(guī)定時(shí)鐘修正序列和通道綁定序列之間至少需要間隔四個(gè)符號(hào)。因此,四個(gè)符號(hào)或字節(jié)是比較常用的間隔距離。

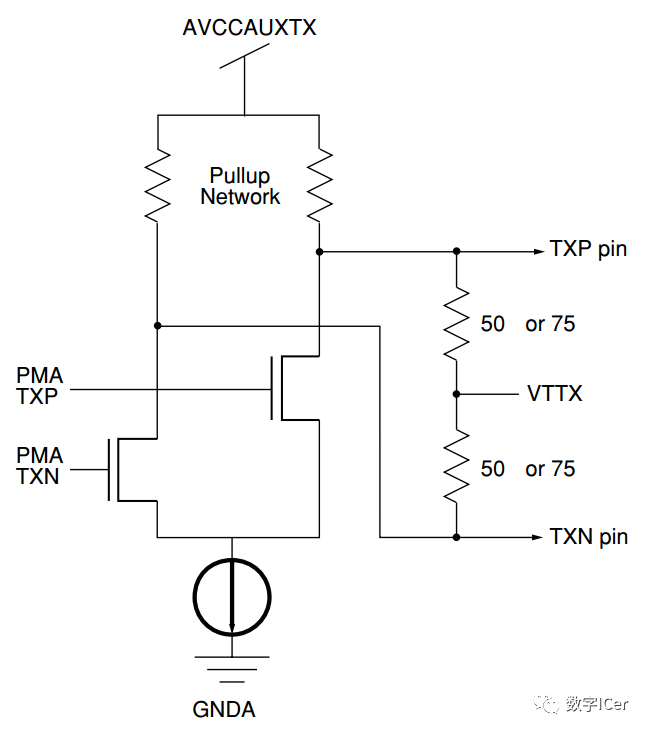

2.8 物理信號(hào)

千兆位級(jí)Serdes的物理實(shí)現(xiàn)普遍采用基于差分的電氣接口。常用的差分信號(hào)方法有三種:低電壓差分信號(hào)(LVDS)、低電壓偽射級(jí)耦合邏輯(LVPECL)和電流模式邏輯(CML)。千兆位鏈路通常使用CML。CML采用最常用的接口類(lèi)型,并且通常都會(huì)提供AC或DC端接以及可選的輸出驅(qū)動(dòng)。部分輸入還提供了內(nèi)建的線(xiàn)路均衡和/或是內(nèi)部端接。通常端接的阻抗也是可選的。

下圖給出了一個(gè)CML型的驅(qū)動(dòng)電路。這些高速驅(qū)動(dòng)電路的原理非常簡(jiǎn)單。兩個(gè)電阻中的一個(gè)始終都有電流通過(guò),并且此電流和通過(guò)另一個(gè)電阻的電流不同。

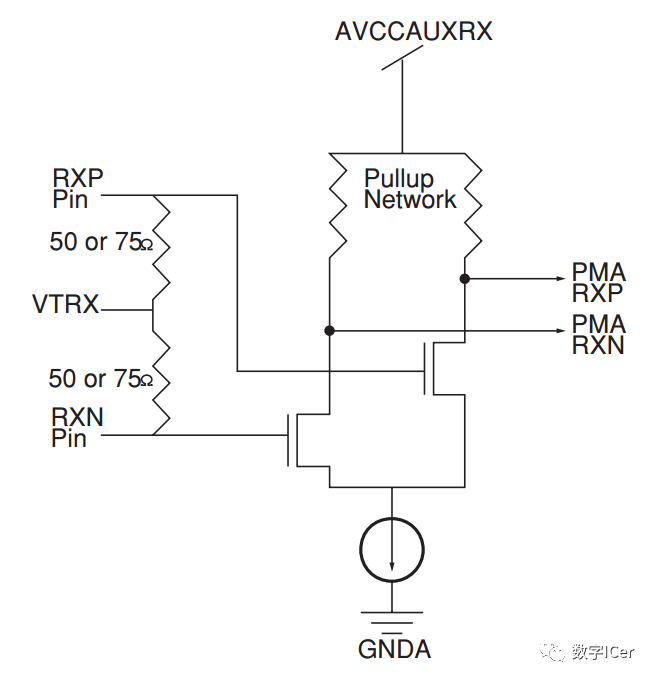

下圖給出了一個(gè)MGT接收器的示意圖。

2.9 預(yù)加重

千兆位級(jí)驅(qū)動(dòng)器最重要的特性可能就是預(yù)加重的能力。預(yù)加重是在轉(zhuǎn)變開(kāi)始前的有意過(guò)量驅(qū)動(dòng)。如果沒(méi)有相關(guān)的經(jīng)驗(yàn),這看起來(lái)會(huì)像是一個(gè)缺陷;看起來(lái)就象是一個(gè)不好的設(shè)計(jì)可能發(fā)生的上沖和下沖。為了弄懂這么做的意圖,我們需要理解符號(hào)間干擾。

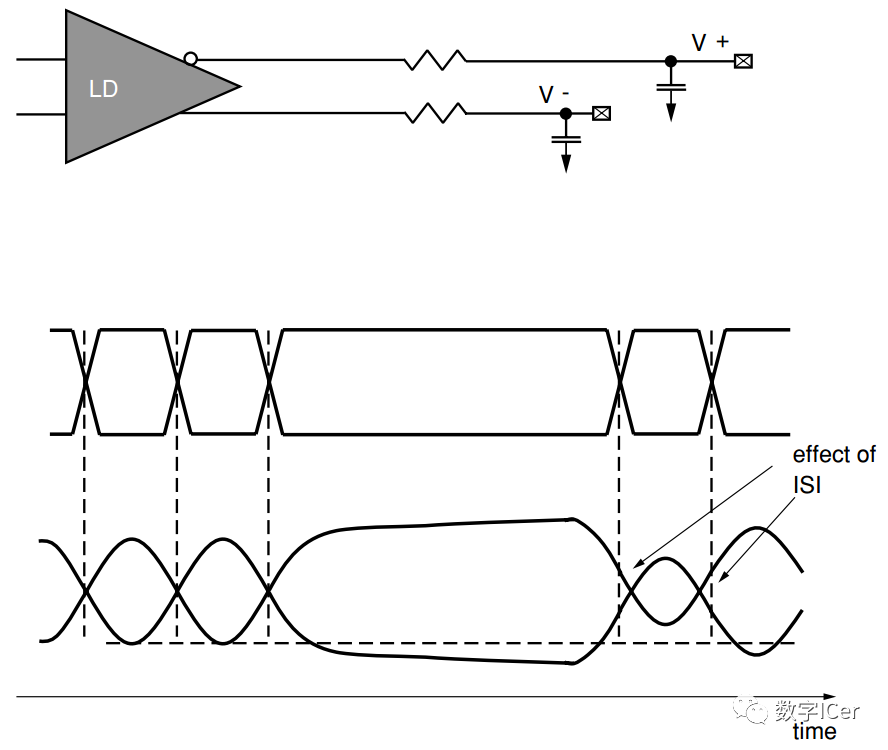

如果串行流包含多個(gè)比特位時(shí)間的相同數(shù)值數(shù)據(jù),而其后跟著短比特位(1或2)時(shí)間的相反數(shù)據(jù)數(shù)值時(shí),會(huì)發(fā)生符號(hào)間干擾。介質(zhì)(傳輸通道電容)在短位時(shí)間過(guò)程中沒(méi)有足夠的充電時(shí)間,因此產(chǎn)生了較低的幅度。符號(hào)間干擾的示意圖如下:

在符號(hào)間干擾的情況下,長(zhǎng)時(shí)間的恒定值將通道中的等效電容完全的充電,在緊接著的相反數(shù)據(jù)數(shù)值位時(shí)間內(nèi)無(wú)法反相補(bǔ)償。所以,相反數(shù)據(jù)的電壓值有可能不會(huì)被檢測(cè)到。這個(gè)問(wèn)題的解決方法是:轉(zhuǎn)變開(kāi)始時(shí)加入過(guò)量驅(qū)動(dòng),而在任意的連續(xù)相同數(shù)值時(shí)間內(nèi)減少驅(qū)動(dòng)量,這種過(guò)程有時(shí)也稱(chēng)作去加重。

2.10 差分傳輸

數(shù)字設(shè)計(jì)工程師和PCB設(shè)計(jì)師們?cè)?jīng)一度認(rèn)為布線(xiàn)只不過(guò)是簡(jiǎn)單的互連或連線(xiàn)。實(shí)際上,原型建造時(shí)通常采用一種叫做蛇行布線(xiàn)的技術(shù)。實(shí)際中并不是一定要運(yùn)用傳輸線(xiàn)和傳輸線(xiàn)理論。如果線(xiàn)路的傳輸延時(shí)只是信號(hào)上升時(shí)間中的很小一部分,我們可以不使用傳輸線(xiàn)理論。

但是隨著信號(hào)的傳輸速率的增大,PCB設(shè)計(jì)過(guò)程中就必須使用傳輸線(xiàn)理論。對(duì)于千兆位級(jí)操作而言,不僅包括傳輸線(xiàn)和阻抗控制,還包括差分線(xiàn)路對(duì)的阻抗控制。差分線(xiàn)路對(duì)阻抗匹配的兩條線(xiàn)路是相鄰的。兩條線(xiàn)路之間的間隔使得兩線(xiàn)路相互耦合。如果兩線(xiàn)路相隔較遠(yuǎn),則稱(chēng)作弱耦合。如果相隔較近,則為強(qiáng)耦合。

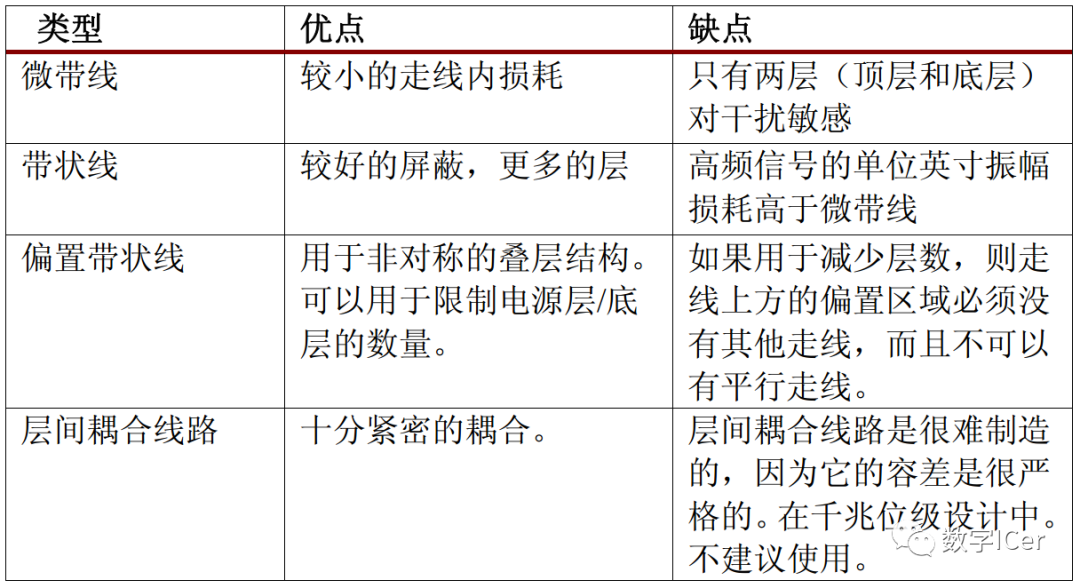

如果給定線(xiàn)路的長(zhǎng)度以及疊層結(jié)構(gòu)(會(huì)帶來(lái)給定的阻抗),耦合還會(huì)影響線(xiàn)路的阻抗。相同幾何形狀的差分線(xiàn)路對(duì)也會(huì)有不同的阻抗。阻抗的精確大小因材料而異,但是板制作廠商通常會(huì)提供精確的數(shù)據(jù)。下表給出了受控阻抗差分線(xiàn)路的各種類(lèi)型。

2.11 線(xiàn)路均衡

均衡主要用于補(bǔ)償由頻率不同而引起的阻抗/衰減差異。均衡器有很多種形式,但總體上可以分為有源和無(wú)源兩種。

無(wú)源均衡器是無(wú)源電路,其頻率響應(yīng)可以補(bǔ)償傳輸衰減。無(wú)源均衡器可以認(rèn)為是一個(gè)濾波器。如果我們的濾波器可以使傳輸線(xiàn)所使用的各頻率通過(guò),而將傳輸線(xiàn)沒(méi)有使用的其他頻率濾除,那么整體的頻率響應(yīng)就會(huì)變得平坦許多。

有源均衡器可以認(rèn)為是依賴(lài)頻率的放大器/衰減器。有源均衡器主要有兩種:固定形式有源均衡器和自適應(yīng)有源均衡器。對(duì)于任意的輸入數(shù)據(jù)流,固定形式有源均衡器的頻率響應(yīng)都是一樣的。

固定形式均衡器的增益/衰減量通常是用戶(hù)可選擇的,或者可編程的。部分均衡器有一個(gè)簡(jiǎn)單的控制參數(shù)—n 用于設(shè)置高增益或低增益,類(lèi)似于簡(jiǎn)單音響系統(tǒng)中的低音設(shè)置。還有一些均衡器可以獨(dú)立設(shè)置不同頻率的增益/衰減量,這和復(fù)雜音響系統(tǒng)中的均衡設(shè)置是類(lèi)似的。

自適應(yīng)均衡器(也稱(chēng)學(xué)習(xí)型均衡器)要復(fù)雜的多,自適應(yīng)均衡器需要分析輸入信號(hào)并檢測(cè)哪些頻率在傳輸通道中被削弱。測(cè)量和調(diào)節(jié)是以閉環(huán)形式實(shí)現(xiàn)的。自適應(yīng)均衡器的頻率響應(yīng)取決于輸入的比特流。

自適應(yīng)均衡器通常和特殊形式的線(xiàn)路編碼機(jī)制協(xié)同工作。自適應(yīng)均衡器對(duì)于可變通道的鏈路來(lái)說(shuō)是最合適的,可變通道可以是可變的電纜長(zhǎng)度,或是顯著的位置依賴(lài)的背板系統(tǒng)。固定形式均衡器比較適合于不變系統(tǒng)中,例如:芯片到芯片,平衡化的背板系統(tǒng)以及固定長(zhǎng)度電纜的系統(tǒng)。均衡器通常包含在SERDES的模擬前端,或者作為系統(tǒng)的一個(gè)獨(dú)立部分。

2.12 光解決方案

如果系統(tǒng)中電纜要傳輸?shù)木嚯x很遠(yuǎn)(遠(yuǎn)大于相鄰底板的距離),那么通常采用光解決方案。使用光纖可以實(shí)現(xiàn)多種長(zhǎng)距離傳輸,例如:樓下到樓上,樓與樓之間,街區(qū)之間或者城鎮(zhèn)之間。

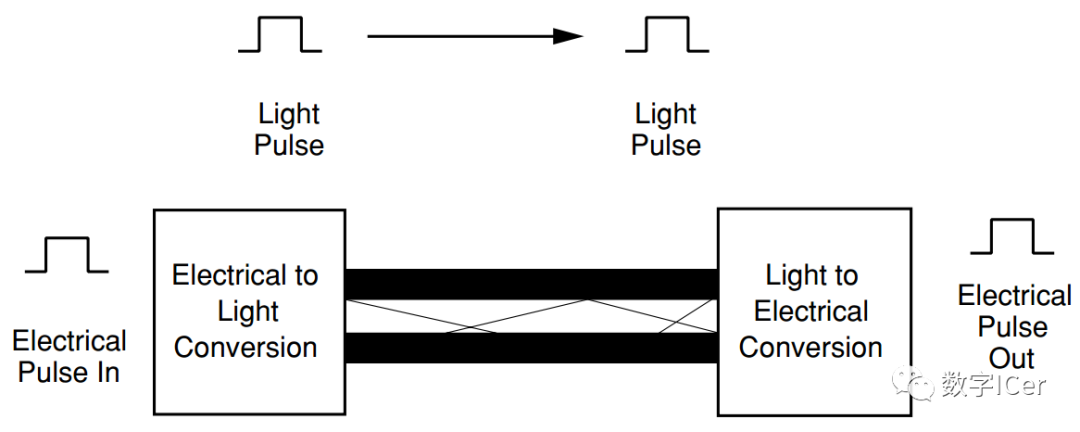

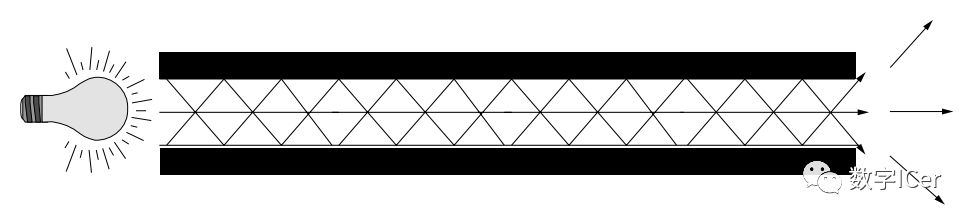

光纖系統(tǒng)使用光信號(hào)取代電信號(hào)來(lái)傳輸信息。最基本的光纖系統(tǒng)包括發(fā)送器或信號(hào)源、光纖以及接收器,接收器將光脈沖重新轉(zhuǎn)變?yōu)殡娦盘?hào)。信號(hào)源通常是注入型激光二極管(ILD)或者發(fā)光二極管(LED),如下圖所示。

光纖中的光脈沖傳輸是基于全反射定理的。全反射定理:如果入射角大于臨界值,則光線(xiàn)不會(huì)透射而會(huì)全部反射回來(lái)。簡(jiǎn)單的說(shuō),光纖可以看作是一個(gè)內(nèi)部全是鏡子的彈性管線(xiàn)。光線(xiàn)在管道中不停反射前進(jìn),就算管道發(fā)生了彎曲,光線(xiàn)也能一直前進(jìn)到達(dá)末端。

光線(xiàn)有兩種類(lèi)型——單模光纖和多模光纖。單模的價(jià)格較高,可以傳輸?shù)木嚯x也較長(zhǎng)。多模光纖的價(jià)格較低,只能用于短距離傳輸。

單模光纖的示意圖如下圖所示

多模光纖的示意圖如下圖所示

基本的光連接器如下圖所示

2.13 循環(huán)冗余校驗(yàn)碼(CRC)

設(shè)計(jì)師還是需要設(shè)計(jì)一個(gè)穩(wěn)健的系統(tǒng)。首先,他需要檢查系統(tǒng)的要求,看是否能夠使用常用的方法來(lái)解決問(wèn)題。

一種方法是錯(cuò)誤檢測(cè)數(shù)據(jù)重傳。檢查輸入數(shù)據(jù)中是否有錯(cuò)。如果發(fā)現(xiàn)錯(cuò)誤,則發(fā)送信息給發(fā)送者要求重傳數(shù)據(jù)。錯(cuò)誤檢測(cè)的首選方法是CRC。因?yàn)镃RC十分常用,所以許多SERDES內(nèi)部都有CRC發(fā)生器和檢測(cè)邏輯。通常重傳請(qǐng)求是由上層協(xié)議定義的。如果協(xié)議支持CRC和重傳,或者數(shù)據(jù)要求正是其所能滿(mǎn)足的,那么這種方法將會(huì)是最好的選擇。

如果情況不是這樣的話(huà),設(shè)計(jì)師還可以有其他的選擇。設(shè)計(jì)師可以建造并測(cè)試所設(shè)計(jì)的系統(tǒng),以觀察其能否正常工作。SERDES發(fā)布的BER可以用來(lái)確定測(cè)試需要進(jìn)行到什么程度,所以設(shè)計(jì)師還是有一些機(jī)動(dòng)空間的。設(shè)計(jì)師不可能設(shè)計(jì)出一個(gè)遠(yuǎn)優(yōu)于發(fā)布數(shù)據(jù)的系統(tǒng)。除了持續(xù)測(cè)試直到達(dá)到發(fā)布的BER,設(shè)計(jì)師還需要在各種極限情況下進(jìn)行測(cè)試(例如,輸入抖動(dòng)十分靠近容限)。如果給系統(tǒng)設(shè)計(jì)提供更好的輸入流,那么結(jié)果會(huì)更好。

數(shù)據(jù)還提供了另一種值得考慮的選擇。多數(shù)的數(shù)據(jù)流都是有模式的,和用于BER測(cè)試的偽隨機(jī)比特流相比,數(shù)據(jù)流更容易預(yù)測(cè)。這一點(diǎn)可能是好處也可能是壞處,這取決于傳輸通道和均衡器適配數(shù)據(jù)流的情況。所以必須進(jìn)行測(cè)試和調(diào)整。所以建造一個(gè)系統(tǒng)并觀察其能否正常工作,這種方法并不是十分牽強(qiáng)的。盡管如此,如果這種方法會(huì)出現(xiàn)操作上的問(wèn)題,那么前向糾錯(cuò)(FEC)可能會(huì)有所幫助。

2.14 前向糾錯(cuò)(FEC)

由于設(shè)計(jì)師知道可能會(huì)發(fā)生錯(cuò)誤,所以可以通過(guò)提供冗余數(shù)據(jù)位來(lái)恢復(fù)這些錯(cuò)誤。常用的方法就是利用一些前向糾錯(cuò)碼來(lái)對(duì)數(shù)據(jù)流中的錯(cuò)誤進(jìn)行糾正。

前向糾錯(cuò)的定義:添加額外的位,用于幫助恢復(fù)錯(cuò)誤數(shù)據(jù)。

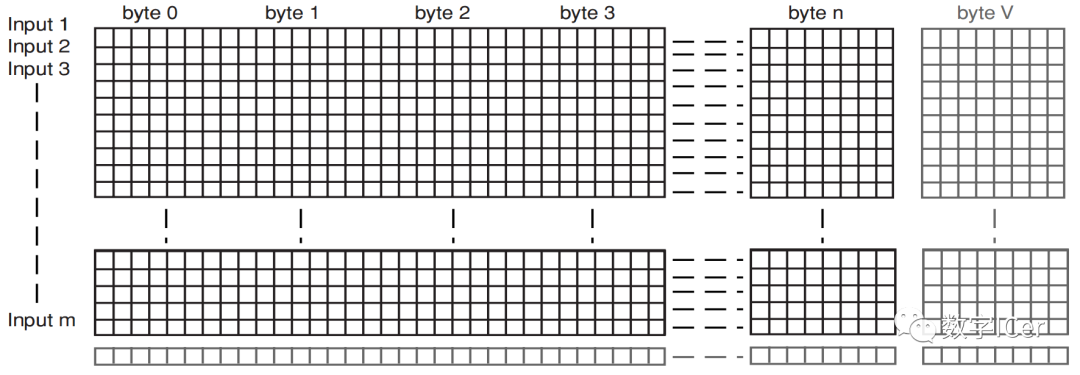

考慮一個(gè)待傳輸?shù)臄?shù)據(jù)塊,其大小為NxR字節(jié),分為R行,每行N字節(jié)。現(xiàn)在給矩陣的每一行附加額外的一個(gè)字節(jié),并給矩陣附加額外的一行。這些地方就是額外的位置。

數(shù)據(jù)塊的附加信息就保存在這些額外的位置中。此例中,額外的信息是奇偶位。附加字節(jié)的每一位代表此行中各字節(jié)對(duì)應(yīng)位的奇偶性。也就是說(shuō),P[1][0]是D[1.1][0] D[1.2][0]D[1.3][0] …。 D[1.N][0]的奇偶性。而對(duì)于額外的行而言,其中的每一位就是對(duì)應(yīng)列中各位的奇偶性。也就是說(shuō), P[R+1.0][0]是 D[0.0][0], D[1.0][0] D[2.0][0] ….D[N.0][0]的奇偶性。矩陣的示意圖如下圖所示。

數(shù)據(jù)和附加位同時(shí)通過(guò)鏈路傳輸。在另一側(cè),接收器會(huì)檢查矩陣的奇偶性。如果數(shù)據(jù)的任一位是錯(cuò)誤的,那么它會(huì)標(biāo)記出來(lái),并通過(guò)行值和列值來(lái)確定位置。只需要簡(jiǎn)單的取反,即可糾正該位的錯(cuò)誤。多位的錯(cuò)誤即可能被糾正,也可能會(huì)導(dǎo)致混亂而且會(huì)阻止其他錯(cuò)誤的糾正,這取決于錯(cuò)誤發(fā)生的位置。

這種方法通常稱(chēng)作簡(jiǎn)單矩陣奇偶性法,而且也是FEC的最初類(lèi)型。這也是多數(shù)FEC方法基本模塊。這個(gè)例子是簡(jiǎn)單易懂的,但是它有局限性。針對(duì)惡劣環(huán)境和性能不好的傳輸通道,已經(jīng)開(kāi)發(fā)出多種FEC 方法,例如Viterbi,Reed-Soloman 和 Turbo 編碼。所有這些方法都有強(qiáng)大的糾錯(cuò)能力,但是糾錯(cuò)也是有代價(jià)的:

1、運(yùn)行速度不夠快: 與大多數(shù)可以在常規(guī)結(jié)構(gòu)下發(fā)揮作用的方法相比,千兆位級(jí) SERDES的速度較快。

2、編解碼器太過(guò)龐大: 編碼器和解碼器的電路邏輯數(shù)量可能會(huì)是MGT及其剩余部分的十倍。

3、編碼開(kāi)銷(xiāo)過(guò)大: 編碼開(kāi)銷(xiāo)就是那些附加的位。編碼開(kāi)銷(xiāo)過(guò)大常常可以使一種 FEC方法不可行。

三 總結(jié)

Serdes技術(shù)中的各種可用功能極大地促進(jìn)了I/O設(shè)計(jì)的發(fā)展。SERDES的各種功能例如RX定位、時(shí)鐘管理器、發(fā)送/接收FIFO、線(xiàn)路編碼器/解碼器等被廣泛用于提高速度和精確度。SERDES在未來(lái)I/O設(shè)計(jì)中扮演著重要角色,它提供的各種功能也將是高效 I/O器件設(shè)計(jì)的重要工具。

原文標(biāo)題:SERDES關(guān)鍵技術(shù)

文章出處:【微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

責(zé)任編輯:haq

-

FPGA

+關(guān)注

關(guān)注

1626文章

21667瀏覽量

601846 -

SerDes

+關(guān)注

關(guān)注

6文章

197瀏覽量

34853 -

大數(shù)據(jù)

+關(guān)注

關(guān)注

64文章

8863瀏覽量

137299

原文標(biāo)題:SERDES關(guān)鍵技術(shù)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

紫光同芯亮相SAECCE 2024汽車(chē)芯片關(guān)鍵技術(shù)及產(chǎn)業(yè)化應(yīng)用論壇

實(shí)驗(yàn)室被動(dòng)式空氣凈化技術(shù)關(guān)鍵技術(shù)解析

磷酸鐵鋰電池自動(dòng)分選機(jī):提升生產(chǎn)效率與電池品質(zhì)的關(guān)鍵技術(shù)

LLM大模型推理加速的關(guān)鍵技術(shù)

機(jī)載低軌衛(wèi)星通信發(fā)展及關(guān)鍵技術(shù)綜述

面向手機(jī)直連的星載相控陣:關(guān)鍵技術(shù)與未來(lái)展望

云安全的關(guān)鍵技術(shù)有哪些

儲(chǔ)能BMS的關(guān)鍵技術(shù)是什么

車(chē)載電池的類(lèi)型及關(guān)鍵技術(shù)分析

EMI濾波器:工業(yè)應(yīng)用的關(guān)鍵技術(shù)與性能優(yōu)勢(shì)?

機(jī)器視覺(jué)缺陷檢測(cè)是工業(yè)自動(dòng)化領(lǐng)域的一項(xiàng)關(guān)鍵技術(shù)

淺談基于數(shù)字孿生的配電室關(guān)鍵技術(shù)研究

人工智能中文本分類(lèi)的基本原理和關(guān)鍵技術(shù)

物聯(lián)網(wǎng)關(guān)鍵技術(shù)和應(yīng)用

SERDES用到的各種關(guān)鍵技術(shù)討論

SERDES用到的各種關(guān)鍵技術(shù)討論

評(píng)論