0 引言

AVS[1](audio video coding standard)是《信息技術 先進音視頻編碼》系列標準的簡稱,是我國具有自主知識產權的第二代信息編解碼標準。2008年底,AVS標準工作組開始起草雙目立體編解碼方案[2]。該方案采用雙目拼接算法,所用視頻序列由基線相互平行的兩攝像機采集,將左、右視點信息合成為一個碼流進行傳輸;而在解碼端恢復出左、右兩路圖像數據。

但目前,尚沒有針對AVS 3D標準的FPGA/SoC軟硬協同平臺實現。本文以Xilinx公司的ZYNQ 7020開發板為平臺,它是內部具有兩個M9處理(Processing System,PS)硬核核心的片上系統芯片,該平臺具有芯片集成度高、控制能力強、軟件通用性好的優點。本文采用一個主PS作為頂層控制,完成3D ES流的外部接口通信和解碼圖像顯示控制;另一個從PS以及部分硬件加速模塊(包括ES流的語法解析、算術碼解碼、變長碼解碼等硬件加速模塊)共同完成AVS雙目拼接解碼算法。兩個PS協同工作,在FPGA/SoC平臺上實現了AVS 3D實時解碼器。

1 AVS 3D解碼器的算法流程

AVS 3D解碼器采用雙目拼接算法。AVS 3D ES流同時含有左、右視點的兩路信息。3D解碼器的算法設計流程圖如圖1所示。讀入3D ES流,以幀為單位解碼,其解碼原理與AVS單路解碼器相似。

視點分離得到的左、右視點基本層圖像存在水平維度的分辨率減半。由于基本層圖像和增強層圖像存在很強的空間相關性,故對基本層圖像進行水平維度的上采樣插值濾波,預測得到分辨率提升的增強層圖像。為保證增強層圖像質量,需要對上采樣濾波器核向量進行設置[3],其原理如式(1)所示:

視點分離得到的基本層圖像分辨率為M/2×N,需要在水平維度上進行上采樣插值濾波。在具有水平關系的兩個基本層像素點xi,j和xi,j+1之間插入半像素點vi。通過水平插值,從分辨率為M/2×N的基本層圖像預測得到分辨率為M×N的增強層圖像。

2 語法元素解析的CABAC和CAVLC硬件加速模塊的設計

本文通過硬件加速模塊實現拼接碼流的語法解析工作,AVS標準中的熵解碼主要采用CABAC[4]和CALVC[5]兩種方式實現。語法元素解析模塊的硬件加速模塊設計框圖如圖2所示。

碼流輸入管理模塊的主要任務是讀入ES原始碼流。其中indata[7:0]存儲原始ES流的8 bit數據;avail_n檢測輸入數據的可得字節數;strobe表示輸入碼流有效性;當讀入的數據解析完成后,req通知ES流繼續讀入。

語法元素輸出模塊主要控制熵解碼后語法元素的數據輸出。其中n_bits表示請求讀取語法數據的bit數;req為請求讀取語法信息;req_type為當前語法元素所需采用的熵解碼方式,根據req_type的不同,對當前元素采用CABAC或CAVLC解析算法;outdata[31:0]為熵解碼后的數據;del_ready指示當前語法解析模塊是否準備好接受外部請求;strobe為當前請求輸出語法信息有效性。

核心語法解析單元運行CABAC或CAVLC的解析算法,涉及模型索引號產生、模型自適應更新、反二進制化等過程。在AVS標準中,CABAC主要用于解析宏塊類型、亮度色度預測模式、變換系數等數據;CAVLC主要用于解析亮度和色度殘差數據。

AVS的碼流數據結構及層次關系從高到低依次為:序列、圖像、條帶、宏塊和塊,在解碼過程中,需要從高到低依次解析出每一層次中的語法元素數據。將硬件加速模塊解析得到的數據賦值給相應的語法元素變量,利用得到的語法元素變量在,恢復出左、右視點的重建圖像。

3 AVS 3D實時解碼器在SoC片上系統的設計與實現

本文采用Xilinx公司ZYNQ 7020開發板,ZYNQ 7020采用雙核設計,擁有兩片Cortex-M9芯片,一片用作主處理系統,一片用作核心AVS算法解碼,兩片M9可以共享內存和外圍設備。針對AVS 3D解碼器,本文采用Master-Slave主從控制設計模式。采用MASTER M9作為頂層控制,完成ES 3D碼流的外部接口通信、解碼圖像顯示控制等功能;SLAVE M9及語法解析硬件加速模塊共同完成AVS 3D核心解碼算法; MASTER M9和 SLAVE M9協同工作,最終實現AVS 3D實時解碼器SoC片上系統設計[6]。

3.1 AVS 3D解碼器在ZYNQ 7020的啟動過程

在啟動AVS雙目解碼器的SoC片上系統時,首先在ZYNQ 7020上進行時鐘配置,之后在MASTER M9上執行BootROM啟動代碼。BootROM是整個SoC系統上最先運行的程序,當SLAVE M9等待解碼啟動指令時,BootROM已經在MASTER M9上運行。BootROM的主要功能是配置整個雙目解碼器的SoC系統的串口信息,并將第一階啟動程序(First Stage Boot Loader,FSBL)從啟動設備復制到MASTER M9的片上內存。

由FSBL初始化SLAVE M9的Xilinx硬件配置信息,并通過讀入BootHeader頭文件通知MASTER M9是否啟動運行。在FBSL運行的過程中,BootROM會先將SLAVE M9設置為事件等待模式,MASTER M9啟動后,由MASTER M9通知SLAVE M9是否啟動AVS雙目立體解碼程序。整個啟動流程如圖3所示。

3.2 AVS 3D解碼器在ZYNQ 7020的設計原理

AVS雙目立體解碼器在SoC片上系統的整體方案設計如圖4所示。在各個模塊的交互過程中,通過AXI LITE傳送信息量較小的數據;通過AXI VDMA傳遞解碼圖像數據等信息量較大的數據;通過AXI CON傳送交互頻繁的數據。

MASTER M9是整個AVS 3D解碼器在SoC片上系統的頂層控制單元。其功能主要包括:

(1)從以太層獲取用于網絡傳輸的3D TS碼流;

(2)與TS碼流語法解析模塊進行信息交互,通知SLAVE M9啟動解碼過程。SLAVE M9根據碼流中解析標志位的不同,調用硬件加速模塊采用CALVC或是CABAC的熵解碼方式對碼流中的語法元素進行解析,并與狀態信息模塊交互,將熵解碼方式標志位、緩存大小、解析完成標志位等信息返回給MASTER M9;

(3)管理解碼圖像數據及參考幀的位置指針,并將相應數據送往DDR MEMORY不同存儲位置。

SLAVE M9運行AVS 3D解碼器的核心算法。解碼算法包括AVS雙目拼接算法和AVS單路解碼算法兩部分。AVS雙目拼接算法如第1節所述。單路解碼器算法主要包括:起始碼檢測、序列及圖像頭讀取、熵解碼、宏塊數據獲取、反變換、反量化、幀內及幀間預測、1/4像素運動向量插值、圖像殘差恢復、環路濾波等模塊。將實現AVS 3D解碼功能的C語言代碼寫至相應的軟件開發平臺,由硬件加速模塊將語法元素解析模塊得到的語法元素數值輸入各個層級的解碼函數,從而通過SLAVE M9上實現AVS 3D解碼算法。最終將解碼得到的拼接圖像序列和左、右視點圖像序列寫入DDR MEMORY的不同地址空間。

解碼圖像信息交換模塊是MASTER M9和SLAVE M9在解碼過程中圖像信息交互的中介。在SLAVE M9解碼過程中會產生3種圖像指針類型:

(1)參考幀指針(針對I、P幀圖像),該指針指向的圖像作為幀間預測的參考值,并不會立即顯示;

(2)顯示幀指針(針對B幀圖像),該指針指向的圖像在解碼后直接放入顯示序列中;

(3)寫入位置指針,SLAVE M9解碼一幀圖像后,將解碼數據寫入在該指針指向的DDR MEMORY地址中。通過該模塊,SLAVE M9將圖像指針的狀態和數值傳送給MASTER M9,MASTER M9又與DDR MEMORY交互,保證正確的圖像解碼順序和顯示順序。

在DDR MEMORY中采用乒乓存儲設計,設置兩塊數據緩存區,每塊數據緩存區為拼接圖像、左視點圖像、右視點圖像各分配5幀內存空間。當緩存區1向HDMI接口傳輸數據時,緩存區2從SLAVE M9接收數據;當緩存區1從SLAVE M9接收數據時,緩存區2向HDMI接口傳輸數據;如此循環工作,通過兩塊緩存區的交替工作,提高DDR MEMORY的工作效率。其中每塊緩存區中的數據讀寫位置均由MASTER M9管理,保證DDR MEMORY以正確的顯示順序將圖像內容送往HDMI接口。

4 實驗結果及分析

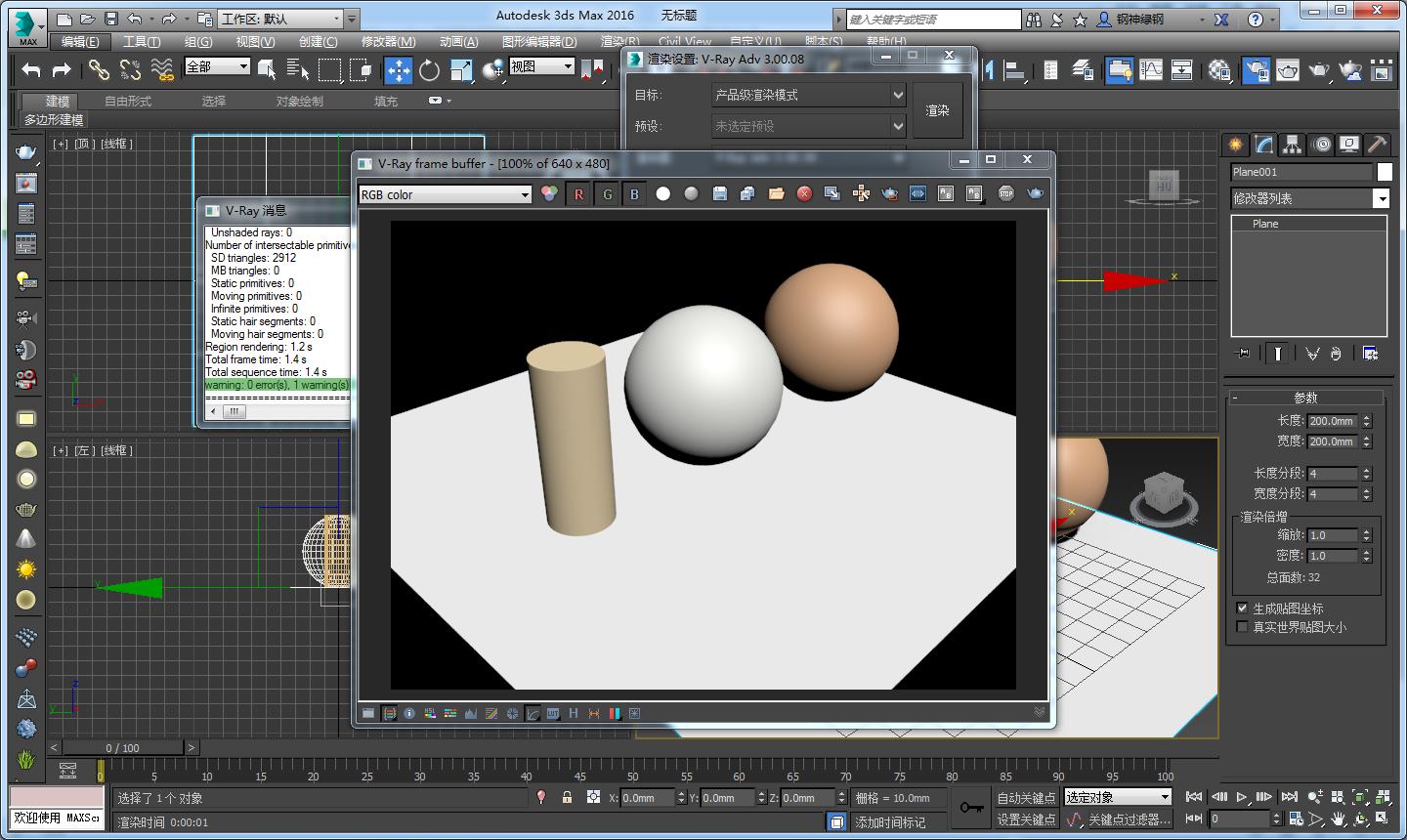

本文中,AVS 3D解碼器的SoC片上系統設計在Xilinx ZYNQ 7020開發板上實現。通過在AVS單路軟件解碼器RM52k上增加視點分離模塊、層間上采樣濾波模塊實現AVS 3D解碼算法,將代碼改寫至Xilinx SDK 2014.2嵌入式軟件平臺,并加載FreeRTOS操作系統用于內存分配和外圍設備初始化。AVS雙目立體解碼參數配置如表1所示。

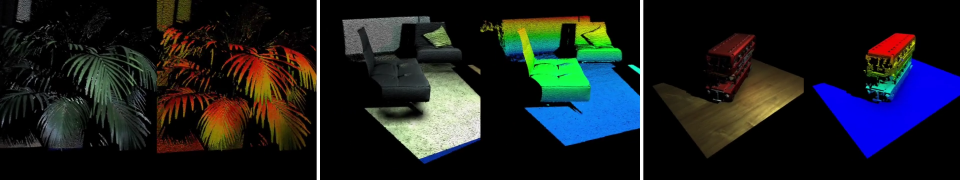

將AVS 3D ES流打包成為用于網絡傳輸的TS流,根據Xilinx的LWIP準則進行TCP連接,經IP QAM調制器最終從以太層將碼流輸入ZYNQ 7020的MASTER M9模塊。通過硬件加速模塊實現語法元素解析,結合SoC片上系統進行AVS雙目立體解碼算法處理,最終通過HDMI接口將視頻數據輸出到三維電視,在三維電視上可以得到左、右視點信息的拼接視頻,通過視點分離和層間上采樣插值,恢復出左、右視點的增強層圖像。經視點交織處理后,得到最終的3D視頻,可以觀察到解碼得到的3D視頻具有明顯的深度信息,AVS 3D解碼器的效果如圖5所示。這說明了AVS 3D實時解碼器在FPGA/SoC平臺的有效性。

5 結束語

本文通過在AVS原有單路解碼器的基礎上進行功能的擴充,實現了基于AVS標準的3D解碼器的設計。結合語法元素解析的硬件加速模塊,在Xilinx ZYNQ 7020開發板上創新性地實現了AVS 3D實時解碼器的FPGA/SoC協同平臺實現。將解碼后的視頻輸入三維顯示設備,通過視點交織觀察到3D視頻的視點差異和深度信息,驗證了該AVS 3D實時解碼器在FPGA/SoC平臺設計的有效性。

參考文獻

[1] 侯金亭,馬思偉,高文.AVS標準綜述[J]。計算機工程,2009,35(8):247-249,252.

[2] 馬茜,李棟,汪啟扉,等.AVS立體視頻編碼標準[J]。上海大學學報(自然科學版),2013,19(3):225-228.

[3] 王樟,柳健,嚴國萍。簡單高效地用于SVC標準中的層間上采樣濾波方案[J]。通信學報,2008,29(4):8-12.

[4] MARPE D,SCHWARZ H,WIEGAND T.Context-based adaptive binary arithmetic coding in the H.264/AVC video compression standard[J].IEEE Transactions on Circuits and Systems for Video Technology,2003,13(7):620-636.

[5] ALLE M,BISWAS J,NANDY S K.High performance VLSI architecture design for H.264 CAVLC decoder[C].ASAP 2006:11-13.

[6] 郭煒,郭箏,謝憬,等.SOC設計方法與實現[M]。北京:電子工業出版社,2007.

編輯:jq

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602037 -

解碼器

+關注

關注

9文章

1131瀏覽量

40684 -

AVS

+關注

關注

0文章

55瀏覽量

23147 -

CABAC

+關注

關注

0文章

4瀏覽量

2558

發布評論請先 登錄

相關推薦

無線網解碼器怎么連接

無線解碼器的質量標準是什么

在基于TMS320C64x的DSP平臺上運行TMS320C64x編解碼器

解碼器和控制器區別是什么

控制器解碼器的使用方法

交互式低延遲音頻解碼器

全景聲解碼器

9740解碼器配什么光柵

光柵解碼器損壞的表現有哪些

如何搭建3d數字孿生平臺

VIVERSE 推行實時3D渲染: 探索Polygon Streaming技術力量與應用

基于AVS 3D實時解碼器在 FPGA/SoC平臺上的設計與實現

基于AVS 3D實時解碼器在 FPGA/SoC平臺上的設計與實現

評論