本原創教程由芯驛電子科技(上海)有限公司(ALINX)創作,版權歸本公司所有,如需轉載,需授權并注明出處(http://www.alinx.com)。

適用于板卡型號:

PGL22G

1. 簡介

本教程介紹如何使用FTDI公司的FT232H驅動芯片進行USB數據傳輸,文中從底層FPGA、驅動層固件(FT232H固件)及上位機測試軟件設計方面闡述了USB開發的整個流程。

2. 實驗原理

2.1 FT232H原理介紹

FT232H是由FTDI公司生產的單路USB2.0驅動芯片,USB速度高達480Mb/s,支持轉UART或FIFO模式,并可配置成多種工業串行或并行接口:

(1)可配置成UART接口;

(2)FT245同步FIFO接口;

(3)FT245風格異步FIFO接口;

(4)同步或異步Bit-Bang接口;

(5)MPSSE接口;

(6)Fast串口;

(7)CPU風格FIFO接口;

(8)FT1248接口。

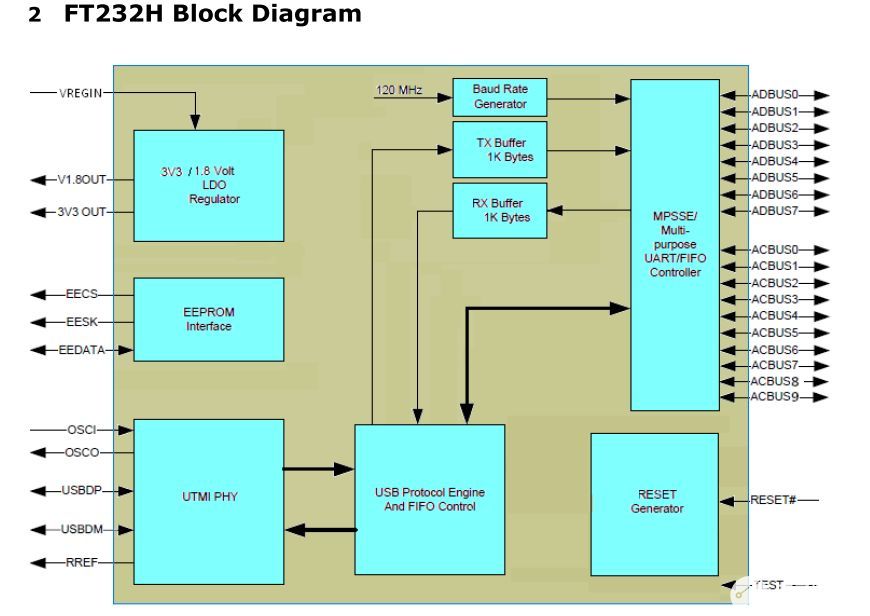

在本實驗中配置成FT245同步FIFO接口。下面是FT232H的內部結構圖。

2.2 硬件原理圖

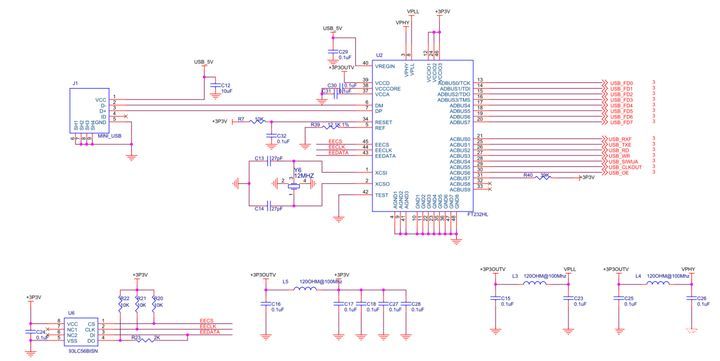

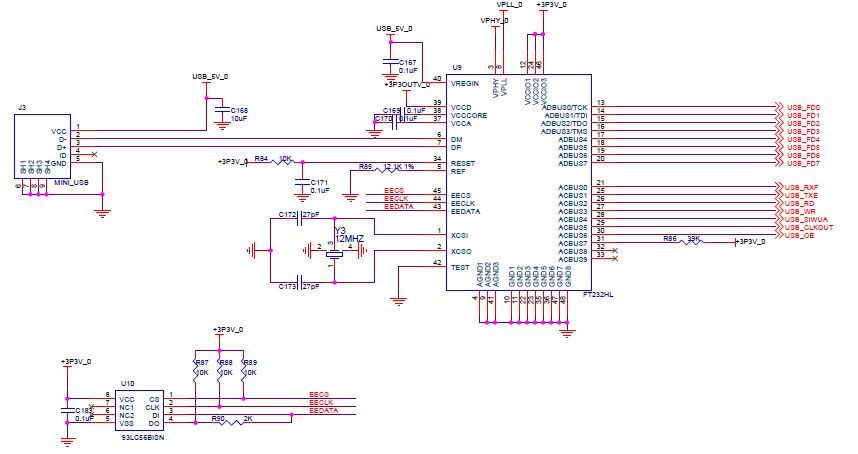

如下為AX7035/AX7050開發板的USB部分原理圖,USB驅動芯片采用FT232HL,配置為FT245 FIFO模式,通過與93LC56存儲芯片相連,將FT232HL配置為FT245 FIFO模式的信息存儲于芯片中。

AX7050 USB部分原理圖

AX7050 USB部分原理圖 AX7035 USB部分原理圖

AX7035 USB部分原理圖

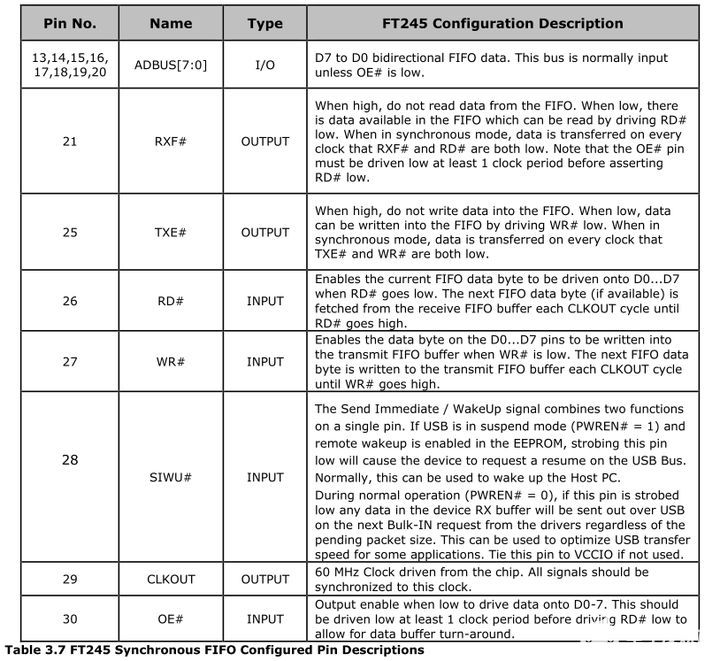

2.3 FT245 FIFO接口引腳

如下表所示為FT245 FIFO接口,ADBUS為并行接口,供FPGA使用,RXF#,TXE#為FT232H輸出信號,用于通知FPGA是否可讀可寫,RD#,WR#為讀寫輸入信號,由FPGA控制,CLKOUT為輸出時鐘60MHz,OE#為輸出全能,需要在RD#有效之前至少提前一個時鐘周期。

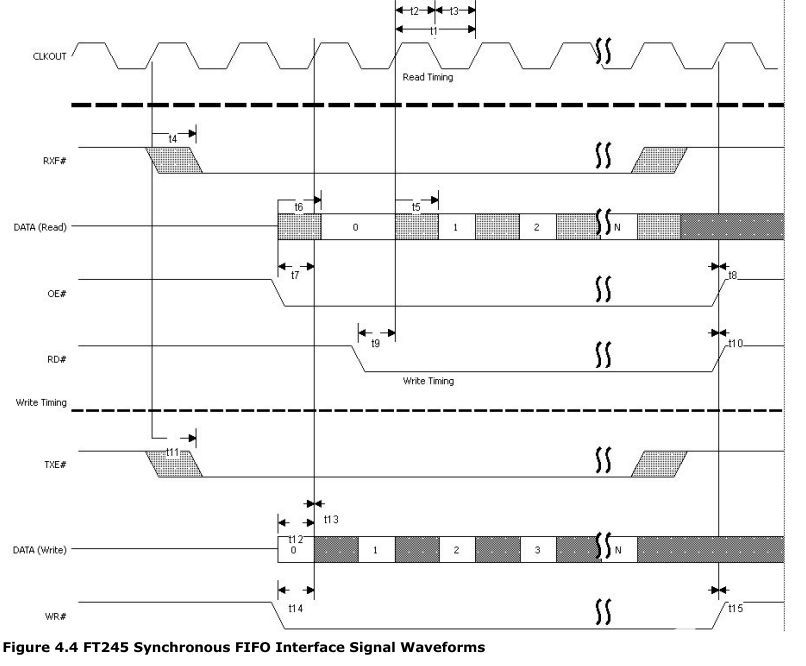

2.4 FT245 FIFO時序

下圖為FT245 FIFO模式時序圖,讀時序中,首先FT232H將RXF#拉低,此時可以讀取FIFO里的數據,FPGA可將OE#先拉低,過至少一個時鐘周期,再將RD#拉低,在CLKOUT上升沿采集數據;寫時序中,FT232H將TXE#拉低,表示現在可寫,FPGA可將WR#拉低,在CLKOUT上升沿寫入數據。

3. 程序設計

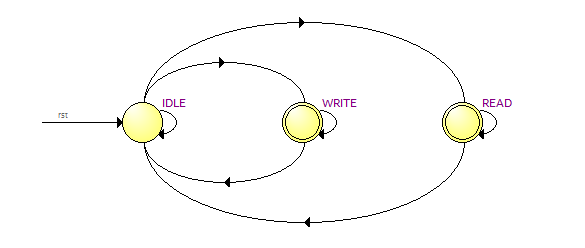

程序設計比較簡單,功能實現為將從FT232H的讀FIFO中讀取的數據存儲到雙口RAM中,再將數據從RAM讀取出來發送到FT232H的寫FIFO中,實現數據的環通。代碼實現根據前面所講的時序圖,實現其功能即可。

代碼中采用了簡單的狀態機,首先在IDLE狀態下判斷ft_rxf_n信號是否是0,如果是0,進入READ狀態,開始讀取FT232H的數據,并存入RAM中,如果ft_rxf_n拉高,進入IDLE狀態;否則判斷ft_txe_n是否為0并且RAM空間不為空,進入WRITE狀態,將RAM數據寫入FT232H,如果ft_txe_n拉高或者RAM空了,進入IDLE狀態。

| 引腳名稱 | 功能描述 |

| ft_clk | FT232H時鐘,CLKOUT頻率60MHz |

| rst | 復位信號,高電平有效 |

| ft_rxf_n | RXF# FT232H FIFO可以讀,低電平有效 |

| ft_txe_n | TXE# FT232H FIFO可以寫,低電平有效 |

| ft_oe_n | OE# 輸出使能,低電平有效 |

| ft_rd_n | RD# 讀信號,低電平有效 |

| ft_wr_n | WR#寫信號,低電平有效 |

| ft_data | FT232H數據端口,8位位寬,雙向IO |

4. 實驗流程

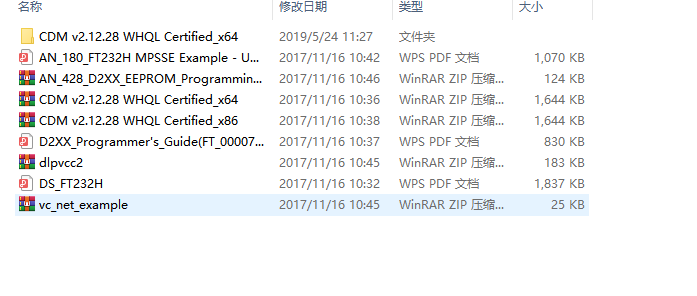

4.1 安裝FTDI D2xx driver

在05_芯片手冊\ft232h文件夾中可以找到CDM v2.12.28 WHQL Certified_x64.zip,將其解壓。

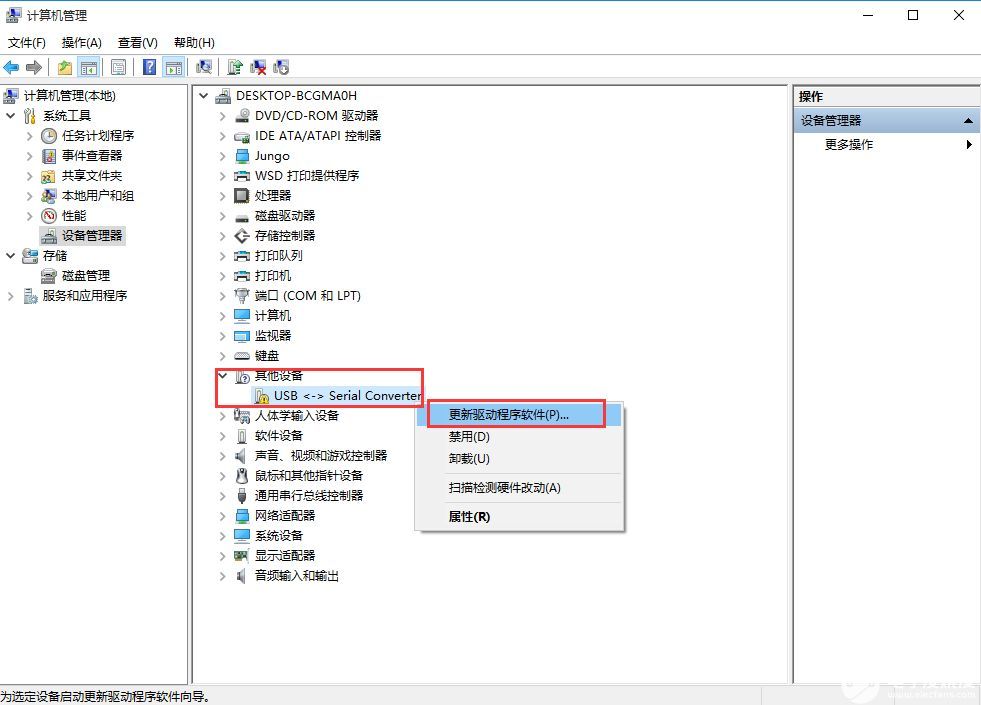

取出開發板,連接上開發板的USB接口,打開電源

打開設備管理器,出現新設備,右鍵點擊更新驅動程序軟件

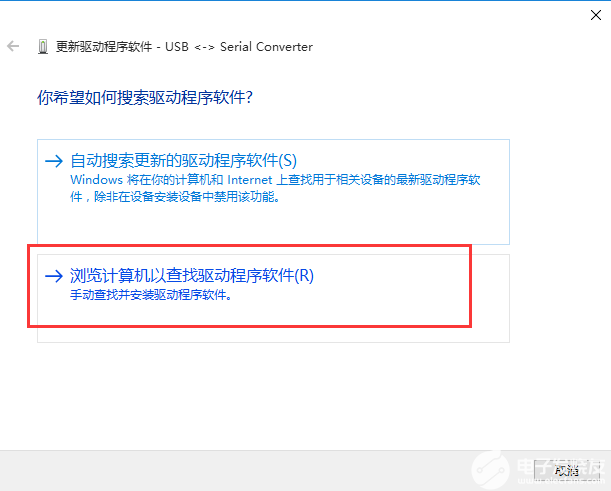

點擊瀏覽計算機以查找驅動程序軟件

點擊瀏覽找到解壓的文件夾,點擊確定,并點擊下一步。

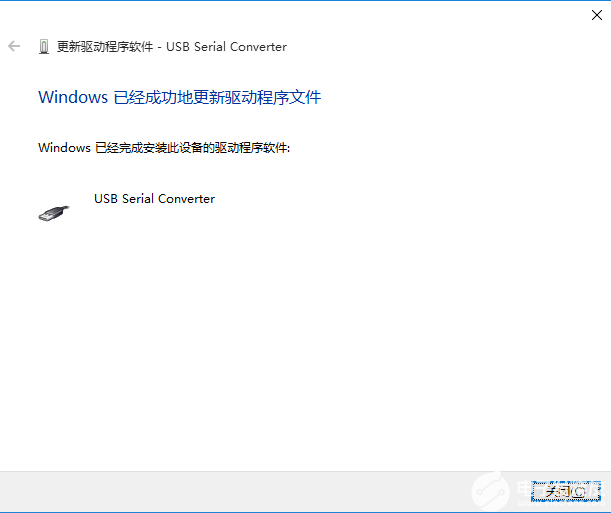

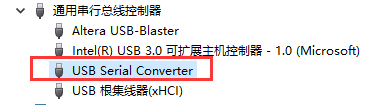

成功安裝驅動后如下圖:

可以看到出現 USB Serial Converter設備

4.2 實驗現象

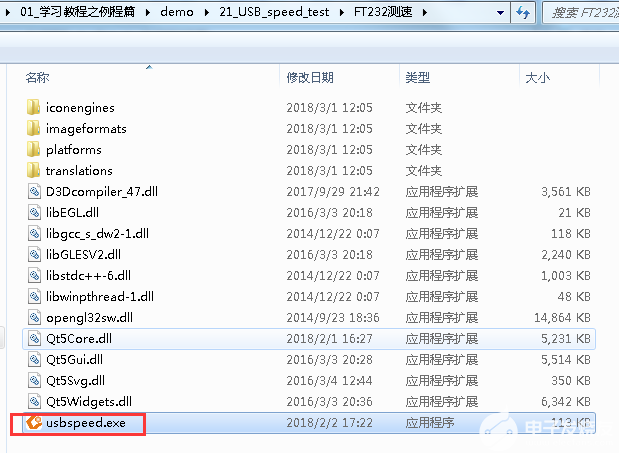

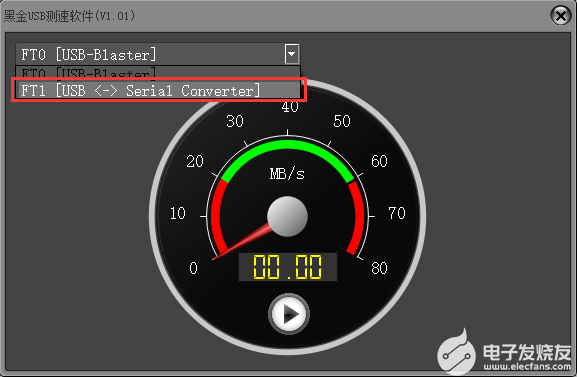

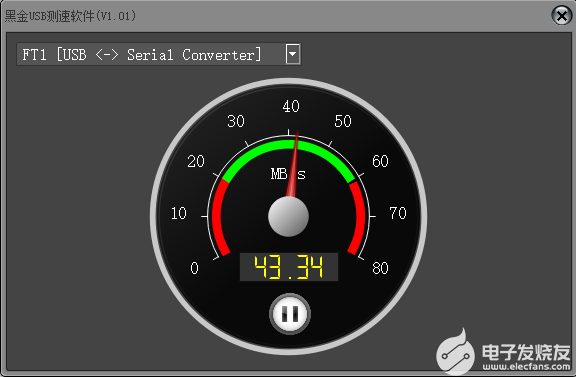

將程序下載到FPGA中,找到上位機測速軟件,打開軟件

選擇USB設備,點擊開始按鈕

可以看到讀寫速度在40MB/s附近變動,點擊暫停按鈕可停止測速。

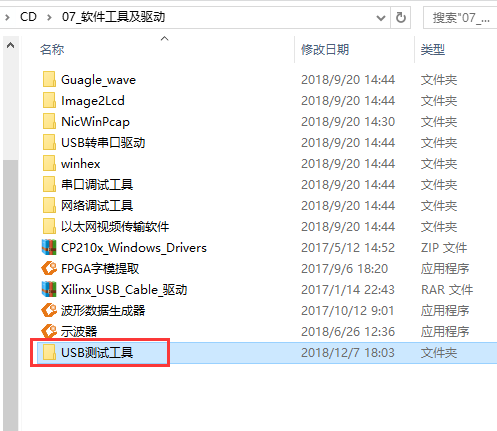

有些同學想要看看USB傳輸的數據,在這里我們提供 了“USB測試工具“,工具在下圖中位置:

操作如下:

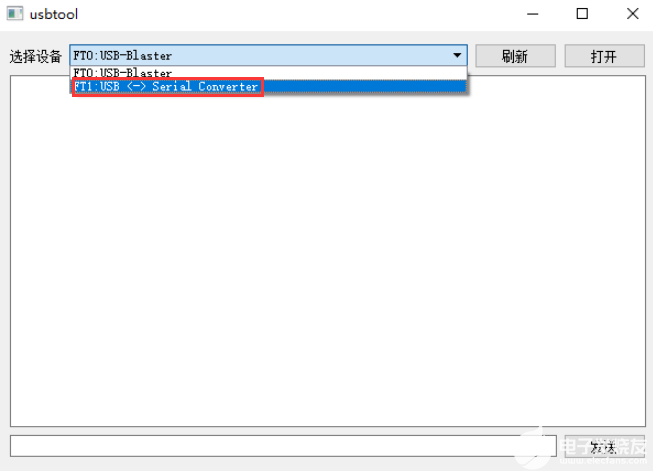

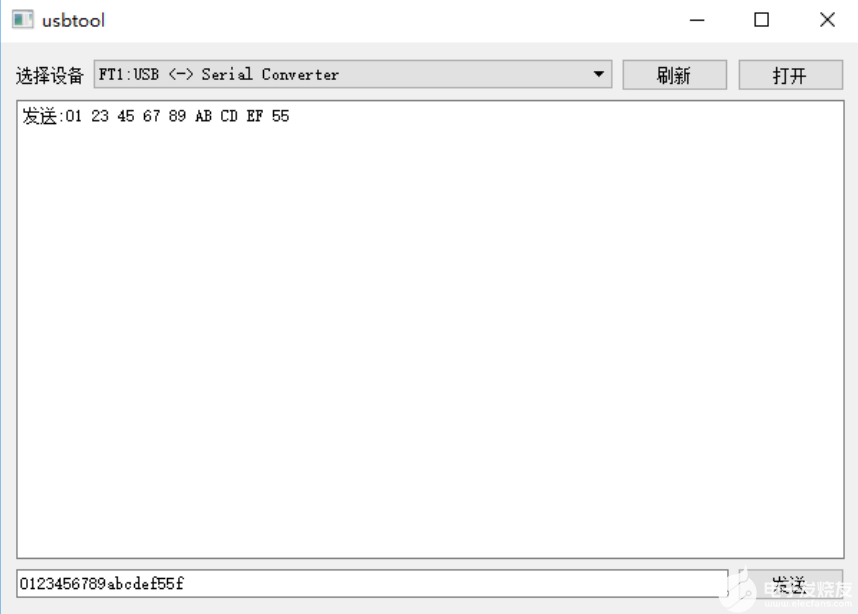

1)首先確保程序(與測速軟件一致)已下載到FPGA中,連接好USB線,找到上位機測速軟件并打開,在選擇設備下拉框里找到USB 設備, 如果沒有顯示 USB 設備, 點擊“刷新” 按鈕 之后選擇好設備, 點擊“打開” 按鈕。如下圖:

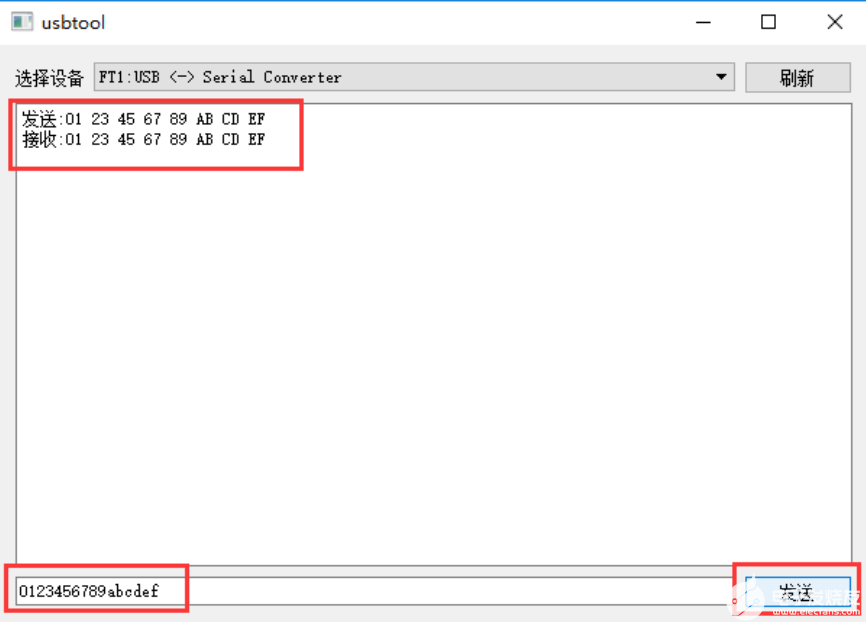

2)在數據輸入框輸入十六進制數據, 再點擊發送, 可以在顯示窗口看到發送和接收的數據, 進行數據對比, 驗證正確性。

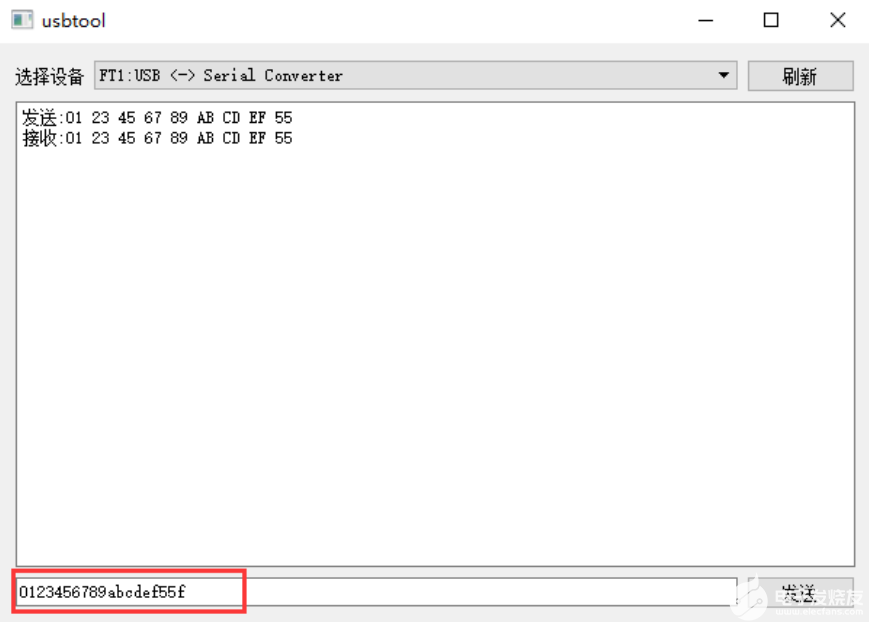

在這里需要注意下:發送數據需要為偶數個,否則上位機會截取偶數個數據發送, 如下圖, 最后一個數據 f 并沒有發送出去。

3)“刷新” 按鈕類似于關閉端口, 點擊“刷新” 按鈕后, 發送數據, 不會有反應, 需要點擊

“打開” 按鈕打開 USB 設備。

5. 總結

本實驗介紹了FT232H芯片FT245 FIFO模式的讀寫測速,大家可以結合各自的應用編寫上位機程序實現所需功能。

-

FPGA

+關注

關注

1620文章

21468瀏覽量

597928 -

usb

+關注

關注

60文章

7730瀏覽量

261740 -

程序

+關注

關注

114文章

3688瀏覽量

80206 -

uart

+關注

關注

22文章

1180瀏覽量

100692 -

紫光同創

+關注

關注

5文章

76瀏覽量

27401

發布評論請先 登錄

相關推薦

2024新品|紫光同創盤古系列FPGA開發板套件,100%國產化方案

紫光同創簡介

「正點原子Linux連載第二十八章多點電容觸摸屏實驗

火力發電廠水汽分析方法 第二十八部分:有機物的測定(紫外吸收

第二十八講 數模和模數轉換器

模擬電路網絡課件 第二十八節:集成電路運算放大器的參數

HDLBits:在線學習 Verilog (二十八 · Problem 135-139)

stm32溫濕度傳感器報告_「正點原子NANO STM32開發板資料連載」第二十八章 DHT11 數字溫濕度傳感器實驗...

鐳拓新款激光圓管切割機亮相第二十八屆中國五金博覽會

【紫光同創國產FPGA教程】【第二十八章】USB雙向測速例程

【紫光同創國產FPGA教程】【第二十八章】USB雙向測速例程

評論