0 引言

飛行器的工作狀態參數和環境參數主要通過無線遙測和回收遙測獲得,是評定飛行器性能和分析飛行器故障的依據[1]。隨著航天技術的發展,飛行器內部的工作參數越發復雜,遙測數據的信息量越來越大,遙測系統現有的存儲能力和信道帶寬已經很難滿足如此大數據量的存儲、傳輸要求。考慮到技術、成本等條件的限制,一味增加信道帶寬和存儲器的容量是不現實的。目前,數據壓縮技術被廣泛應用于遙測系統[2]。根據遙測數據的特點,采用合適的算法對大數據量的遙測數據進行編碼壓縮,不僅減輕了遙測系統數據存儲的壓力,也降低了對信道帶寬的要求,提高了通信效率。

遙測噪聲信號的頻率和幅度變化很大且無規則,信號的相關性差,為反映信號的完整特性,需要較高的采樣頻率,這樣就會產生很大的數據量。為有效地完成對噪聲信號的測量,這里采用ARC(算術編碼)算法對噪聲數據進行無損壓縮,以DSP+FPGA為硬件平臺[3],充分利用FPGA高速、并行的特性和DSP在算法實現上的優勢,很好地實現了對遙測噪聲數據的實時、無損壓縮。

1 系統設計

系統整體設計框圖如圖1所示,由噪聲傳感器采集的噪聲信號經調理電路濾波、放大后,進行A/D轉換得到量化噪聲數據;FPGA將噪聲數據寫入內部8 KB FIFO,直到FIFO達到半滿[4],DSP才會讀取噪聲數據進行算術編碼;編碼壓縮后的噪聲數據先是被DSP緩存至SDRAM,然后通過McBSP串口發送到FPGA,FPGA通過內建的4 KB FIFO對接收的壓縮數據進行緩沖;422通信控制模塊會接收讀數命令并在4 KB FIFO達到半滿時按照HDLC協議的要求將壓縮數據傳輸到外部設備進行存儲、傳輸和分析等操作。

2 數模轉換電路設計

噪聲信號的模數轉換采用TI公司的ADS8365芯片實現。它是16位6通道并行A/D,最高采樣率可達250 kS/s,完全滿足對4路噪聲信號進行27 kHz采樣的要求。

ADS8365的6個模擬輸入通道可分為3組,分別為A、B和C組[5]。每組都有一個保持信號(分別為HOLDA、HOLDB和HOLDC),用于啟動各組的A/D轉換。6個通道可以進行同步并行采樣和轉換。當ADS8365的HOLDX保持20 ns的低電平后開始轉換。當轉換結果被存入輸出寄存器后,引腳EOC的輸出將保持半個時鐘周期的低電平,以提示FPGA進行轉換結果的接收,FPGA通過置RD和CS為低電平使數據通過并行輸出總線讀出。

ADS8365的數據的讀出模式有3種,分別是:直接地址讀取、FIFO讀取、循環讀取,是由地址/模式信號A0、A1和A2來選擇的[6]。本系統FPGA將數據讀出配置為FIFO讀取模式。A/D轉換電路如圖2所示。

3 FPGA與DSP通信設計

FPGA控制ADS8365完成對4路噪聲信號的A/D轉換,各路量化數據加入通道標志后依次寫入FPGA內部FIFO。當FIFO達到半滿后,通知DSP讀取2 048 B數據進行編碼,編碼時間最長為40 ms,平均20 ms。DSP在編碼過程中不能與FPGA進行數據通信,FPGA要對由A/D產生的量化數據進行緩存。按最長耗時40 ms計算,每路27 kHz的采樣率會產生為4.32 K個采樣點。采用16位FIFO,則FIFO的深度應大于4 320,這里為增加可靠性,設計FIFO深度為8 192。

FPGA內部FIFO由Block RAM構建,其與DSP EMIF接口的連接如圖3所示。

噪聲數據經DSP壓縮后可以通過并行EMIF總線傳輸至FPGA。但為降低數據傳輸誤碼率,提高系統穩定性,本設計采用DSP的McBSP0串口將壓縮后的數據以串行數據流的方式傳送至FPGA。McBSP0傳輸單元的大小設置為48 bit,包括4 bit起始位、32位數據位和12 bit停止位。FPGA將串行接收的壓縮數據轉換成8 bit并行數據并將其寫入到內部4 KB FIFO中。FPGA通過422接口與外部設備通信,在接收到讀數命令后判斷4 KB FIFO是否達到半滿。如果FIFO達到半滿,就讀取FIFO中的數據,并進行HDLC協議編碼和幀格式編碼后發送出去;否則采用填充幀技術,將預先定義好的一組固定幀結構數據發送給外部設備。

4 DSP程序設計

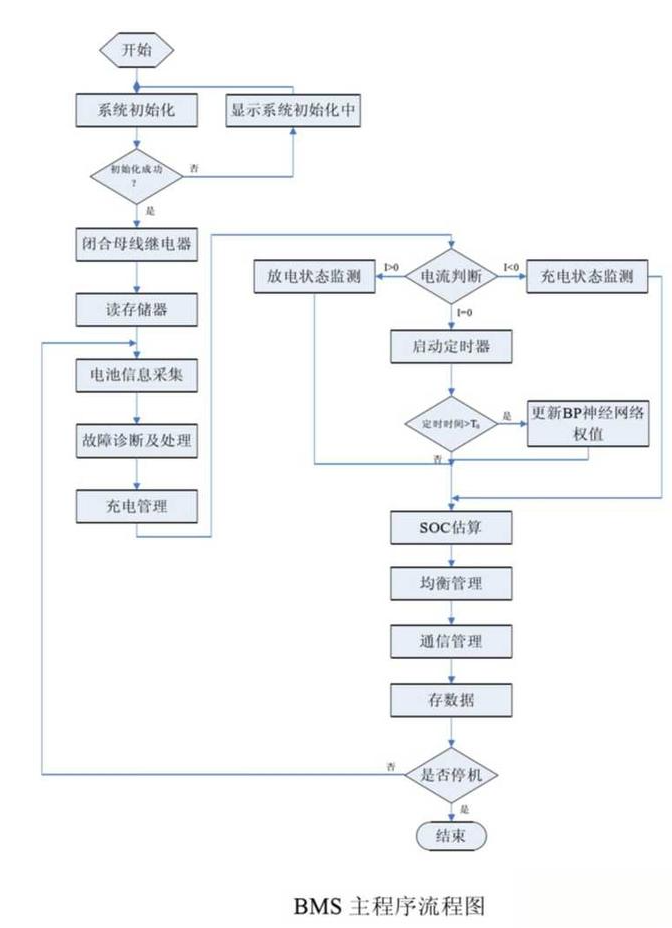

基于C語言的各種常見壓縮算法的開發都已很成熟,ARC算法的源程序也容易調研,算法的具體實現過程在此不再贅述。本設計將ARC源程序移植到DSP中實現算法的壓縮功能,DSP上電啟動或者復位后,從 Flash中加載程序,進入主函數main()完成外部FIFO數據讀入、啟動ARC壓縮,讀寫SDRAM和數據輸出等工作工作。程序流程如圖4所示。

當DSP檢測到外部8 KB FIFO半滿信號后會讀取2 048 B噪聲數據到內部4個緩存中,由于4路噪聲信號采樣時僅相差一個采樣點,故各路噪聲數據相差一個字節。DSP內4路噪聲數據對應的緩存幾乎同時達到2 048 B, DSP需要同時對4路噪聲數據進行編碼,這會使DSP長時間處于繁忙狀態而不能進行采樣數據的讀入和壓縮數據的輸出,容易引起FPGA內部8 KB FIFO溢出和4 KB FIFO的讀空。

如果采用中斷方式打斷壓縮進程、讀入量化數據和輸出壓縮數據,則可能造成DSP內數據量過大,超出DSP片內RAM容量。這里將DSP內的4個緩存預設初值分別設為1 536 B、1 024 B、512 B和0 B,DSP每次從FPGA內部FIFO中讀取2 048 B數據,則DSP內每個緩存增加512 B。DAP第一次讀取FIFO,第一路噪聲數據對應的緩存達到2 048 B,進行編碼、輸出后,該緩存數據量變為0。

此時,4路緩存中的字節數變為0、1 536、1 024和512。DSP第二次讀取FIFO后,第2路數據緩存達到2 048 B,完成對第二路噪聲數據的編碼、傳輸。如此循環執行,實現每次只對一路噪聲數據進行處理,保證了數據的連續均勻流動。

5 測試驗證與分析

采用測試系統對設計的噪聲壓縮裝置的性能進行了驗證,測試系統的測試臺向噪聲壓縮裝置提供4路信號來模擬噪聲傳感器的輸入,噪聲壓縮裝置對輸入信號完成壓縮后將數據回傳給測試臺并由測試臺將壓縮數據上傳至上位機。上位機對壓縮數據先進行數據結構分析,如果數據結構正確,就按照HDLC協議將數據解碼并去除填充數據和幀標識。之后根據ARC算法將噪聲數據解壓還原并分離得到各路噪聲原始數據,上位機對各路噪聲原始數據進行處理,還原出各路信號的原始波形。

給噪聲無損壓縮裝置的噪聲信號輸入接口輸入信號,其中第1路為幅值2 V、頻率25 Hz的正弦波,第2路為幅值3 V、頻率25 Hz的正弦波,第3路為幅值2 V、頻率50 Hz的正弦波,第4路為幅值2 V、頻率25 Hz的矩形波。測試結果如圖5~圖8所示。

從測試結果可以看出,同一種信號幅值、頻率不同,它們的壓縮去除率會存在差異;幅值、頻率相同,不同種類信號的壓縮去除率也會不同。對標準信號源,該壓縮裝置的壓縮去除率接近90%。圖9為噪聲壓縮裝置對實際噪聲信號壓縮后由上位機還原得到的波形,可以看出該壓縮裝置對實際噪聲信號的壓縮去除率能達到50%以上。

6 結論

數據壓縮技術在遙測系統中對包括噪聲信號在內的速變參數的處理已經很常見,本文設計的系統以FPGA+DSP為硬件核心,其中,FPGA主要完成對模/數轉換和數據通信的控制,噪聲數據的編碼無損壓縮則是在DSP中實現的。同時,采用不同信號對設計的噪聲壓縮裝置進行了測試,得到了理想的效果。本文提出的設計思路對其他類型數據的壓縮也有一定的借鑒意義。

參考文獻

[1] 謝紅衛,張明.航天測控系統[M].長沙:國防科技大學出版社,2000.

[2] 劉文怡.遙測速變數據無損壓縮時空性能優化設計與應用[D].太原:中北大學,2009.

[3] 冷佳鵬,劉文怡.一種遙測數據實時壓縮系統[J].電子技術應用,2013,39(4):72-74.

[4] 孟楠,楊巖飛,劉文怡.遙測速變數據實時無損壓縮技術研究[J].科學技術與工程,2013,13(33):9983-9986.

[5] 張峰,趙慧昌,石現峰.便攜式多通道振動信號分析儀數采模塊設計[J].自動化與儀表,2014(1):15-18.

[6] 康偉,路秀芬,詹哲軍.基于ADS8365的高速同步數據采集系統[J].電腦開發與應用,2009,22(4):48-51.

編輯:jq

-

傳感器

+關注

關注

2548文章

50705瀏覽量

752084 -

FPGA

+關注

關注

1626文章

21674瀏覽量

601936 -

噪聲

+關注

關注

13文章

1118瀏覽量

47369

發布評論請先 登錄

相關推薦

分析遙測噪聲數據無損壓縮關鍵技術實現

分析遙測噪聲數據無損壓縮關鍵技術實現

評論