一、白平衡介紹

對于白平衡基本概念的詳細介紹請查看文章《白平衡初探》,白平衡算法主要的作用是將偏暖或者偏冷的色調自動恢復到正常色調,是圖像看起來更加色彩飽滿正常。

如上圖所示,左1色溫偏冷,中間色溫正常,右一色溫偏暖。上圖比較直觀的展示了色溫的概念。偏冷的色溫會給人一種還冷的感覺,偏暖的色溫會給人一種溫暖的感覺。

二、白平衡算法以及matlab實現

1)原始的灰度世界算法

灰度世界算法(Gray World)是以灰度世界假設為基礎的,該假設認為對于一幅有著大量色彩變化的圖像, R、 G、 B 三個分量的平均值趨于同一個灰度K。一般有兩種方法來確定該灰度。

(1)直接給定為固定值, 取其各通道最大值的一半,即取為127或128;

(2)令 K = (Raver+Gaver+Baver)/3,其中Raver,Gaver,Baver分別表示紅、 綠、 藍三個通道的平均值。

算法的第二步是分別計算各通道的增益:

Kr=K/Raver;

Kg=K/Gaver;

Kb=K/Baver;

算法第三步為根據Von Kries 對角模型,對于圖像中的每個像素R、G、B,計算其結果值:

Rnew = R * Kr;

Gnew = G * Kg;

Bnew = B * Kb;

對于上式,計算中可能會存在溢出(》255,不會出現小于0的)現象,處理方式有兩種。

a、 直接將像素設置為255,這可能會造成圖像整體偏白。

b、 計算所有Rnew、Gnew、Bnew的最大值,然后利用該最大值將將計算后數據重新線性映射到[0,255]內。實踐證明這種方式將會使圖像整體偏暗,建議采用第一種方案。

2)完美反射算法

原理:完美全反射理論perfect Reflector假設圖像上最亮點就是白點,并以此白點為參考對圖像進行自動白平衡,最亮點定義為R+G+B的最大值,具體編碼步驟如下:

(1)計算每個像素的RGB之和,并保存到一臨時內存塊中。

(2)按R+G+B值的大小計算出其前10%或其他Ratio的白色參考點的的閾值T。

(3)遍歷圖像中的每個點,計算其中R+G+B值大于T的所有點的RGB分量的累積和的平均值。

(4)對每個點將像素量化到[0,255]之間。

3)動態閾值法

(1)。 把圖像w*h從RGB空間轉換到YCrCb空間。

(2)。 選擇參考白色點:

a. 把圖像分成寬高比為4:3個塊(塊數可選)。

b. 對每個塊,分別計算Cr,Cb的平均值Mr,Mb。

c. 對每個塊,根據Mr,Mb,用下面公式分別計算Cr,Cb的方差Dr,Db。

d. 判定每個塊的近白區域(near-white region)。

判別表達式為:

設一個“參考白色點”的亮度矩陣RL,大小為w*h。

若符合判別式,則作為“參考白色點”,并把該點(i,j)的亮度(Y分量)值賦給RL(i,j);

若不符合,則該點的RL(i,j)值為0。

(3)。 選取參考“參考白色點”中最大的10%的亮度(Y分量)值,并選取其中的最小值Lu_min.

(4)。 調整RL,若RL(i,j)《Lu_min, RL(i,j)=0; 否則,RL(i,j)=1;

(5)。 分別把R,G,B與RL相乘,得到R2,G2,B2。 分別計算R2,G2,B2的平均值,Rav,Gav,Bav;

(6)。 得到調整增益:

Ymax=double(max(max(Y)))/5;

Rgain=Ymax/Rav;

Ggain=Ymax/Gav;

Bgain=Ymax/Bav;

(7)。 調整原圖像:

Ro= R*Rgain;

Go= G*Ggain;

Bo= B*Bgain;

FPGA的實現采用灰度世界算法。

Matlab代碼:

close allclear allclcI=imread(‘test1.jpg’);[H,W,L]=size(I);%得到圖像長寬高Rsum = 0;Gsum = 0;Bsum = 0;Rsum = double(Rsum);Gsum = double(Gsum);Bsum = double(Bsum);for i = 1 : H for j = 1 :W Rsum = Rsum + double(I(i,j,1)); Gsum = Gsum + double(I(i,j,2)); Bsum = Bsum + double(I(i,j,3)); endendRaver = Rsum / (H*W);Gaver = Gsum / (H*W);Baver = Bsum / (H*W);%K=128;%第一種K取值方法K = (Raver+Gaver+Baver)/3;%第二種方法Rgain = K / Raver;Ggain = K / Gaver;Bgain = K / Baver;Iwb(:,:,1) = I(:,:,1) * Rgain;Iwb(:,:,2) = I(:,:,2) * Ggain;Iwb(:,:,3) = I(:,:,3) * Bgain;imwrite(Iwb,‘Result1.jpg’);figure(1),subplot(121),imshow(I),title(‘原始圖像’);subplot(122),imshow(Iwb),title(‘自動白平衡圖像’);

效果展示:

三、FPGA實現自動白平衡灰度世界法

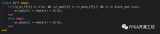

灰度世界法Verilog代碼:

/**********************************copyright@FPGA OPEN SOURCE STUDIO微信公眾號:FPGA開源工作室Algorithm:Auto White balance Gray World 800X600X255=480000***********************************/`define XLEN 32`define N(n) [(n)-1:0]module White_balance#( parameter DW = 24 )( input pixelclk, input reset_n, input [DW-1:0] din, //rgb in input i_hsync, input i_vsync, input i_de,

output [DW-1:0] dout, //gray out output o_hsync, output o_vsync, output o_de );

localparam STAGE_LIST = 32‘h0101_0101;//32’b00000000_00000000_00000000_00000000;localparam divisor = 32‘h0007_5300;//800*600localparam divisorK = 32’h0000_0003;//800*600

wire [7:0] R,G,B;reg [27:0] sumr,sumg,sumb;reg [27:0] sumr_r,sumg_r,sumb_r;wire [9:0] Kave;wire [7:0] K;

wire Rack;wire `N(`XLEN) Rquo,Rrem;

wire Gack;wire `N(`XLEN) Gquo,Grem;

wire Back;wire `N(`XLEN) Bquo,Brem;

wire Kack;wire `N(`XLEN) Kquo,Krem;

wire GRack;wire `N(`XLEN) GRquo,GRrem;

wire GGack;wire `N(`XLEN) GGquo,GGrem;

wire GBack;wire `N(`XLEN) GBquo,GBrem;

reg [39:0] R_r,G_r,B_r;wire [7:0] RO,GO,BO;

reg hsync_r1;reg vsync_r1;reg de_r1;

reg i_vsync_r;reg vsync_neg_r;

wire vsync_neg=(i_vsync_r&(~i_vsync));

assign Kave=(Rquo+Gquo+Bquo);assign K=Kquo[7:0];

assign R=din[23:16];assign G=din[15:8];assign B=din[7:0];

assign o_hsync = hsync_r1;assign o_vsync = vsync_r1;assign o_de = de_r1;

assign RO=(R_r[18:10]》255)?255:R_r[17:10];assign GO=(G_r[18:10]》255)?255:G_r[17:10];assign BO=(B_r[18:10]》255)?255:B_r[17:10];assign dout={RO,GO,BO};

//synchronizationalways @(posedge pixelclk) begin hsync_r1 《= i_hsync; vsync_r1 《= i_vsync; de_r1 《= i_de;end

always @(posedge pixelclk or negedge reset_n)begin if(!reset_n)begin sumr《=28‘d0;《 span=“”》 sumg《=28’d0;《 span=“”》 sumb《=28‘d0;《 span=“”》 sumr_r《=28’d0;《 span=“”》 sumg_r《=28‘d0;《 span=“”》 sumb_r《=28’d0;《 span=“”》 i_vsync_r《=1‘b0;《 span=“”》 vsync_neg_r《=1’b0;《 span=“”》 R_r《=40‘b0;《 span=“”》 G_r《=40’b0;《 span=“”》 B_r《=40‘b0;《 span=“”》 end else begin i_vsync_r《=i_vsync;《 span=“”》 vsync_neg_r《=vsync_neg;《 span=“”》

R_r《=r*grquo;《 span=“”》 G_r《=g*ggquo;《 span=“”》 B_r《=b*gbquo;《 span=“”》

if(vsync_neg==1’b1) begin sumr_r《=sumr;《 span=“”》 sumg_r《=sumg;《 span=“”》 sumb_r《=sumb;《 span=“”》 end

if(i_vsync==1‘b1) begin if(i_de==1’b1) begin sumr《=sumr+r;《 span=“”》 sumg《=sumg+g;《 span=“”》 sumb《=sumb+b;《 span=“”》 end else begin sumr《=sumr;《 span=“”》 sumg《=sumg;《 span=“”》 sumb《=sumb;《 span=“”》 end end else begin sumr《=28‘d0;《 span=“”》 sumg《=28’d0;《 span=“”》 sumb《=28‘d0;《 span=“”》 end endend

//Rave divfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divR ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {4’b0,sumr_r} ), .b ( divisor ), .vld ( vsync_neg_r ),

.quo ( Rquo ), .rem ( Rrem ), .ack ( Rack )

);

//Gave divfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divG ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {4‘b0,sumg_r} ), .b ( divisor ), .vld ( vsync_neg_r ),

.quo ( Gquo ), .rem ( Grem ), .ack ( Gack )

);

//Bave divfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divB ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {4’b0,sumb_r} ), .b ( divisor ), .vld ( vsync_neg_r ),

.quo ( Bquo ), .rem ( Brem ), .ack ( Back )

);

//Kdivfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divK ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {22‘b0,Kave} ), .b ( divisorK ), .vld ( Back ),

.quo ( Kquo ), .rem ( Krem ), .ack ( Kack )

);

//RGaindivfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divGR ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {14’b0,K,10‘b0} ), .b ( Rquo ), .vld ( Kack ),

.quo ( GRquo ), .rem ( GRrem ), .ack ( GRack )

);

//GGaindivfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divGG ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {14’b0,K,10‘b0} ), .b ( Gquo ), .vld ( Kack ),

.quo ( GGquo ), .rem ( GGrem ), .ack ( GGack )

);

//BGAINdivfunc #( .XLEN ( `XLEN ), .STAGE_LIST ( STAGE_LIST )

) i_divGB ( .clk ( pixelclk ), .rst ( ~reset_n ),

.a ( {14’b0,K,10‘b0} ), .b ( Bquo ), .vld ( Kack ),

.quo ( GBquo ), .rem ( GBrem ), .ack ( GBack )

);

endmodule

1)仿真效果

原始圖像

經過灰度世界法的白平衡仿真效果

2)下板驗證模型以及實現效果

下板驗證圖像由筆記本電腦通過HDMI輸入到FPGA芯片,經過FPGA算法處理后在通過HDMI將圖像送到顯示屏展示處理效果。

視

原文標題:基于FPGA的自動白平衡算法的實現(附代碼)

文章出處:【微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602047

原文標題:基于FPGA的自動白平衡算法的實現(附代碼)

文章出處:【微信號:HXSLH1010101010,微信公眾號:FPGA技術江湖】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+介紹基礎硬件算法模塊

【「從算法到電路—數字芯片算法的電路實現」閱讀體驗】+一本介紹基礎硬件算法模塊實現的好書

FPGA在自動駕駛領域有哪些優勢?

FPGA在自動駕駛領域有哪些應用?

凱茉銳電子|索尼FCB-EV9500M點聚焦、點曝光與點白平衡的定義和功能

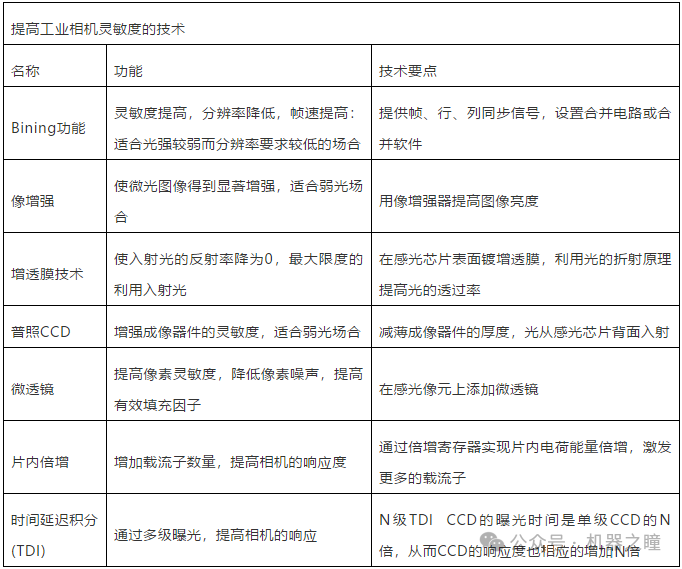

工業相機相關知識科普

什么是白平衡?白平衡的作用

怎么用FPGA做算法 如何在FPGA上實現最大公約數算法

浮點LMS算法的FPGA實現

fpga布局布線算法加速

基于FPGA的平衡小車設計

基于FPGA自動白平衡算法的介紹和實現

基于FPGA自動白平衡算法的介紹和實現

評論