自從 Vitis 發布后,Xilinx 在 Github 上持續開源了很多資源,方便開發者進行自己的設計,減少產品上市時間。所以本期文章我們來看下如何獲取和使用 Github 上的開放資源。

1. 在 Vitis IDE 上的使用方法:

以 Vitis_example 為例,

Vitis IDE 是基于 eclipse 開發而成的,Xilinx 在此基礎上添加了很多自己的功能。在 Vitis IDE上使用 Vitis example 的方法相對簡單,具體的操作如下:

1)。 Vitis IDE 下載方式

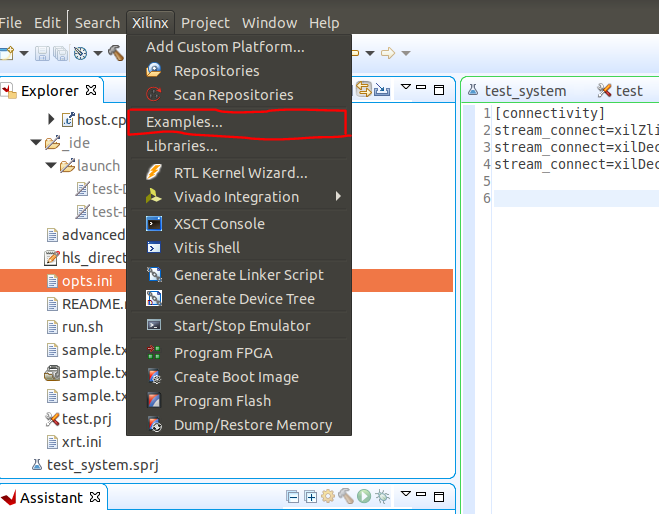

Xilinx-》Examples-》Download:

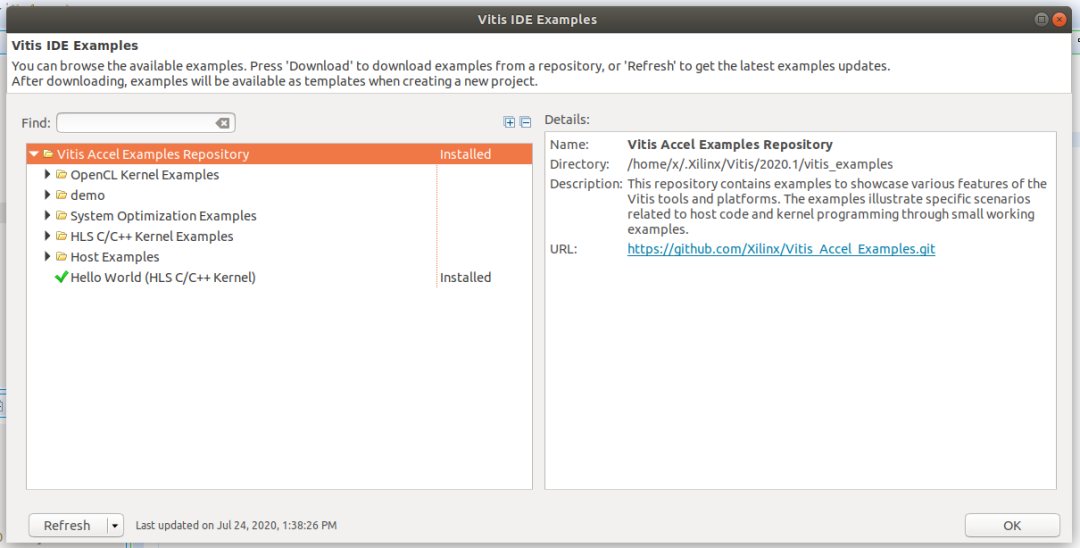

等待一段時間后,下載完成后的界面如下圖所示。

有的用戶會遇到下載失敗的情況,最典型的錯誤: fatal unableto find remote helper for ‘https’這個其實跟git的設置或缺少庫有關,可以參考

如果還有其他問題,也可以在我們的中文論壇上尋求幫助。

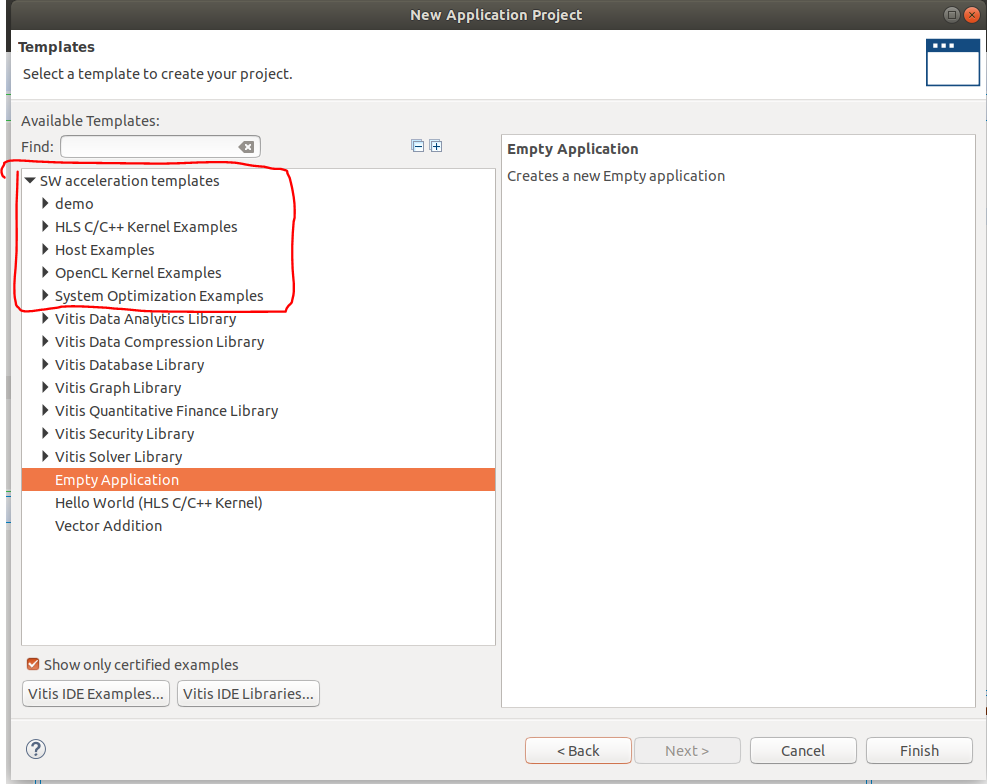

2)。 當你新建application工程之后你就會看到下載的 exampledesign,選擇并點擊 finish 即可。

2. 基于makefile的使用方法:

有些軟件開發者更趨向基于 makefile 的命令行方式來進行開發,它的優點是更加靈活,但是對Vitis的理解有要求,具體如下:

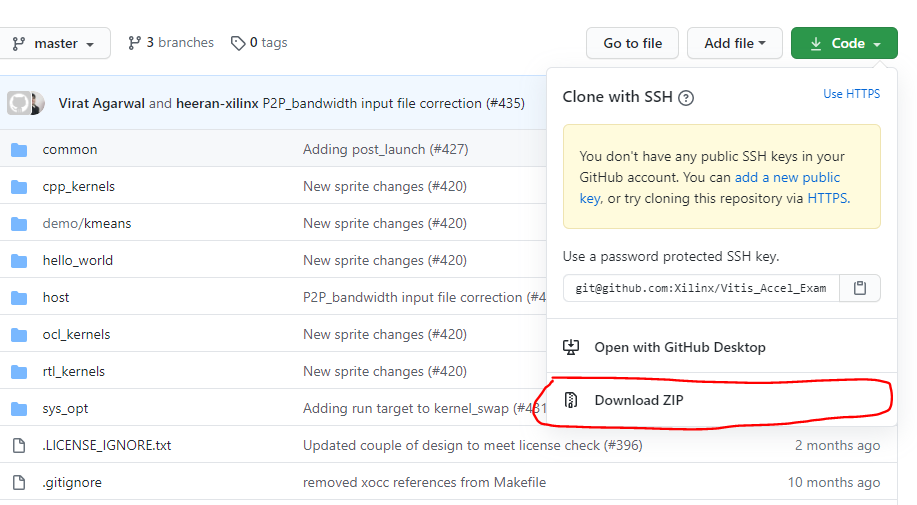

1)。 下載 example design:

或使用命令:

git clone https://github.com/Xilinx/Vitis_Accel_Examples.git

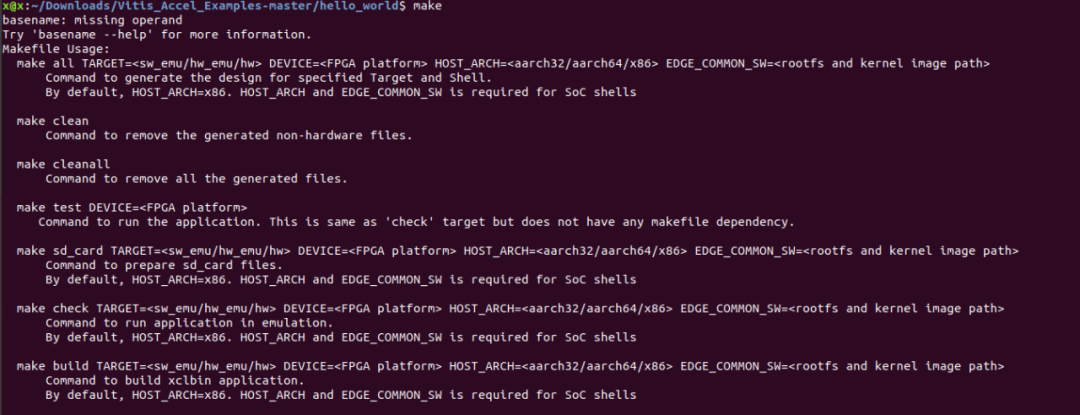

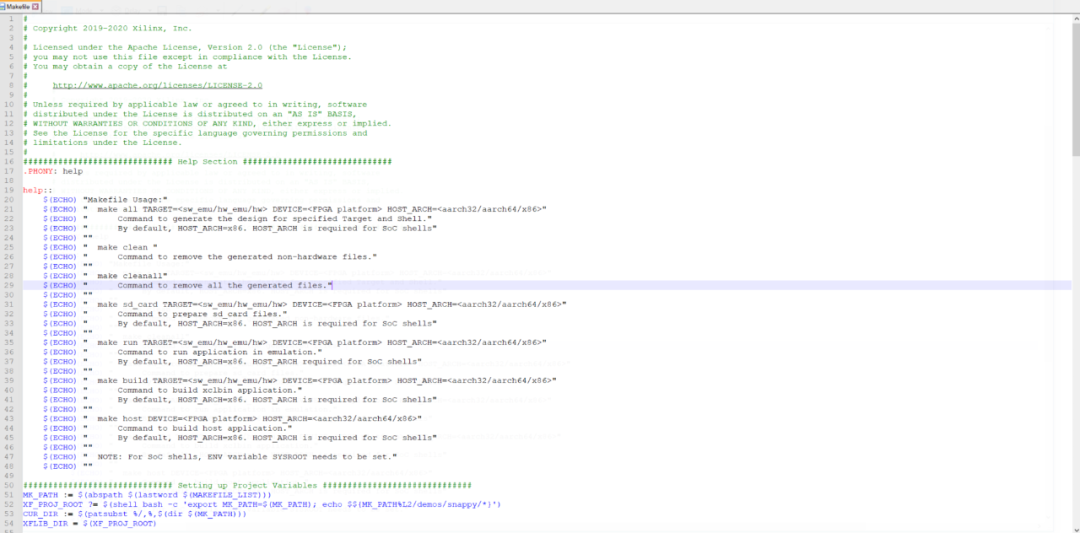

2)。 進入文件目錄,例如 hello_world,可以先輸入 make,獲取 make 指令的用途和選項:

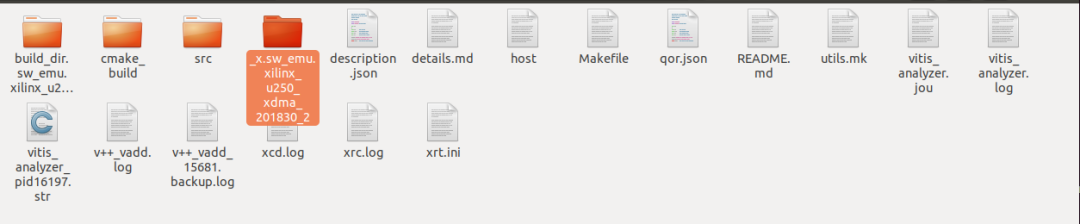

3)。 根據我們安裝的 platform,在這里我們使用的是 u50 板卡。我們可以該目錄下輸入:

make all TARGET=sw_emu DEVICE=xilinx_u50_xdma_201920_3

可以得到示例工程生成的目標文件。

當然在此之前我們要確認這個 example design 支持的 platform 有沒有限制,所以推薦先閱讀一下各個示例的 README.rst

https://github.com/Xilinx/Vitis_Accel_Examples/tree/master/hello_world

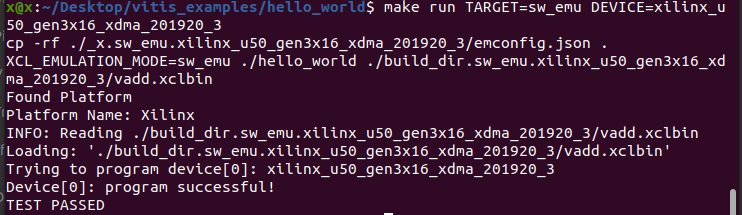

4)。 當我們生成完所需的目標文件后,我們可以進行軟件仿真(硬件仿真,硬件)運行。可以輸入:

make run TARGET=sw_emu DEVICE=xilinx_u50_xdma_201920_3

會輸出如下:

可以看到 TEST PASSED,代表軟件仿真已經通過。

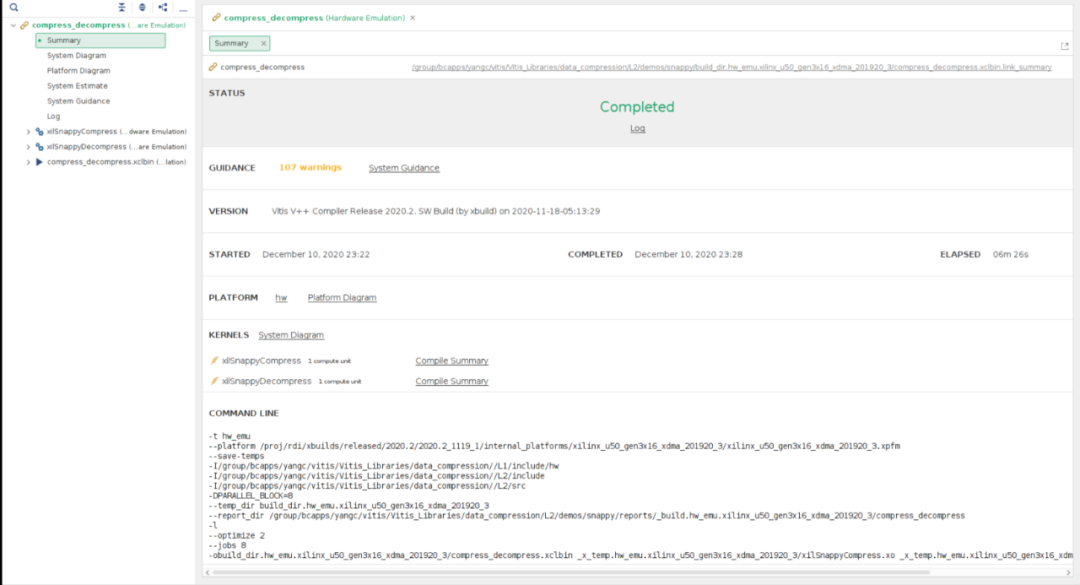

5)。 如果要觀察仿真的結果或者報告分析,我們在目標生成目錄下可以命令啟動 Vitisanalyzer (vitis acceleration 流程只支持 Linux 操作系統):

vitis_analyzer 。/

它會自動索引目錄下的 summary 文件,并且提供 GUI 化的可視界面,幫助用戶分析性能和評估板卡:

附:如果你對 V++ 熟悉的話,也可以根據自己的需求直接修改 makefile 文件和相關的 .ini 配置文件:

總結

以上就是使用 Vitis example 的兩類方法。

在前面圖片中 library 跟 example 出現在一起,Vitis library 是 Xilinx 提供的開源庫,更趨近于不同專業領域的開發方向

并且其提供了測試工程示例,具體使用方法跟 vitis example 類似。

編輯:lyn

-

GitHub

+關注

關注

3文章

461瀏覽量

16229 -

Vitis

+關注

關注

0文章

145瀏覽量

7310

原文標題:如何獲取 Github 上Xilinx Vitis, Vitis 庫等資源

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

上傳本地項目代碼到github

GitHub推出GitHub Models服務,賦能開發者智能選擇AI模型

如何在ESP8266上獲取并刷寫最新固件?

esp32無法燒錄github上的一個固件,為什么?

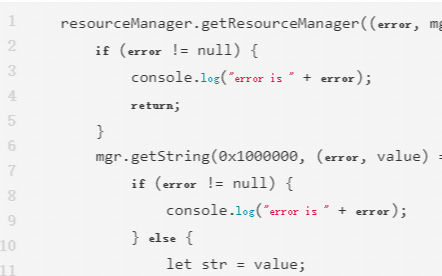

鴻蒙開發接口資源管理:【@ohos.resourceManager (資源管理)】

GitHub存在高危漏洞,黑客可利用進行惡意軟件分發

Sora短期不會向公眾開放 還處于反饋獲取階段

GitHub Copilot Enterprise全線向企業客戶開放,提供個性化定制服務

【米爾-全志T113-i開發板試用】3、使用golang獲取系統信息

使用modustoolbox_v3.0 創建XMC7200_kit的工程,但是在github上獲取一直失敗的原因?

GitHub入門與實踐

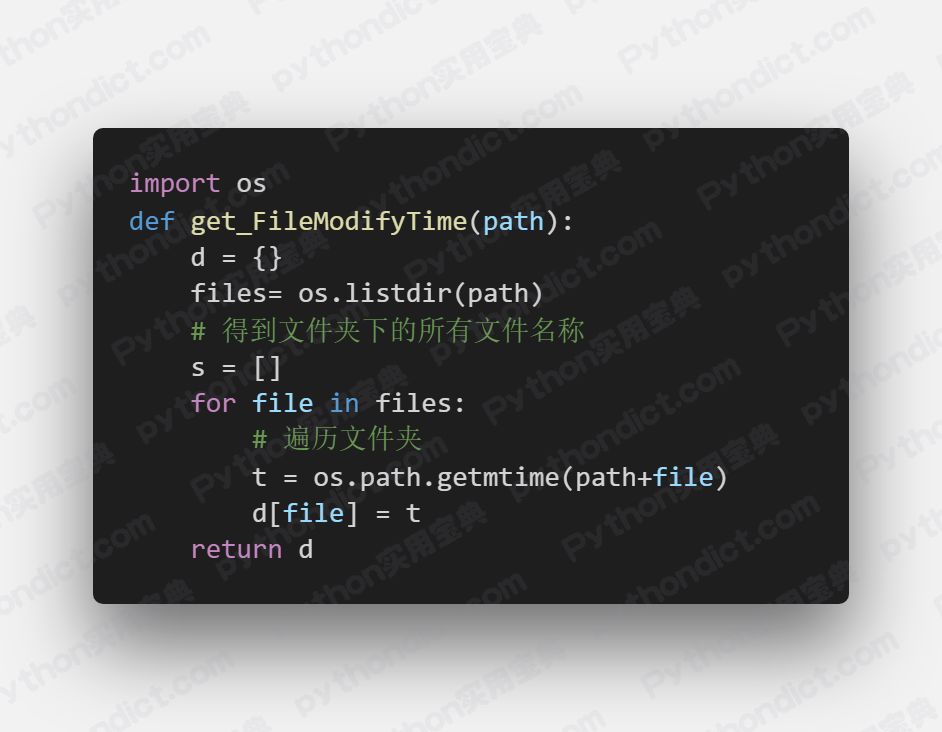

Python監控Github項目如何更新并自動下載

免費PLC學習文檔和資料一般可以在哪里獲取?

如何使用Github高效率的查找項目

如何獲取和使用Github上的開放資源

如何獲取和使用Github上的開放資源

評論