“IIC 協議與編程序列” 一文,我們為內部集成電路 (IIC) 協議的初學者們提供了有關該協議基礎知識和編程序列的詳細解釋。

在本篇博文中,我們將探討有關 AXI IIC 和 PS IIC 的自調試技巧。

PS IIC 編程序列調試:

控制器設置為 “主發射器 (Mastertransmitter)”。

在 Zynq-7000/Zynq UltraScale+ 器件中啟用 PS IIC。確保 SCL 頻率配置為 100 kHz 或 400 kHz。

設置主發射器控制器的控制寄存器。

檢查中斷是否已清除,并且已配置實際 SCL 的時鐘分頻器。

要測試與從設備的通信,請將從地址寫入 PS I2C 地址寄存器 (I2C_Address),然后將數據寫入 I2C_data_reg

HOLD 位應根據數據大小來處理。當數據大小小于 FIFO 深度時,請清除 HOLD 位以終止事務傳輸,并生成 STOP 位。

在中斷使能寄存器 (IER) 中使能 NACK 中斷后,即可通過 ISR 來監控從設備應答 (ACK)。

驗證 ISR 中的 COMP 標記位已置位。這樣即可確認數據傳輸成功。

如果主傳輸不成功,用戶可使用以下步驟進行調試:

確保控制寄存器中的配置正確無誤

檢查 ISR 中的 NACK 位,以確認從設備的響應

按上述方式謹慎處理 HOLD 位。否則,將導致 SCL 下拉直至超時為止

監控狀態寄存器中的 TXDV 位,檢查是否有任何暫掛數據正在等待傳輸

狀態寄存器中的“總線繁忙 (Bus busy)”位或 BA 位將有助于您了解數據傳輸期間的總線狀態。

控制器設置為 “主接收器 (Masterreceiver)”

與對應主發射器的步驟 1 相同,在 Zynq-7000/Zynq UltraScale+ 器件中啟用 PS IIC。確保 SCL 頻率配置為 100 kHz 或 400 kHz。

使用軟件應用來設置主接收器控制器的控制寄存器。

與對應主發射器的步驟 3 相同,檢查中斷是否已清除,并且已配置實際 SCL 的時鐘分頻器。

將讀取數據計數填入 PS IIC 的傳輸大小寄存器。如果傳輸大小大于 FIFO 深度,則啟用 HOLD 位。

將地址寫入從地址寄存器

等待數據接收完成,可通過檢查狀態寄存器的 RXDV 位來確認。

如果 RXDV = 0 且 ISR 中有任意中斷位處于置位狀態,則停止傳輸并報告錯誤。

同樣,如果 RXDV = 1 且 ISR 中有任意中斷位處于置位狀態,則停止傳輸并報告錯誤。

如果 RXDV=1 且未報告任何錯誤,則從 FIFO 讀取數據,直至狀態變為 RXDV=1 為止。如果尚未完成接收的剩余數據(來自從設備)小于 FIFO 深度,則清除 HOLD 位。

等待 ISR 中的 COMP 位變為置位狀態以完成傳輸。

以上對應編程序列的調試步驟適用于默認輪詢方法。

如果對主接收器使用中斷方法,則存在如下差異:

您需要在數據傳輸前啟用中斷

無需監控 RXDV 位,而需檢查 ISR 中的 DATA 位。

常見問題解答

在 IIS 中,何謂“超時”?

如果在任何時間點上,主設備或接入的從設備將 SCL 時鐘信號置于低位,且時間超過超時寄存器中指定的時間段,則會生成 [TO] 中斷位以避免出現停滯狀況。

如何將 PS IIC 復位?

寄存器 RST_LPD_IOU2 位 9 和 10 用于復位控制器

支持哪些模式?

主設備模式、從設備模式以及多重主設備模式。

注:在多重主設備模式下,所有主設備中的 SCL 頻率需保持相同。

支持哪些頻率?

僅支持 100 kHz 和 400 kHz。

用戶如何檢查總線錯誤?

在 ISR 寄存器中,監控總線上是否存在 ARB_LOST、NACK、RX_OVF 和 RX_UNF 錯誤。

如何區分 DATA 標記與 COMP 標記?

在 ISR 寄存器中,對應每讀取 14 字節數據,DATA 位就有一個觸發器,而 COMP 位則用于指示傳輸完成。

PS IIC 遵循何種規范?

NXP 規范UM10204

支持的最大數據發射率是多少?

255 個字節

AXI IIC 編程序列調試:

用戶可以使用以下讀寫操作來調試 AXI IIC IP,以了解協議是否正常工作。

快速獲取結果的首選選項是使用“動態”編程進行調試。

動態讀取操作:

此操作的最終目的是從從設備中讀取單一寄存器,以證明主從設備的功能是否正常。

使用寫入操作將 START + 從設備地址一起寫入 TX FIFO

將從設備的子寄存器地址寫入 TX FIFO

使用讀取操作將 RE-START + 從設備地址一起寫入 TX FIFO

將 STOP + 要從從設備讀取的字節數一起寫入 TX FIFO

使用控制寄存器來啟用控制器

輪詢 RX_FIFO_EMPTY 的狀態寄存器,以查看數據接收狀態(如果 RX_FIFO = 0,則數據已進入接收 FIFO 內)

如果 RX FIFO 中無數據,且 RX_FIFO_EMPTY 為 1,則可遵循以下步驟來了解問題:

如果由于從設備不響應而導致無法接收數據,那么原因可能是指定地址不存在任何從設備。請復查從設備地址是否正確。

如果您確認從設備地址正確無誤,請探測 SCL/SDA 以了解是否正在從從設備生成 ACK。

如果有來自從設備的 ACK,請以相同方式檢查子寄存器,以對通信進行調試。

檢查 TX_FIFO_Empty 標記,確認是否所有數據都已完成發射。

如果步驟 6 中未發現任何問題,則表示您可從從設備接收數據,請檢查是否已建立通信。

動態寫入操作:

使用寫入操作將 START + 從設備地址一起寫入 TX FIFO

將從設備的子寄存器地址寫入 TX FIFO

將除最后一個字節外的所有數據字節都寫入 TX FIFO

將 STOP + 最后一個數據字節寫入 TX FIFO

使用控制寄存器來啟用控制器

輪詢 TX_FIFO_EMPTY 的狀態寄存器,以判定數據發射狀態(TX_FIFO_Empty = 1 表示數據發射已完成)。

如果用戶想要檢查寫入操作是否正確,可通過以下步驟來進行調試:

請檢查發射占用寄存器,確認是否已發射所有數據。

用戶還可以執行上述讀取操作以便通過讀取和驗證數據來交叉驗證寫入操作。

如果有來自從設備的 ACK,還請以相同方式檢查子寄存器,以對通信進行調試。

檢查 TX_FIFO_Empty 標記,確認是否所有數據都已完成發射。

如果步驟 6 中未發現任何問題,則表示您可將數據寫入從設備,請檢查是否已建立通信。

如何開始進行基本設計測試?

邏輯測試用例:

從 PS-IIC 訪問 EEPROM - 用戶可參閱代碼示例以測試如何通過 PS IIC 控制器訪問從設備。

針對從設備的低級 AXI IIC 寄存器訪問 - 用戶可使用隨附的代碼示例來測試 AXI IIC 控制器的基本功能。

從 AXI-IIC 訪問 EEPROM - 用戶可參閱代碼示例以測試如何通過 AXI IIC 控制器訪問從設備。

Linux 測試用例:

從PS-IIC 訪問 EEPROM

請參閱 Wiki 頁面

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842160/Cadence+I2C+Driver

以獲取 PS IIC 內核配置、設備樹節點和可用的用戶應用示例。

從 AXI-IIC 訪問 EEPROM

請參閱 Wiki 頁面

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841974/Linux+I2C+Driver

以獲取 AXI IIC 內核配置、設備樹節點和可用的 sysfs 示例。

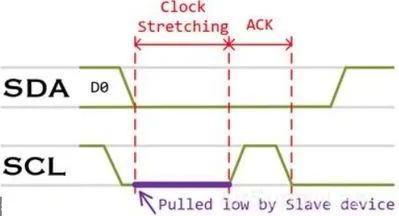

時鐘拉伸

IIC 設備可以通過拉伸 SCL 來延緩通信。在 SCL 低位狀態下,總線上的任何 IIC 主設備或從設備均可額外下拉 SCL 以防止其重新拉高,使其能夠降低 SCL 時鐘速率或者將 IIC 通信停止一段時間。

如何使用 AXI-IIC 來測試時鐘拉伸

測試用例的目的是生成時鐘拉伸機制。

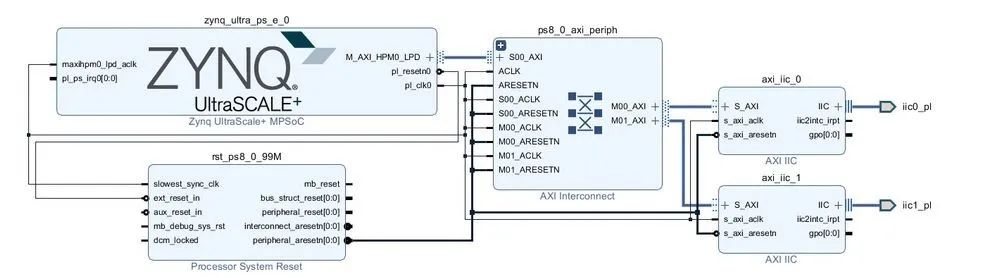

簡單硬件設計示例如下:

創建含 2 個 AXI-IIC IP 實例的 Vivado 硬件設計

在此測試用例中,2 個 IP 的輸出頻率相同。

每個 AXI IIC IP 的 SCL 和 SDA 都應在外部環回,即 SCL0 到 SCL1 且 SDA0 到 SDA1。

設計就緒后,您就可以導出到 SDK 并包含以下附件中的源代碼。

注:隨附的模塊框圖和源代碼示例已在 ZCU102 板上經過測試。用戶可以在自己的定制板上利用此測試用例,也可將其移植到 Vitis。

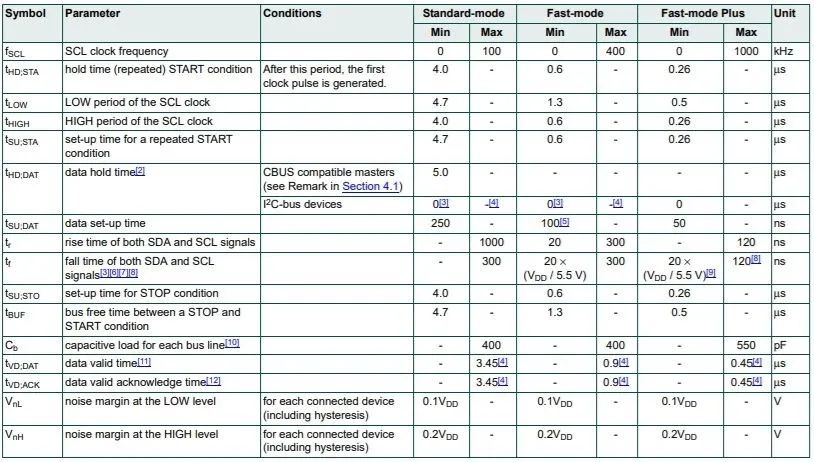

如何為賽靈思 IIC 控制器選擇從設備?

AXI IIC 和 PS IIC 控制器都符合 NXP IIC 總線規范。用戶必須確保其選擇使用的從設備的時序參數與UM10204 的第 48 頁上的“表 10”中的參數相同。

SDA 和 SCL 總線行的時序參數

注: PS IIC 不支持 Fast-mode Plus。

編輯:lyn

-

IIC

+關注

關注

11文章

300瀏覽量

38277 -

AXI

+關注

關注

1文章

127瀏覽量

16598

原文標題:開發者分享 | PS IIC 和 AXI IIC 調試技巧

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

是德示波器在音頻設備調試中的作用

解鎖SoC “調試”挑戰,開啟高效原型驗證之路

數字電源的低壓調試和高壓調試

mos管的vth和什么有關

渦流損耗的大小與什么有關

使用PSoc 62系列板卡時遇到了無法燒錄和調試的問題如何解決?

PLC系統的安裝與調試流程

探討有關AXIIIC和PSIIC的自調試技巧

探討有關AXIIIC和PSIIC的自調試技巧

評論