很多FPGA/IC開(kāi)發(fā)工具都提供設(shè)計(jì)例子,方便使用者學(xué)習(xí)和練習(xí),例如,Xilinx ISE提供了很多設(shè)計(jì)實(shí)例,放在ISE5.X的安裝目錄下的ISEexamples目錄下,例如CDMA匹配濾波器、Johnson計(jì)數(shù)器、PN碼發(fā)生器、頻率計(jì)等,這些例子是經(jīng)驗(yàn)豐富的工程師寫(xiě)的,我們可以學(xué)到編程思想、代碼風(fēng)格等方面的知識(shí)和經(jīng)驗(yàn),這些東西可能從學(xué)校老師或一般書(shū)籍都學(xué)習(xí)不到。

如果你用的不是Xilinx的FPGA,也就是說(shuō)不使用ISE,那也沒(méi)關(guān)系,HDL代碼和testbench的設(shè)計(jì)思想和方法是一樣的,你照樣可以從中學(xué)到很多東西。下面以其中一個(gè)例子――同步FIFO為例,分析一下我們的第一個(gè)testbench,設(shè)計(jì)的源代碼可以在ISEexamples目錄下找到,Xilinx還提供了Application Note詳細(xì)介紹了該FIFO的細(xì)節(jié),

1.511x8同步FIFO功能簡(jiǎn)介

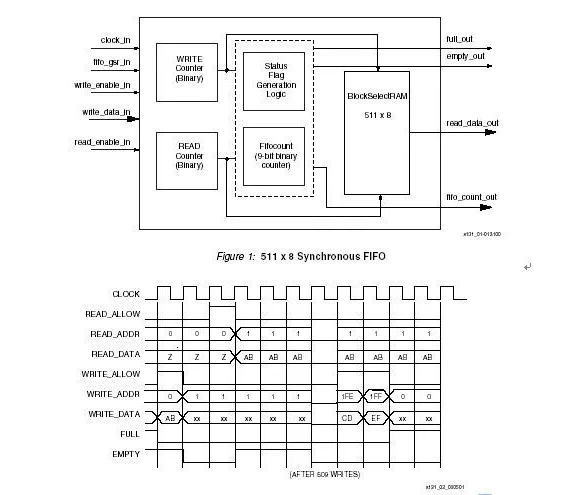

為了對(duì)這個(gè)511x8同步FIFO進(jìn)行功能驗(yàn)證,首先要清楚它的功能,只有這樣才能知道需要驗(yàn)證什么功能,以及如何進(jìn)行驗(yàn)證,圖1為該同步FIFO的原理框圖。

與異步FIFO相比,同步FIFO的讀、寫(xiě)時(shí)鐘是同一個(gè)時(shí)鐘,簡(jiǎn)化了FIFO的設(shè)計(jì),Empty和Full標(biāo)志的產(chǎn)生也比較容易,同步FIFO內(nèi)部使用二進(jìn)制計(jì)數(shù)器記錄讀地址和寫(xiě)地址。在異步FIFO中,由于讀寫(xiě)使用不同的時(shí)鐘,也就是說(shuō)設(shè)計(jì)存在兩個(gè)時(shí)鐘域,為了減少出現(xiàn)亞穩(wěn)態(tài)時(shí)產(chǎn)生的錯(cuò)誤,記錄讀寫(xiě)地址的計(jì)數(shù)器要使用格雷碼,Empty和Full標(biāo)志的產(chǎn)生也比較復(fù)雜。511x8同步FIFO(以下簡(jiǎn)稱FIFO)的工作時(shí)序如圖2所示。

讀FIFO數(shù)據(jù)時(shí),首先read_allow信號(hào)置高,時(shí)鐘上升沿到來(lái)時(shí)read_addr地址處的數(shù)據(jù)將出現(xiàn)在read_data處,同時(shí)read_addr加1。讓read_allow信號(hào)持續(xù)為高可以完成burst read操作。如果讀出的數(shù)據(jù)是FIFO的最后一個(gè)數(shù)據(jù),那么讀操作完成后Empty信號(hào)變高。Empty信號(hào)為高時(shí)讀出來(lái)的數(shù)據(jù)是無(wú)效的。

寫(xiě)FIFO數(shù)據(jù)時(shí),首先write_allow信號(hào)置高,同時(shí)準(zhǔn)備好輸入數(shù)據(jù)write_data,時(shí)鐘上升沿到來(lái)時(shí),數(shù)據(jù)將寫(xiě)入write_addr所指向的地址中,同時(shí)write_addr加1。讓write_allow信號(hào)持續(xù)為高可以完成burst write操作。如果某一個(gè)時(shí)鐘上升沿時(shí)寫(xiě)入第511個(gè)數(shù),那么下一個(gè)時(shí)鐘沿到來(lái)的時(shí)候Full信號(hào)變高,表示FIFO已經(jīng)寫(xiě)滿。

我們?cè)僭敿?xì)分析FIFO的工作時(shí)序圖。在圖2中,開(kāi)始時(shí)FIFO的讀寫(xiě)指針均為0,Empty為高表示FIFO處于空的狀態(tài),然后write_allow置高,時(shí)鐘上升沿到來(lái)時(shí)寫(xiě)入第一個(gè)數(shù)據(jù),Empty變低;一個(gè)CLK之后,read_allow置高,時(shí)鐘上升沿到來(lái)時(shí),讀出數(shù)據(jù),由于是最后一個(gè)數(shù)據(jù),所以Empty信號(hào)又變?yōu)橛行Вǜ唠娖剑T跁r(shí)序圖的右半部分,寫(xiě)入509個(gè)數(shù)據(jù)之后,再寫(xiě)入兩個(gè)數(shù)據(jù),F(xiàn)ull信號(hào)變?yōu)橛行В硎綟IFO為滿。

這個(gè)FIFO還有一個(gè)名為fifo_count_out的輸出,從4’b0000~4’b1111,分別表示FIFO滿的程度從不足1/16到15/16,為某些應(yīng)用提供方便。

2.驗(yàn)證

清楚FIFO的功能之后,我們就可以開(kāi)始驗(yàn)證工作了。驗(yàn)證工作的第一步是整理出FIFO需要驗(yàn)證的功能點(diǎn),這些功能點(diǎn)一般直接來(lái)源于FIFO應(yīng)該具有的功能,或者來(lái)源于它的使用方法。FIFO需要驗(yàn)證的功能點(diǎn)包括:

1)FIFO復(fù)位后,read_addr和write_addr為0,F(xiàn)ull為0,Empty為1。

2)讀FIFO數(shù)據(jù)時(shí),read_allow信號(hào)必須置高,時(shí)鐘上升沿到來(lái)時(shí)read_addr地址處的數(shù)據(jù)將出現(xiàn)在read_data處,同時(shí)read_addr加1。

3)讀出FIFO的最后一個(gè)數(shù)據(jù)后,Empty信號(hào)變高。

4)寫(xiě)FIFO數(shù)據(jù)時(shí),write_allow信號(hào)必須置高,時(shí)鐘上升沿到來(lái)時(shí),輸入數(shù)據(jù)write_data將寫(xiě)入write_addr所指向的地址中,同時(shí)write_addr加1。

5)如果某一個(gè)時(shí)鐘上升沿時(shí)寫(xiě)入第511個(gè)數(shù),那么下一個(gè)時(shí)鐘沿到來(lái)的時(shí)候Full信號(hào)變高,表示FIFO已經(jīng)寫(xiě)滿。

6)fifo_count_out端能正確的指示FIFO滿的程度。

分析Xilinx提供的testbench可以為我們編寫(xiě)自己的testbench提供很好的參考。FIFO的RTL代碼和testbench代碼放在ISEexamplesfifo_ver_131和fifo_vhd_131下。以verilog代碼為例,fifo_ver_131中包括了兩個(gè)testbench文件,一個(gè)是功能仿真testbench文件fifoctlr_cc_tb.tf,另一個(gè)是時(shí)序仿真(后仿真)testbench文件fifoctlr_cc_tb_timing.tf,這里我們主要分析功能仿真文件,為了方便大家理解,以下(下一帖)為注釋過(guò)的功能仿真testbench。大家看testbench的代碼時(shí),對(duì)照FIFO需要驗(yàn)證的功能點(diǎn),檢查是不是所有功能點(diǎn)都經(jīng)過(guò)了驗(yàn)證。

FIFO的testbench主要包括初始化、驗(yàn)證initial塊、讀寫(xiě)task等內(nèi)容,初始化部分主要完成復(fù)位信號(hào)、CLK信號(hào)等的初始化工作,讀寫(xiě)task把讀寫(xiě)、delay等操作模塊化,方便使用。這里主要介紹一下驗(yàn)證initial塊,也可以說(shuō)是驗(yàn)證的主程序,如下所示。

initial begin

delay; //保證驗(yàn)證環(huán)境正確復(fù)位

writeburst128; //寫(xiě)入512個(gè)數(shù),F(xiàn)ull信號(hào)應(yīng)該在寫(xiě)入511個(gè)數(shù)后變高

writeburst128;

writeburst128;

writeburst128;

read_enable = 1; //讀出一個(gè)數(shù),F(xiàn)ull信號(hào)應(yīng)該變低

writeburst128; //同時(shí)讀寫(xiě),檢查FIFO操作是否正確

read_enable = 0; //讀操作結(jié)束

endwriteburst; //寫(xiě)操作結(jié)束

delay;

readburst128; //連續(xù)讀512次,Empty信號(hào)應(yīng)在讀出511個(gè)數(shù)后變高

readburst128;

readburst128;

readburst128;

endreadburst;

end

這段程序首先延遲5個(gè)時(shí)鐘周期,等初始化完成之后再開(kāi)始驗(yàn)證工作。驗(yàn)證時(shí),首先寫(xiě)入512個(gè)數(shù),使用波形觀察器可以檢查寫(xiě)入的過(guò)程是否正確,以及Full信號(hào)在寫(xiě)入511個(gè)數(shù)后是否變高;然后read_enable = 1,讀出一個(gè)數(shù),F(xiàn)ull信號(hào)應(yīng)該變低,這樣寫(xiě)操作和Full信號(hào)的驗(yàn)證就基本完成了;程序接著也啟動(dòng)了寫(xiě)操作,由于此時(shí)read_enable仍然為高,即讀寫(xiě)同時(shí)進(jìn)行,這是對(duì)實(shí)際情況的模擬,可以對(duì)FIFO的功能進(jìn)行更嚴(yán)格的驗(yàn)證;最后,連續(xù)讀FIFO 512次,用波形觀察器檢查讀操作是否正確,Empty信號(hào)是否在讀出511個(gè)數(shù)后變高,如果這些操作都是正確的,那么FIFO的功能就基本正確了。

需要注意的一點(diǎn)是,以上的程序是不可綜合的,因?yàn)椴皇荝TL級(jí)描述,而是行為級(jí)描述(Behavioral Description)。行為級(jí)描述的特點(diǎn)是直接描述對(duì)象的功能,具有比較高的抽象層次,開(kāi)發(fā)、運(yùn)行速度都比RTL代碼要快,因此testbench都是用行為級(jí)描述寫(xiě)的。關(guān)于行為級(jí)描述的特點(diǎn)、寫(xiě)法以后將有專(zhuān)門(mén)的章節(jié)論述。

這個(gè)testbench的特點(diǎn)是,輸入激勵(lì)由testbench產(chǎn)生,輸出響應(yīng)的檢查人工完成,這樣的testbench編寫(xiě)相對(duì)容易,可以加快開(kāi)發(fā)速度,作為開(kāi)發(fā)人員自己驗(yàn)證是非常好的選擇。有些testbench能完成輸入激勵(lì)和輸出檢查,不用觀察波形也能完成驗(yàn)證工作,這樣的testbench具有更高的自動(dòng)化程度,使用方便,可重復(fù)性好,當(dāng)設(shè)計(jì)比較復(fù)雜而且團(tuán)隊(duì)中有專(zhuān)門(mén)的驗(yàn)證工程師時(shí),一般會(huì)有驗(yàn)證工程師建立一套這樣的testbench,用于驗(yàn)證開(kāi)發(fā)工程師的RTL級(jí)代碼,如果發(fā)現(xiàn)問(wèn)題,開(kāi)發(fā)工程師修改后在testbench再運(yùn)行一次所花的時(shí)間非常少,開(kāi)發(fā)復(fù)雜項(xiàng)目時(shí)這樣做可以比用波形觀察器節(jié)省很多時(shí)間。

3.總結(jié)

驗(yàn)證一般要通過(guò)寫(xiě)testbench實(shí)現(xiàn),testbench要完成向DUT施加激勵(lì)和檢查DUT相應(yīng)是否正確的功能,這就要求我們非常清楚待驗(yàn)證模塊(DUT)的功能,這樣才知道需要驗(yàn)證什么、如何施加激勵(lì)和如何檢查響應(yīng)是否正確。寫(xiě)testbench時(shí), 首先要列出需要驗(yàn)證的功能,讓后再編寫(xiě)testbench,這樣可以做到有的放矢,避免遺漏。

編輯:jq

-

IC

+關(guān)注

關(guān)注

36文章

5906瀏覽量

175245 -

fifo

+關(guān)注

關(guān)注

3文章

387瀏覽量

43555 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17128

原文標(biāo)題:FPGA開(kāi)發(fā)分析一個(gè)testbench

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

編寫(xiě)高效Testbench的指南和示例

FPGA基礎(chǔ)知識(shí)學(xué)習(xí)

FPGA入門(mén)必備:Testbench仿真文件編寫(xiě)實(shí)例詳解

fpga仿真器是什么?它有哪些優(yōu)勢(shì)?

fpga原型驗(yàn)證流程

fpga驗(yàn)證和測(cè)試的區(qū)別

fpga驗(yàn)證和uvm驗(yàn)證的區(qū)別

fpga開(kāi)發(fā)是什么意思

fpga仿真是什么

fpga開(kāi)發(fā)板是什么?fpga開(kāi)發(fā)板有哪些?

fpga用的是什么編程語(yǔ)言 fpga用什么語(yǔ)言開(kāi)發(fā)

高云FPGA簡(jiǎn)介

原型平臺(tái)是做什么的?proFPGA驗(yàn)證環(huán)境介紹

FPGA驗(yàn)證簡(jiǎn)介之FPGA開(kāi)發(fā)分析一個(gè)testbench

FPGA驗(yàn)證簡(jiǎn)介之FPGA開(kāi)發(fā)分析一個(gè)testbench

評(píng)論