一、主要概念

同步邏輯和異步邏輯:時鐘域為由單個時鐘或具有固定相位關系的時鐘驅動的設計部分。也就是說,在一個模塊中一個時鐘和他的翻轉或者分頻時鐘認為是相同的時鐘域,其所驅動的邏輯是同步邏輯。在一個模塊中不具有相同相位和時間關系的時鐘被視為不同的時鐘域,其所驅動的邏輯是異步邏輯。

亞穩態:如果數據傳輸中不滿足觸發器的建立時間和保持時間,或者復位過程中復位信號的釋放相對于有效時鐘沿的恢復時間(recovery time)不滿足,就可能產生亞穩態。亞穩態就是無法避免的,亞穩態主要發生在異步信號檢測、跨時鐘域信號傳輸以及復位電路等常用設計中。

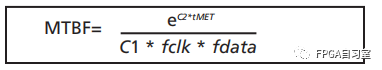

MTBF: 平均無故障工作時間,英文全稱:Mean time between failures;利用平均故障間隔時間(MTBF)公式可以預測亞穩態的發生,MTBF越大則說明亞穩態對電路產生的影響越小,反之亦然。

其中C1和C2是常數,依賴于構建觸發器所使用的技術;tMET為在不引起同步失敗的前提下亞穩態輸出持續時間,時間越長MTBF指數級增大,所以高頻電路兩級觸發器不夠可能要用三級觸發器來保證;fclk和fdata分別是同步時鐘和數據翻轉率;所以在不影響功能前提下,可以降頻工作頻率和數據的翻轉頻率,都可以有效的增大MTBF。

二、CDC典型錯誤場景

在芯片設計過程中,CDC正向確認時經常會發現幾種典型的錯誤場景:沒有處理直接裸跨、輸入同步器前組合邏輯輸出以及多路扇出和重新聚合場景等,還有一些不太常見情況未列出,請參閱文末資料。

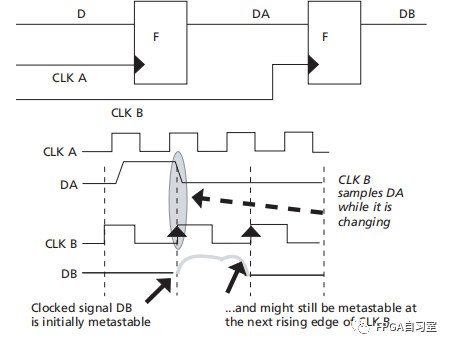

2.1直接裸跨

如上圖,如果CLK B采樣DA,而DA是變化的(在CLK的上升邊緣和下降D)的邊緣,則DB將是亞穩態的,這種就是沒有使用同步器,顯然是不合理的。

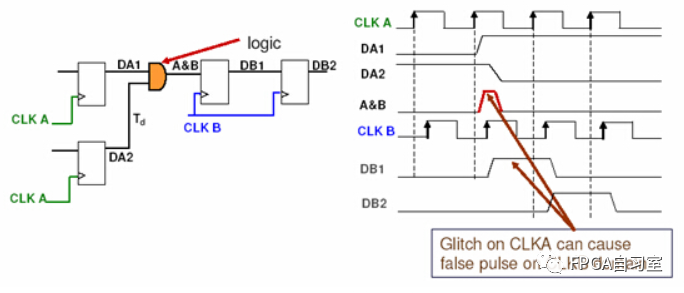

2.2毛刺(Glitch)

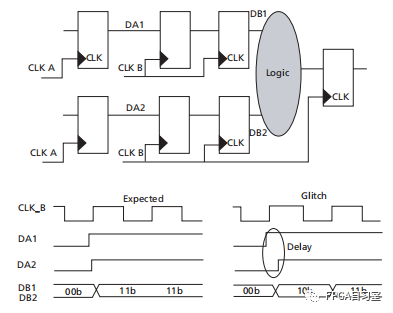

異步路徑時序工具不會進行時序分析,這條道路上的任何邏輯都必須謹慎精心設計并驗證,因為邏輯可能導致故障并在下游產生功能錯誤。如下圖所示,盡管兩個源觸發器同時給出脈沖,但由于布局布線以及環境原因而引起的傳播延遲(Td)不同,導致DA1和DA2信號不能同時到達,因此在CLKA時鐘域下A&B會產生毛刺,而在CLKB時鐘域下產生一個假脈沖,導致后繼電路異常。正確的做法是將A&B在CLKA時鐘域下打一拍寄存器輸出。

此外,還有另外一種情況出現漏采,如下圖所示,DB1在CLKB時鐘域下應有的高電平信號,由于DA1和DA2的傳輸延時不同,導致在CLKB下沒有傳遞出去。

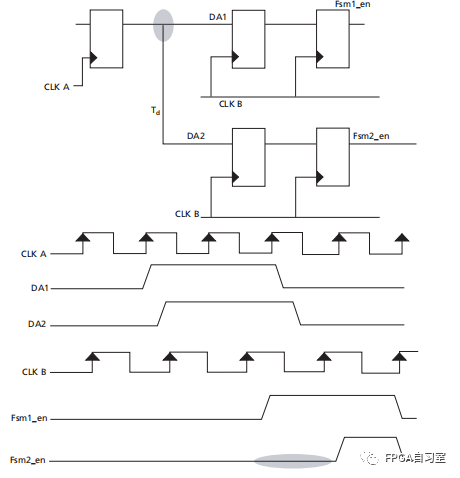

2.3多路扇出

單個信號扇出輸入到多個同步器時,由于輸入信號到達的同步器的時間不同(傳輸延時Td不同),同步可能需要一拍或者兩拍完成同步,此時同步后的各個信號之間可能存在錯拍問題。如下圖所示,DA1和DA2信號同步后分別是Fsm1_en 和 Fsm2_en信號,設計時如果仍認為它們是相同的信號,就會導致邏輯功能錯誤。

2.4重新聚合(RECONVERGENCE)

在多bit跨時鐘傳輸過程中,如果各個bit之間分別使用單bit同步器進行跨時鐘處理,在目的時鐘域又重新聚合起來。如下圖所示,DA1和DA2由于傳輸delay不同,在 CLKB上升沿采樣時,就會有2’10不期望值的出現,這樣DB1和DB2進行邏輯處理(聚合)時,也會得到不期望的值,這也是總線不能采用單bit同步器進行跨時鐘處理的原因。此外,格雷碼是可以使用單bit同步器進行處理的,AFIFO就是其典型設計。

擴展:上述指的兩個兩級觸發器的單bit同步器,可以擴展為兩個AFIFO總線跨時鐘,如果設計不當,只使用其中一個AFIFO的empty作為兩個AFIFO讀判斷,由于格雷碼同步的不確定性,導致兩個AFIFO的empty信號不一致,當出口兩組總線聚合時,就會發生錯拍問題,從而導致功能異常。解決辦法是兩個AFIFO的讀條件應該關聯或者使用一個大的AFIFO.

Referencecadencecdc(1)

Reference Spyglass cdc(2)

編輯:jq

-

CDC

+關注

關注

0文章

57瀏覽量

17770 -

復位電路

+關注

關注

13文章

322瀏覽量

44536

原文標題:CDC(四) CDC典型錯誤案例

文章出處:【微信號:FPGA_Study,微信公眾號:FPGA自習室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

cdc減振器控制原理是什么

關鍵指南針-NXP USB CDC_VCOM虛擬串口例程

USB復合設備MSC+CDC,MSC異常影響CDC收發怎么解決?

請問如何安裝Espressif CDC Device驅動?

esp32-s2-usb-host-cdc示例程序接收錯誤怎么處理?

ESP32-S2-WROOM使用USB CDC虛擬串口打印log,模組在跑一段時間后會報一下錯誤,為什么?

ESP32S2使用單根USB線創建MSC+CDC與上位機通信,CDC異常的原因?

STM32 USB CDC為什么只能發送4096個字節?

STM32做3個CDC復合設備遇到的地址問題怎么解決?

USB CDC無法使用中斷傳輸的原因?

USB復合設備MSC+CDC,CDC_Transmit_FS函數發送不正常的原因?

求助,關于USB復合設備HID+CDC串口問題求解

PCB設計工作中常見的錯誤有哪些?

簡述CDC當中最典型錯誤案例

簡述CDC當中最典型錯誤案例

評論