作者:董文岳,林國(guó)偉,梁文海

1、引言

近年來(lái)人工智能(AI)已成為國(guó)際上技術(shù)創(chuàng)新研究的一個(gè)熱點(diǎn),各種工業(yè)機(jī)器人、服務(wù)機(jī)器人等機(jī)器人產(chǎn)品的應(yīng)用日益廣泛,而作為機(jī)器人的“腳”,機(jī)器人移動(dòng)平臺(tái)也要具備豐富的功能和高度的智能化,不但需要實(shí)現(xiàn)高靈活性的移動(dòng)能力和良好的越障能力,而且要求臺(tái)配置有多種傳感器,配合機(jī)器人的“大腦”可以實(shí)現(xiàn)自動(dòng)避障越障、自主進(jìn)行路徑規(guī)劃、地圖構(gòu)建等功能。

多功能智能移動(dòng)平臺(tái)電控系統(tǒng)作為機(jī)器人移動(dòng)平臺(tái)的“神經(jīng)中樞”,是實(shí)現(xiàn)機(jī)器人移動(dòng)平臺(tái)智能化設(shè)計(jì)的關(guān)鍵設(shè)計(jì)。本文分析多功能智能移動(dòng)平臺(tái)的功能性能需求,基于高可靠嵌入式處理器S698-T芯片,提出一個(gè)多功能智能移動(dòng)平臺(tái)電控系統(tǒng)的設(shè)計(jì)方案,為各種機(jī)器人移動(dòng)平臺(tái)的設(shè)計(jì)提供一個(gè)良好的解決方案。

2、系統(tǒng)需求

根據(jù)機(jī)器人移動(dòng)平臺(tái)功能、性能要求,電控系統(tǒng)擬采用PC+嵌入式系統(tǒng)架構(gòu),由上位機(jī)系統(tǒng)和下位機(jī)系統(tǒng)兩個(gè)部分組成,上位機(jī)采用PC+傳感器實(shí)現(xiàn),下位機(jī)基于高可靠嵌入式SPARC架構(gòu)處理器S698-T設(shè)計(jì),上位機(jī)與下位機(jī)之間采用RS422總線進(jìn)行數(shù)據(jù)/命令交互,預(yù)留CAN2.0總線通訊接口。

2.1 上位機(jī)性能需求

上位機(jī)作為多功能智能移動(dòng)平臺(tái)的“大腦”,主要實(shí)現(xiàn)多功能智能移動(dòng)平臺(tái)的視覺(jué)功能、地圖構(gòu)建以及導(dǎo)航等功能。

上位機(jī)要求采用Intel -X86 i5以上CPU的工業(yè)級(jí)嵌入式主板實(shí)現(xiàn),并基于嵌入式主板的USB、PCIe、以太網(wǎng)、RS422以及SIM卡接口等外圍接口,集成二維/三維激光(室內(nèi)/外)傳感器、相機(jī)(預(yù)留)、CAN總線通訊模塊等外圍模塊

2.2 下位機(jī)性能需求

下位機(jī)作為多功能智能移動(dòng)平臺(tái)的指令執(zhí)行控制以及部分傳感器的輸入采集處理平臺(tái),主要實(shí)現(xiàn)電機(jī)驅(qū)動(dòng)控制功能以及紅外測(cè)距、超聲波測(cè)距等傳感器輸入參數(shù)采集處理功能,并通過(guò)RS422總線(備用CAN總線)與上位機(jī)建立通訊,具體需求如下:

1、主處理器:S698-T,主頻100MHZ;

2、協(xié)處理器:FPGA;

3、板載內(nèi)存:SRAM:1Mbit,F(xiàn)LASH:1Mbit;

4、提供7路紅外測(cè)距傳感器信號(hào)采集接口,接口為12bit的A/D采集輸入,輸入為最大3.3V模擬信號(hào);

5、提供6路超聲波測(cè)距傳感器的輸入接口,要求為信號(hào)電平為T(mén)TL3.3V的RS232接口,波特率可配置(4800bps ~ 115200bps);

6、提供1路GPS模塊的輸入接口,要求為信號(hào)電平為T(mén)TL3.3V的RS232接口,波特率可配置(4800bps ~ 115200bps);

7、提供3路慣導(dǎo)單元IMU的輸入接口,接口要求為I2C接口,預(yù)留SPI接口;

8、提供6路PWM信號(hào)輸出、18路IO信號(hào)輸出(6路方向控制、6路使能控制、6路電機(jī)剎車信號(hào))用于控制電機(jī)驅(qū)動(dòng),要求信號(hào)光耦隔離5V輸出;

9、提供6路IO信號(hào)采集,用于霍爾反饋PWM捕獲,輸入信號(hào)為脈沖信號(hào),最大頻率為5KHz;

10、提供2路CAN2.0總線接口以及2路RS422總線接口,用于與上位機(jī)通訊;

11、提供對(duì)上位機(jī)進(jìn)行電源上下電控制功能;

12、提供1路A/D用于電源電壓采集,1路A/D用于溫度采集;

13、具備溫度采集功能,提供1路預(yù)留RS232接口;

14、工作溫度:-40℃~+60℃;

3 、系統(tǒng)組成

圖1 系統(tǒng)框圖

如圖1所示,電控系統(tǒng)主要由上位機(jī)和下位機(jī)模塊兩部分組成,其中上位機(jī)包含以下組成部分:

1、嵌入式主板:1個(gè);

2、CAN總線模塊:1個(gè);

3、二維/三維激光(室內(nèi)/外)傳感器:1個(gè);

4、相機(jī)(預(yù)留):1個(gè);

下位機(jī)包含以下組成部分:

1、基于S698-T+FPGA控制器模塊:1個(gè);

2、紅外測(cè)距傳感器:7個(gè);

3、超聲波測(cè)距傳感器:6個(gè);

4、GPS模塊:1個(gè);

5、慣導(dǎo)單元IMU:3個(gè);

6、電機(jī)及驅(qū)動(dòng)模塊:6組;

4、系統(tǒng)設(shè)計(jì)

本電控系統(tǒng)的上位機(jī)主要涉及到硬件選型以及軟件開(kāi)發(fā),本文暫不對(duì)其設(shè)計(jì)展開(kāi)詳述,主要對(duì)下位機(jī)的設(shè)計(jì)方案進(jìn)行詳述。

下位機(jī)主要由主控制器模塊以及電機(jī)驅(qū)動(dòng)、超聲波傳感器、紅外傳感器、慣導(dǎo)模塊等周邊相關(guān)外設(shè)組成,其中主控制器模塊基于S698-T設(shè)計(jì),具體方案如下:

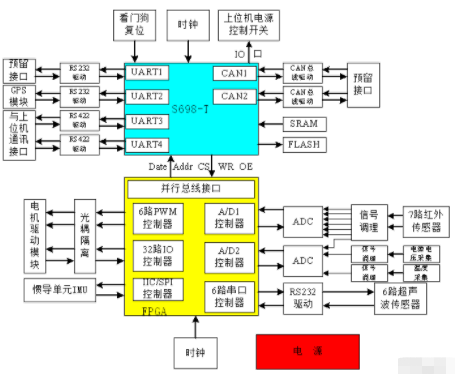

圖2 基于S698-T+FPGA的控制器模塊系統(tǒng)框圖

如圖2所示,下位機(jī)主控制器模塊采用S698-T+FPGA的架構(gòu),S698-T作為主處理器,其外圍設(shè)計(jì)SRAM、FLASH、硬件看門(mén)狗復(fù)位、時(shí)鐘等模塊,構(gòu)成一個(gè)S698-T的最小系統(tǒng),再根據(jù)外圍接口需要,使用S698-T片內(nèi)的4路RS232總線接口以及2路CAN總線接口,實(shí)現(xiàn)2路RS232接口、2路RS422接口以及2路CAN總線接口。

控制器模塊采用FPGA作為協(xié)處理器,并通過(guò)并行總線將FPGA掛接在S698-T的IO空間上,實(shí)現(xiàn)與S698-T的協(xié)同處理。FPGA根據(jù)系統(tǒng)功能需要,片內(nèi)設(shè)計(jì)了兩個(gè)ADC控制器、6路串行總線控制器、6路PWM輸出控制器、32路IO控制器、IIC/SPI接口控制器以及并行接口控制器等功能模塊,同時(shí)外接相關(guān)驅(qū)動(dòng)電路實(shí)現(xiàn)系統(tǒng)的接口需求。

控制器模塊采用12V DC供電,板上設(shè)計(jì)有DC-DC電源模塊,實(shí)現(xiàn)12VDC到+1.2VDC、+2.5VDC、+3.3VDC、+5VDC的轉(zhuǎn)換,供板上相關(guān)器件使用。

4.1 主處理器設(shè)計(jì)

控制器模塊的主處理器設(shè)計(jì)主要是S698-T最小系統(tǒng)+外圍接口驅(qū)動(dòng)電路的設(shè)計(jì),S698-T最小系統(tǒng)主要包括S698-T、SRAM、FLASH、硬件看門(mén)狗復(fù)位電路、時(shí)鐘電路以及調(diào)試用的DSU接口電路。

高可靠處理器S698-T簡(jiǎn)介:

1、采用哈弗體系結(jié)構(gòu)(Harvard architecture);

2、具備整型單元(IU:Integer Unit):

? 32位RISC,采用SPARC V8(IEEE-1754)指令集;

? 5級(jí)指令流水(預(yù)取、譯碼、執(zhí)行、存儲(chǔ)、回寫(xiě));

? 具有硬件乘法器和硬件除法器;

? 支持MAC和UMAC等DSP指令;

3、浮點(diǎn)處理單元(FPU:Floating Point Unit)

? 遵循IEEE-754標(biāo)準(zhǔn);

? 支持單/雙精度;

4、具有彼此分離的大容量指令Cache 32K Bytes和數(shù)據(jù)Cache 16K Bytes;

5、片內(nèi)總線遵循AMBA2.0標(biāo)準(zhǔn),采用AHB總線聯(lián)接片內(nèi)高速設(shè)備,采用APB總線聯(lián)接片內(nèi)低速設(shè)備;

6、在線硬件調(diào)試支持單元(DSU:Debug Support Unit):

? 無(wú)需外置仿真器的支持即可實(shí)現(xiàn)硬件在線直接調(diào)試;

? 可實(shí)現(xiàn)對(duì)內(nèi)部資源(如寄存器、用戶可用RAM等)的操作;

? 可實(shí)現(xiàn)程序斷點(diǎn)設(shè)置;

7、集成存儲(chǔ)器控制器(MCTRL:Memory Controller):

? 支持外部SRAM、SDRAM、ROM 以及MAP I/O等類型的存儲(chǔ)器;

? SRAM、ROM及MAP I/O的數(shù)據(jù)總線寬度可通過(guò)軟件配置成32/16/8 位三種模式;

? SRAM、ROM及MAP I/O的存取時(shí)間參數(shù)可配置;

? 支持5個(gè)SRAM Bank、2個(gè)SDRAM Bank、2個(gè)ROM Bank、1個(gè)IO Bank;

? 尋址空間2048M Bytes;

? ROM尋址空間:512M Bytes;

? MAP I/O尋址空間:512M Bytes;

? SRAM/SDRAM尋址空間:1024M Bytes;

8、集成1553B 、ARINC429、CAN、串口等數(shù)據(jù)總線控制器;

9、集成多功能IO接口(MFIO):

? 集成16路獨(dú)立的多功能IO接口;

? 各路的輸入或輸入方向可以獨(dú)立配置;

? 各路均可以輸出周期、占空比、電平極性、脈沖數(shù)目等參數(shù)可調(diào)的PWM信號(hào);

? 各路均具有輸入脈沖計(jì)數(shù)功能;

10、集成定時(shí)器、看門(mén)狗、ADC、DAC等模塊;

11、生產(chǎn)工藝:130nm CMOS;

12、工作頻率:

? 最高主頻(IUCLK):200MHz;

? 最高外頻(SYSCLK):100MHz;

13、處理能力:

? 180MIPS@200MHz;

? 55MFLOPS(Double Precision)@200MHz;

14、峰值功耗:不高于1.5W@200MHz;

15、電源電壓

? 3.3V±0.3V(IO);

? 1.2V±0.1V(CORE);

16、工作環(huán)境溫度

? 工業(yè)級(jí)-40℃~+85℃(塑封PBGA352);

? 軍品級(jí)-55℃~+125℃(陶封CBGA352);

控制器模塊的主處理器的主要元器件選型如下:

1) 主控制器:S698-T,工作主頻為100MHz;

2) SRAM:IS61LV51216-10TI,容量為512k*16bit;

3) FLASH:39VF040-90-4I-NH,容量為512k*8bit;

4) 看門(mén)狗:TPS3813K33MDBVREP;

5) 時(shí)鐘:有源晶振,10MHz;

6) DSU接口/RS232總線接口驅(qū)動(dòng)芯片:MAX3232ESE;

7) CAN總線驅(qū)動(dòng)芯片:TJA1042t;

8) RS422總線驅(qū)動(dòng)芯片:MAX488ESA;

9) 上位機(jī)電源控制開(kāi)關(guān):選用歐姆龍繼電器G6k-2F;

4.2 協(xié)處理器設(shè)計(jì)

控制器模塊的主處理器設(shè)計(jì)主要是FPGA最小系統(tǒng)+外圍接口驅(qū)動(dòng)電路的設(shè)計(jì),F(xiàn)PGA設(shè)計(jì)包括硬件設(shè)計(jì)以及FPGA邏輯設(shè)計(jì),對(duì)于FPGA邏輯設(shè)計(jì)本文只提出設(shè)計(jì)需求,具體如下:

1) 具備2個(gè)ADC控制器功能,ADC采用ADS8555;

2) 具備6路串口控制器功能,波特率可設(shè)置,收發(fā)緩存不小于32Byte;

3) 具備6路PWM輸出控制器功能;

4) 具備32路IO輸入輸出功能,輸入可識(shí)別脈沖頻率不小于5KHz;

5) 具備8路IIC和SPI接口控制器功能;

6) 具備與S698-T進(jìn)行交互的并行接口功能;

7) 時(shí)鐘資源:時(shí)鐘可采用S698-T的時(shí)鐘輸出作為FPGA時(shí)鐘輸入,同時(shí)FPGA外接33MHz晶振;

控制器模塊的協(xié)處理器的主要元器件選型如下:

1) FPGA:選用Altera FPGA;

2) 時(shí)鐘:有源晶振,33MHz;

3) ADC:選用ADS8555;

4) 光耦隔離:HCPL-2630;

5) RS232總線接口驅(qū)動(dòng)芯片:MAX3232ESE;

4.3電源供電設(shè)計(jì)

控制器模塊采用+12VDC供電,模塊內(nèi)部需要用到的電源包括+5VDC、+3.3VDC、+2.5VDC、+1.2VDC,因此需要選用DC-DC模塊芯片進(jìn)行設(shè)計(jì),具體選型如下:

1) 12V轉(zhuǎn)5V:LM2596T_5.0;

2) 5V轉(zhuǎn)3.3V:LT1963AMP-3.3V;

3) 5V轉(zhuǎn)2.5V:LT1963AMP-2.5V;

4) 5V轉(zhuǎn)1.2V:NCP565D2T12;

4.4 軟件設(shè)計(jì)

基于高可靠處理S698-T進(jìn)行多功能智能移動(dòng)平臺(tái)電控系統(tǒng)的設(shè)計(jì),涉及到S698-T的控制軟件設(shè)計(jì),在此我們引入了嵌入式實(shí)時(shí)多任務(wù)操作系統(tǒng)(EOS)--RTEMS,利用珠海歐比特控制工程股份有限公司開(kāi)發(fā)的基于此操作系統(tǒng)的Orbita EOS嵌入式操作系統(tǒng)及其Orbita EOS 開(kāi)發(fā)工具,可大大提高軟件編程效率和可靠性,具體可參考(Orion4.0用戶手冊(cè))。

5、結(jié)束語(yǔ)

在當(dāng)今人工智能的熱潮下,多功能智能移動(dòng)平臺(tái)的應(yīng)用也日益廣泛,各種應(yīng)用場(chǎng)景對(duì)其電控系統(tǒng)提出了多種多樣的要求,本文針對(duì)市面廣泛的需求,提出一種基于S698-T的多功能智能移動(dòng)平臺(tái)電控系統(tǒng)的設(shè)計(jì)方案,可兼容市面的各種需求,為后續(xù)多功能智能移動(dòng)平臺(tái)的設(shè)計(jì)提供一種有效的參考。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19178瀏覽量

229200 -

嵌入式

+關(guān)注

關(guān)注

5071文章

19026瀏覽量

303502 -

機(jī)器人

+關(guān)注

關(guān)注

210文章

28231瀏覽量

206614

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

辰漢-如何實(shí)現(xiàn)服務(wù)機(jī)器人的運(yùn)算與控制

【下載】《嵌入式系統(tǒng)設(shè)計(jì)與實(shí)例開(kāi)發(fā):基于ARM微處理器與μC/OS-2實(shí)時(shí)操作系統(tǒng)》

【下載】《 嵌入式系統(tǒng)設(shè)計(jì)與實(shí)例開(kāi)發(fā):基于ARM微處理器與μC/OS-2實(shí)時(shí)操作系統(tǒng)》

嵌入式系統(tǒng)在機(jī)器人中的應(yīng)用

如何利用ARM研究嵌入式服務(wù)機(jī)器人控制器?

嵌入式在機(jī)器人視覺(jué)系統(tǒng)的應(yīng)用

RIO嵌入式控制平臺(tái)怎么助力機(jī)器人應(yīng)用?

嵌入式技術(shù)在機(jī)電控制系統(tǒng)有什么應(yīng)用?

如何實(shí)現(xiàn)移動(dòng)機(jī)器人的設(shè)計(jì)?

小白求助,求基于嵌入式處理器S3C2440為核心的多任務(wù)機(jī)器人控制系統(tǒng)

通過(guò)多軸工業(yè)機(jī)器人來(lái)聊聊機(jī)器人控制系統(tǒng)以及控制器的實(shí)現(xiàn)

S698-T芯片開(kāi)發(fā)系統(tǒng)S698T-Dkit使用說(shuō)明書(shū)

OBT-BSP-VxWorks6.7 S698-T平臺(tái)應(yīng)用開(kāi)發(fā)手冊(cè)v2

S698-T芯片開(kāi)發(fā)系統(tǒng)S698T-Dkit使用說(shuō)明書(shū)下載

基于嵌入式移動(dòng)機(jī)器人無(wú)線通訊系統(tǒng)的實(shí)現(xiàn)

基于嵌入式處理器S698-T芯片實(shí)現(xiàn)機(jī)器人移動(dòng)平臺(tái)電控系統(tǒng)的設(shè)計(jì)

基于嵌入式處理器S698-T芯片實(shí)現(xiàn)機(jī)器人移動(dòng)平臺(tái)電控系統(tǒng)的設(shè)計(jì)

評(píng)論