典型的相控陣CWD(連續波多普勒)架構中,超聲傳感器的聚焦孔徑分成兩部分,一半的(64至128個)傳感器單元用于發送器,另一半用于接收器。作用在發射單元的信號是方波信號,典型頻率為2.0MHz至7.5MHz多普勒頻率。發射單元通過發送適當相位的信號聚焦發射波束。同樣,CWD接收信號通過對每個接收單元的信號進行相位調整、求和進行聚焦。

“波束成型”CWD接收信號是由固態組織反射的強信號(通常稱其為雜波)以及流動的血液反射回來的較弱的多普勒信號。每個相控陣接收通道輸入端的典型雜波可能高達100mVp-p,而接收機RTI的噪底只有1至2nV/。為了優化接收性能,需要每通道的SNR達到155dBc/。

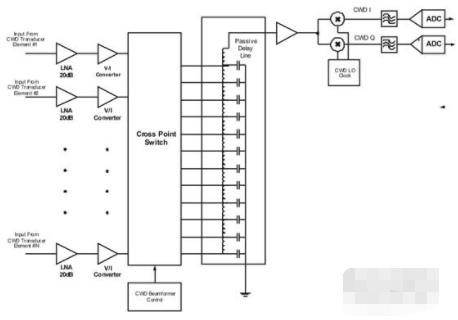

對于一個64通道的CWD接收機,考慮到求和增益,求和后的“波束成型”信號需要額外的18dB動態范圍,整體信噪比SNR的要求會達到173dBc/!更加困難的是,感興趣的低速多普勒信號的頻率會在1kHz以內或低于雜波信號。由此可見超聲檢測設備面臨巨大的設計挑戰。目前,超聲系統大多采用模擬延時線接收器實現CWD信號檢測(圖1),來自超聲接收單元的輸入信號經過緩沖、放大,低噪聲放大器提供大約20dB的增益。LNA輸出被轉換成電流信號,隨后通過交叉開關和模擬延時線進行波束成型。這種架構很容易集成,因為他所需要的電壓-電流轉換器、模擬開關、無源延時線以及單路I/Q混頻器很容易集成。通過配置交叉開關求和,通過適當的延時線抽頭切換信號,達到每個接收器的延時要求。

波束成型后的RFCWD信號混頻后得到基帶I、Q信號,這兩路信號經過帶通濾波后進行數字轉換。RF至基帶的混頻處理通常是接收鏈路保證SNR的瓶頸,這個處理過程對CWD的性能影響較大,對于64通道設計示例,I、Q RF混頻器需要在處理波束成型信號時具有173dBc/(1kHz頻偏)的動態范圍。能夠達到這一指標的混頻器很難實現,此外,本振驅動信號還必須保持極低的抖動。遺憾的是很難從市場上獲得能夠達到這樣指標的邏輯器件—雖然CWD延時線能夠滿足結構緊湊的超聲系統的最低要求,因此,上述性能的局限性是亟待解決的問題。

圖1 基于CWD延時線的接收機簡化電路

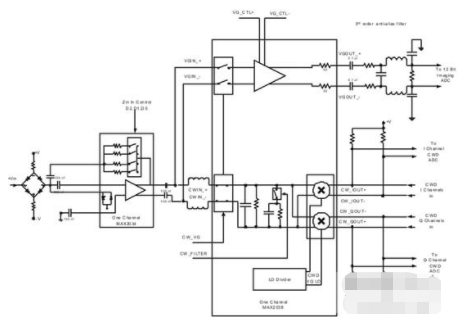

為了獲得更高性能,在CWD系統中引入一個CWD混頻器/波束成型器,簡化框圖如圖2所示。該架構中,每個通道都具有一個I/Q混頻器,在基帶端(而非RF端)進行波束成型求和;每路I/Q混頻器的LO相位可以調節在N (N =8至16相)個相位中的一種。LO相位的變化將改變接收信號的相位,達到波束成型的目的。

由于混頻器的實現基于每個通道,對每個通道混頻器的要求可以降低到155dBc/Hz (1kHz頻偏)。這一指標雖然苛刻,但利用雙極型混頻器和標準邏輯器件可以實現。混頻器輸出為電流,而且在基帶進行無源求和,可以滿足CWD波束成型的SNR要求。

圖2 低功耗LNA和CWD混頻器/波束成型電路能夠簡化CWD接收機設計,獲得高性能

過去,由于缺乏適當的集成工藝,很難實現高性能的波束成型架構。但目前這一問題已經得到解決,完全集成的8通道VGA和8通道CWD I/Q混頻器以及配套的可編程LO驅動器已經開始供貨,圖3所示給出了這類器件MAX2038接收鏈路的示圖。采用這種架構可以使超聲系統達到優異的CWD性能,不存在上述延時線CWD架構的局限性。

圖3 簡化后的單通道超聲接收機,采用MAX2038單芯片8路I/Q混頻器和MAX2034 4路LNA,有效提高系統性能

構建CWD接收器的另外一個潛在問題是LNA放大器的SNR指標,為了降低功耗、減小尺寸,許多超聲設計人員選擇了CMOSLNA,這樣的器件可能適合某些能夠控制CWD性能的應用。利用幾何尺寸低于0.35μm的CMOS工藝制作放大器時,1/f噪聲很大。這種噪聲會引起LNA增益的低頻調制。較強的RFCWD雜波通過這種LNA時將產生較大的低頻調制噪聲,從而降低SNR指標和CWD檢測靈敏度。因此,為了滿足高性能的應用需求,應選擇類似于MAX2034 4通道超聲LNA的雙極型低噪聲放大器。

責任編輯:gt

-

傳感器

+關注

關注

2548文章

50698瀏覽量

752053 -

混頻器

+關注

關注

10文章

678瀏覽量

45618 -

發送器

+關注

關注

1文章

258瀏覽量

26798

發布評論請先 登錄

相關推薦

混頻器的分類和介紹

混頻器怎么選

結構緊湊的超聲成像系統連續波多普勒(CWD)設計的挑戰

RF和微波設計中混頻器件應用

利用雙極型混頻器和標準邏輯器件滿足CWD波束成型的SNR要求

利用雙極型混頻器和標準邏輯器件滿足CWD波束成型的SNR要求

評論