問題:有沒有一個模塊,能讓我直接將微小的傳感器輸出訊號轉換為ADC輸入電壓?

答案:有的,新一代儀表放大器系列(如ADI的整合方案)可望一舉完成如下任務:抑制共模訊號、放大差模訊號,將電壓轉換為符合要求的ADC輸入電壓,并且保護ADC免受過壓影響!

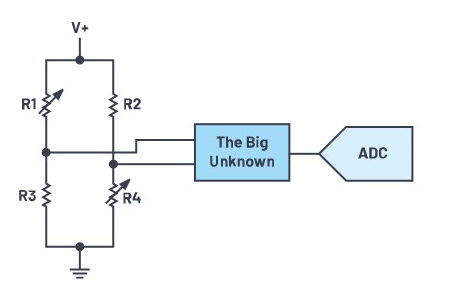

在無數的工業、汽車、儀器儀表和眾多其他應用中,普遍存在著一項挑戰,就是如何將微小的傳感器訊號正確連接到ADC,以實現數字化和數據擷取。傳感器訊號通常很微弱,可能有很高的噪聲,看上去像是一個非常高的阻抗源,位于大共模(CM)電壓之上。這些都是ADC輸入所不樂見的。

本文將介紹最新整合解決方案,可以徹底解決工程師所提出超出當下能力范圍的問題。文中并將詳細介紹設計步驟,以便配置一個完整的傳感器接口儀表放大器來驅動ADC輸入。

圖1:從傳感器到達ADC的挑戰

什么適合傳感器?為何有問題?

這個問題的簡短答案是儀表放大器。傳感器適合連接的對象是儀表放大器。

儀表放大器具有高精度(低失調)和低噪聲特性,不會破壞小輸入訊號。其差分輸入適合于許多傳感器訊號(如應變計、壓力傳感器等),并且能夠抑制任何存在的共模訊號,僅留下我們感興趣的原始小電壓,而不至于會有不需要的共模訊號。儀表放大器具有很大的輸入阻抗,不會為傳感器帶來負載,確保脆弱的訊號不受訊號處理的影響。

此外,儀表放大器通常使用單一外部電阻即可提供很大的增益和可選增益范圍,因而非常靈活,讓目標小訊號適應遠高于訊號路徑噪聲位準的電壓和ADC模擬輸入。儀表放大器是針對精密性能而設計的,內部進行了調整,能夠在寬廣的工作溫度范圍內保持其性能,并且不受電源電壓變化的影響。儀表放大器還具有極低的增益誤差,這也有助于其維持精度,并限制擺幅變化所造成的測量或訊號誤差

ADC輸入樂見什么?

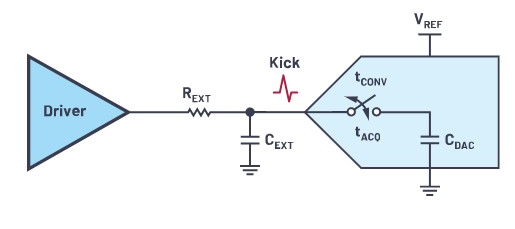

驅動ADC輸入可不是那么容易。前端的內部電容(圖2中的CDAC)開關操作會引起電荷注入,這使得傳輸高線性度的穩定訊號以供ADC量化成為一項艱巨的任務。驅動ADC輸入的驅動器必須能夠處理這些龐大的電荷注入,并在下一個轉換周期之前迅速穩定下來。此外,根據ADC分辨率(位數),驅動器的噪聲和失真不應成為限制因素。

圖2:ADC輸入驅動具有挑戰性

要達到上述要求絕非易事,特別是對于低功耗驅動器而言。另外,由于半導體制程的現代化,ADC工作電源電壓日漸下降。這種趨勢的不良副作用之一,是ADC輸入變得更容易受輸入過壓的影響,并可能造成傷害或損壞,而這就需要有外部電路來防范這種過壓。此類外部電路不僅不能將任何可測量噪聲加入訊號,而且不應限制帶寬或引起任何形式的失真。另外還非常希望整個電路能快速反應,并能從過壓事件中迅速地恢復。

偏移輸入訊號以符合ADC模擬輸入電壓范圍也存在挑戰。為執行此任務而增加的任何電路組件都必須遵守前面列出的所有限制條件(即低失真、低噪聲、足夠的帶寬等)。

如果儀表放大器能夠直接驅動ADC就好了…

市面上的所有儀表放大器都存在一些缺點,因此需要更多電路組件才能完成從物理世界(傳感器)到數字世界(ADC)的路徑。傳統上,儀表放大器不是驅動ADC的首選電路組件(某些ADC比其他ADC更精密)。儀表放大器所做的事情已經夠多了,希望它做得更多似乎不公平!

克服ADC驅動器的諧波失真(HD)是一項困難的挑戰。下面是ADC驅動器必須滿足或超過的失真性能的表達式,其是ADC分辨率的函數:

因此,對于16位ENOB,SINAD≥98 dB

目前市場上的儀表放大器通常不是為驅動ADC輸入而設計的。造成這種情況的最常見的原因,是這些組件缺乏高分辨率ADC所需的線性度。線性度或諧波失真(也稱為THD,即總諧波失真)是最有可能的限制因素,儀表放大器因此而無法直接驅動ADC。當復雜波形被數字化后,一旦其被失真項干擾,訊號便無法與此類干擾區分開來,數據擷取將被破壞!驅動器還應能夠從之前解釋的ADC輸入電荷注入瞬態中快速穩定下來。

當下的解決方案得到改善

現在,新的儀表放大器系列不僅能夠完成儀表放大器傳統上所做的所有事情,而且能非常良好地直接驅動ADC并保護ADC輸入! LT6372-1 (支援0dB到60dB的增益)和 LT6372-0.2 (支持–14dB到+46dB的增益/衰減)可以協助完成精密傳感器接口的任務,直接驅動ADC輸入。

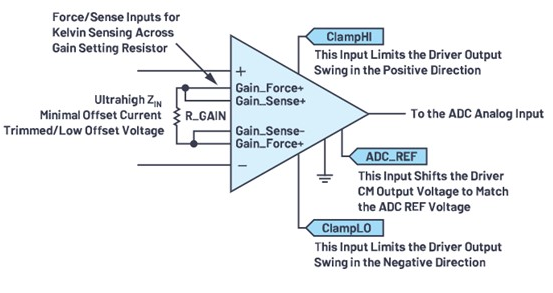

圖3:理想的傳感器放大器/ADC驅動器

使用諸如LT6372系列的高精度、低噪聲儀表放大器來直接驅動ADC模擬輸入具有明顯的優勢,無需再增加一個放大或緩沖級。其中的一些好處包括:減少組件數量,降低功耗和成本,縮小電路板面積,提供高CMR、卓越的直流精度、低1/f噪聲,透過單一組件選擇增益。

許多被選作ADC驅動器的高速運算放大器可能沒有LT6372系列所具有的低1/f噪聲特性,原因是后者采用專有制程制造。此外,可能需要增加額外的緩沖和增益級以放大微小的傳感器訊號。采用儀表放大器直接驅動ADC時,放大器級或基準電壓源都沒有與之相當的額外噪聲源或直流偏移項。

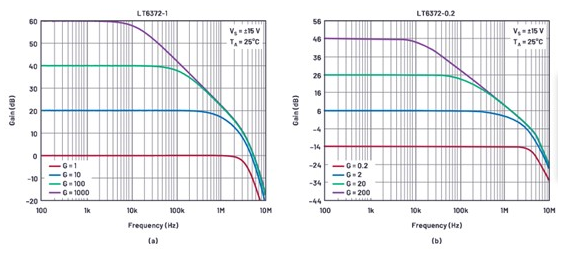

LT6372-1和LT6372-0.2具有極高的輸入阻抗,可以與傳感器或類似訊號輸入接口,并提供大增益(LT6372-1)或衰減(LT6372-0.2)而不會引起負載效應,同時其低失真和低噪聲可確保精確轉換而不會降低性能,支持16位和更低分辨率ADC以高達150kSPS的速率運作。圖4顯示在給定增益設定下,每個組件可實現的帶寬。

圖4:LT6372-1和LT6372-0.2在各種增益下的頻率響應

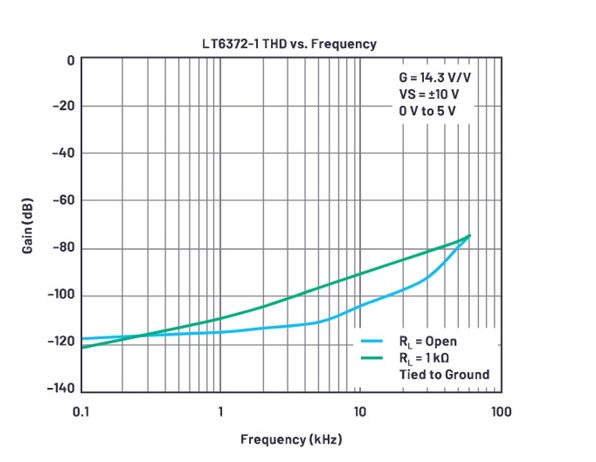

LT6372-1失真與頻率的關系參見圖5,應確保失真項不會影響ADC在最高目標頻率的THD性能。以ADC LTC2367-16 為例,其SINAD規格為94.7dB。為確保驅動器不是主要因素,圖5顯示LT6372-1是小于約5kHz頻率的合適選擇。

圖5:LT6372-1 THD與頻率的關系

LT6372-1用于ADC驅動器的精妙之處

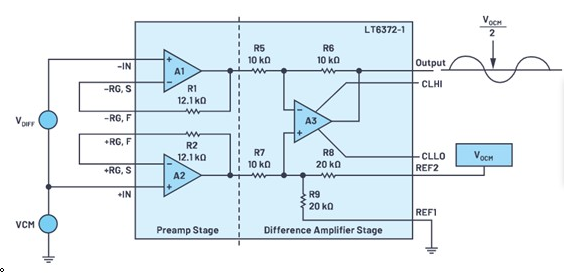

除前面提到的優點之外,LT6372系列的分離基準電壓架構(在圖6中顯示為分開的RF1和RF2接腳)則允許以將訊號直接有效地平移到ADC FS電壓范圍內,而無需使用額外的基準電壓源和其他外部電路來達到相同目的,從而降低成本和復雜性。對于大多數ADC,REF2(此處顯示與VOCM直流電壓相連)將與ADC VREF電壓相連,這將確保ADC模擬輸入中間位準為VREF/2。

圖6:LT6372分離基準電壓用于將訊號移至ADC模擬輸入訊號范圍內

LT6372系列的內建輸出箝位(CLHI和CLLO)確保ADC的敏感輸入不會受到正向或負向瞬變的破壞或可能的損害。該系列支持無失真的輸出擺幅達到箝位電壓,并能夠快速響應和恢復,從而在可能的瞬變觸發任一箝位之后保護ADC并使之迅速恢復正常工作。

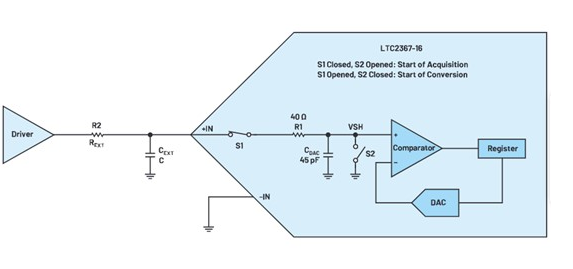

有些SAR ADC的模擬輸入為放大器驅動帶來了具挑戰性的負載。放大器需要有低噪聲和快速建立特性,并具備高直流精度,以將干擾訊號的擾動保持在一個LSB或更小。更高的采樣速率和更高階的ADC對放大器的要求也更高。圖7顯示了典型SAR ADC的輸入。

圖7:采集/采樣模式下的SAR ADC輸入

圖7所示的切換位置對應于采樣或采集模式,在該模式下,模擬輸入連接到采樣電容CDAC,然后在下一會話開始轉換。

在此階段開始之前,切換S2已將CDAC電壓放電至0V或其他偏置點,例如FS/2。在采樣周期開始時,S1閉合且S2斷開,VSH和模擬輸入的電壓差導致瞬態電流流動,使得CDAC可以充電達到模擬輸入電壓。對于較高采樣速率的ADC,該電流可能高達50mA。電容CEXT有助于緩解該電流階躍引起的放大器輸出電壓的階躍變化,但放大器仍會受到其干擾,需要在采集周期結束之前及時建立。電阻REXT將驅動器與CEXT隔開,并且在驅動大電容時還能降低其對穩定性的影響。關于REXT和CEXT值的選擇,需要權衡這種電流注入造成的更大隔離與以這種方式形成的低通濾波器所導致的建立時間性能下降。此濾波器也有助于減小帶外噪聲并改善SNR,不過這不是其主要功能。

ADC前端RC組件值設計

選擇REXT和CEXT的值時要考慮很多因素。以下是影響FFT或其他方式測得的ADC動態響應的因素總結:

CEXT:充當輸入電荷反沖的電荷桶,使電壓階躍最小,從而改善建立時間。

太大:可能會影響放大器穩定性,并可能將LPF滾降頻率降得太低而無法讓訊號通過。

太小:ADC輸入的電荷反沖太大,無法及時建立。

REXT:在放大器輸出和CEXT之間提供隔離,以確保穩定性。

太大:可能會使建立時間常數過長。當計入ADC輸入非線性阻抗時,也可能導致THD升高1。可能會增加IR壓降誤差。

太小:由于CEXT,放大器可能變得不穩定或其正向路徑建立可能會受到影響。

下面是設計REXT和CEXT值的一些設計步驟,以LT2367-16 ADC為例,其由LT6372-1驅動,最大輸入頻率fIN為2kHz,采樣速率為150kSPS:

選擇足夠大的CEXT充當電荷桶,大幅減少電荷反沖:

其中:

CDAC:ADC輸入電容 = 45 pF (LTC2367-16)

→ CEXT = 10 nF (選定值)

使用下式計算ADC輸入電壓階躍VSTEP:

其中:

VREF = 5 V (LTC2367-16)

CDAC: ADC輸入電容 = 45 pF (LTC2367-16)

CEXT = 10 nF(之前)

→ VSTEP = 22 mV (計算值)

注意:此VSTEP函數假設CDAC在每個采樣周期結束時都放電至地,LTC2367-16也是如此。參考文獻1中的VSTEP公式使用了不同的假設,因為它是針對ADC架構的,CDAC電壓對于每個樣本保持不變。

假設階躍輸入以指數方式建立,計算需要多少個輸入REXT×CEXT時間常數NTC才能建立:

其中:

VSTEP:之前計算的ADC輸入電壓階躍

VHALF_LSB:LSB/2,單位為伏特。對于5V FS和16位,其為 38μV (= 5V/217)

→ NTC = 6.4個時間常數

計算時間常數τ:

其中:

tACQ:ADC采集時間;tACQ = tCYC – tHOLD

假設采樣率為150kSPS:

tCYC = 6.67μs (= 1/150kHz)

tHOLD = 0.54μs (LTC2367-16)

因此:tACQ = 6.13μs

→ τ ≤ 0.96 μs

在已知τ和CEXT的情況下,可以計算REXT

→ REXT ≤ 96 Ω

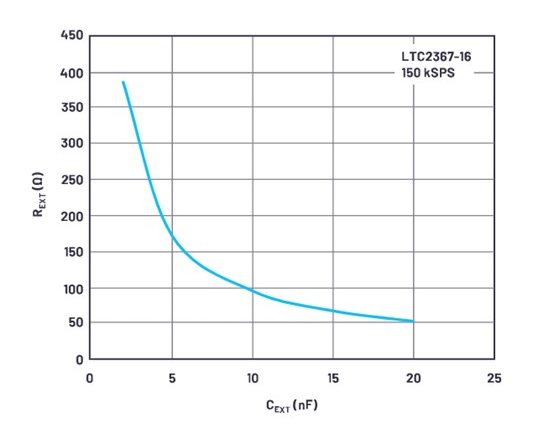

現在我們有了外部RC值,所選ADC可以適當地建立。如果計算出的REXT過高,可以增加CEXT并重新計算REXT以減小其值,反之亦然。圖8顯示了CEXT的選定值和對應的REXT值,用以簡化本例工作條件下的計算任務。

圖8:ADC正確建立對應的外部輸入RC關系。

使用前面的步驟找到合適的REXT和CEXT起始值。應執行基準檢驗和評估,并根據需要優化這些值,同時牢記此類變動對性能的影響。

總結

本文介紹一個新的儀表放大器系列,它能協助連通傳感器與數據擷取組件。文中并詳細探討這些組件的特性,并透過一個實際的例子說明了如何設計ADC前端組件,以確保驅動器與ADC的組合能夠達到預期的分辨率。

責任編輯:lq

-

傳感器

+關注

關注

2548文章

50698瀏覽量

752064 -

adc

+關注

關注

98文章

6438瀏覽量

544116 -

數字化

+關注

關注

8文章

8619瀏覽量

61643

發布評論請先 登錄

相關推薦

如何將多個ESP連接到一個ESP并向服務器發送數據?

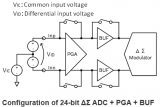

RX23E-A 24bit ΔΣADC基礎篇(2)用于傳感器測量的Δ∑ADC的特性

CAN如何將雙通道ADC連接到FX3控制器?

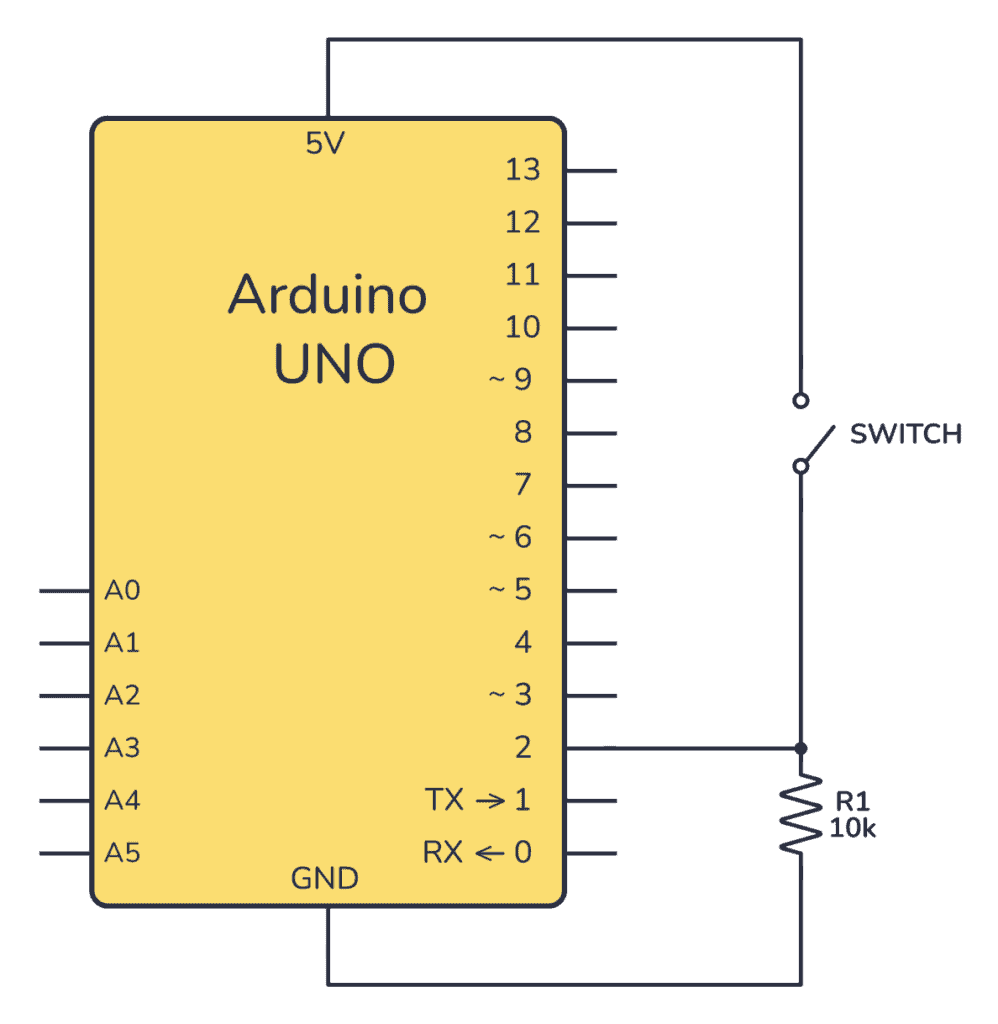

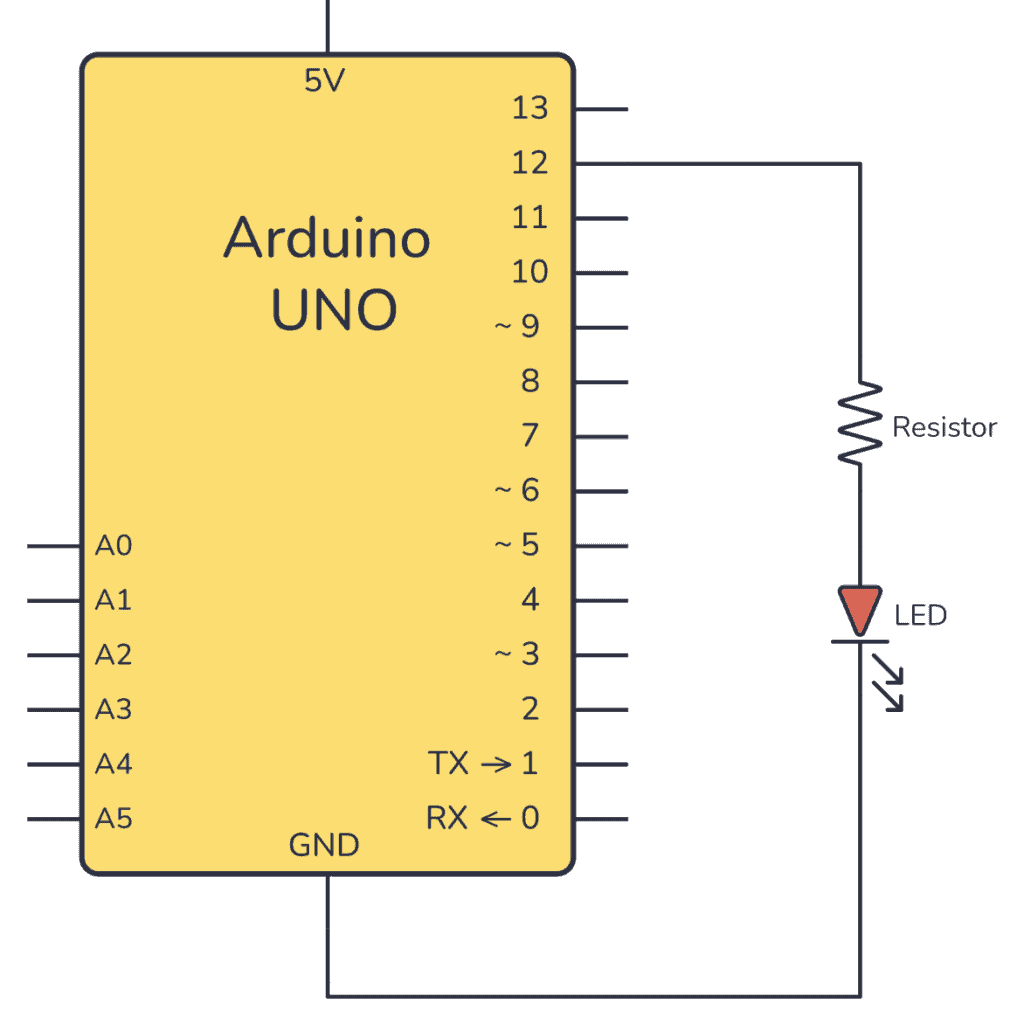

如何將按鈕連接到Arduino板

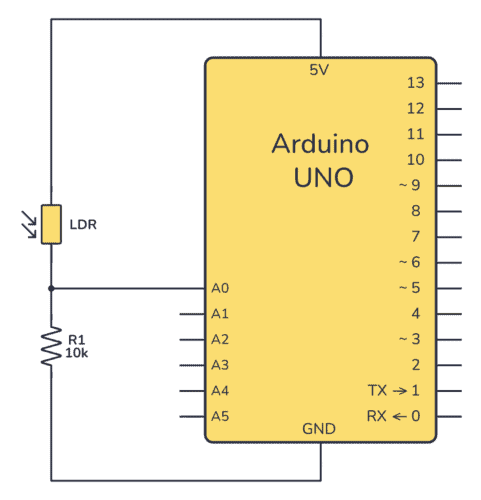

如何將光敏電阻連接到Arduino板并讀取電壓

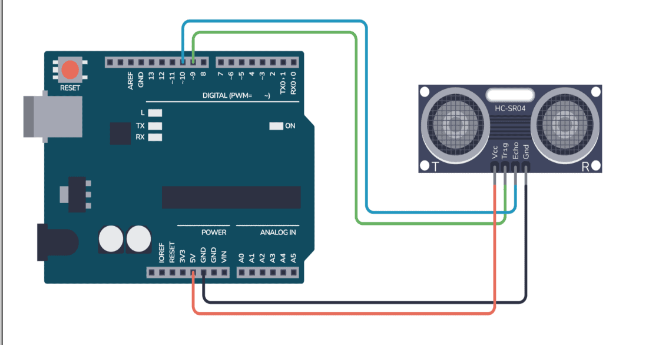

如何將HC-SR04連接到Arduino并編寫一個簡單的程序來測量距離

教你如何將微小的傳感器訊號正確連接到ADC

教你如何將微小的傳感器訊號正確連接到ADC

評論