1 引言

近年來,可編程邏輯器件的發(fā)展,使得SOPC (System On A Programmable Chip,可編程片上系統(tǒng))成為可能, 即在一塊可編程芯片上實(shí)現(xiàn)整個(gè)系統(tǒng)。Nios是Altera公司開發(fā)的可用于SOPC設(shè)計(jì)的處理器軟核。基于Nios軟核的SOPC系統(tǒng),其最大特點(diǎn)就是靈活,可以根據(jù)自己的需要靈活改變Nios的外圍設(shè)備,使得硬件利用效率達(dá)到最高,同時(shí)它具有ISP(In System Programmable,在系統(tǒng)編程)的功能,可裁減,可擴(kuò)充,可升級。本文充分利用了Nios系統(tǒng)靈活定制的優(yōu)點(diǎn),設(shè)計(jì)實(shí)現(xiàn)了一套CT機(jī)掃描系統(tǒng)控制器。

2 CT掃描系統(tǒng)控制器

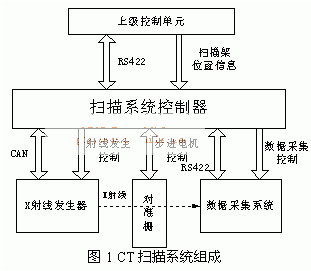

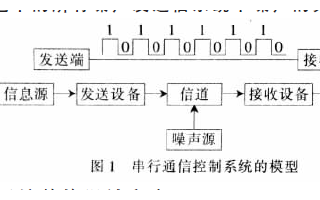

CT機(jī)是根據(jù)不同密度和厚度的物體對X射線的吸收程度不同的原理,通過計(jì)算機(jī)成像技術(shù),對病人身體成像的一種醫(yī)學(xué)設(shè)備。CT機(jī)掃描系統(tǒng)由X射線發(fā)生系統(tǒng),數(shù)據(jù)采集系統(tǒng),對準(zhǔn)柵三個(gè)子系統(tǒng)組成,如圖1所示。掃描系統(tǒng)由掃描架承載,掃描架是一個(gè)旋轉(zhuǎn)體,掃描系統(tǒng)隨著掃描架旋轉(zhuǎn),以獲得不同角度下的人體信息,掃描架旋轉(zhuǎn)一周所得數(shù)據(jù)可產(chǎn)生圖像。

掃描系統(tǒng)的三部分中,X射線發(fā)生系統(tǒng)產(chǎn)生射線,掃描系統(tǒng)控制器通過CAN總線和它通信,發(fā)送X射線參數(shù)和動作指令,同時(shí)接收X射線發(fā)生器的狀態(tài)信息。數(shù)據(jù)采集系統(tǒng)負(fù)責(zé)對X射線采樣和傳輸數(shù)據(jù),它掃描系統(tǒng)控制器采用RS422總線與其通信,發(fā)送控制指令,并接收指令執(zhí)行狀態(tài)。同時(shí)有IO接口用作采樣觸發(fā)脈沖和采樣使能。對準(zhǔn)柵通過擋板來調(diào)節(jié)X射線的開口寬度,擋板由一個(gè)步進(jìn)電機(jī)驅(qū)動。掃描系統(tǒng)控制器接收來自上級的開口寬度指令,然后發(fā)出控制脈沖,控制步進(jìn)電機(jī)到達(dá)指定位置,通過編碼器接收步進(jìn)電機(jī)轉(zhuǎn)子位置信號,形成閉環(huán)。

CT掃描系統(tǒng)控制器負(fù)責(zé)三個(gè)子系統(tǒng)的協(xié)調(diào)控制,為掃描系統(tǒng)中設(shè)備的通信中心和控制中心。首先它和上級控制單元通信,接收指令和匯報(bào)各子系統(tǒng)狀態(tài),其次與各子系統(tǒng)通信,發(fā)送控制指令,并接收子系統(tǒng)的狀態(tài)信息。它根據(jù)接收到的控制指令和掃描架的位置信息,控制對準(zhǔn)柵到達(dá)指定寬度,產(chǎn)生控制X射線發(fā)生和采樣的時(shí)序。可見,CT掃描系統(tǒng)控制器包括了實(shí)時(shí)通信、電機(jī)控制,時(shí)序控制,是一個(gè)多任務(wù)的系統(tǒng)。并且對實(shí)時(shí)性要求也很高,任何一點(diǎn)時(shí)序發(fā)生偏差,都會對病人造成不必要的傷害。

本文使用SOPC的方式,設(shè)計(jì)了以一片FPGA為核心的CT機(jī)掃描系統(tǒng)控制器硬件,定制了基于Nios軟核的FPGA系統(tǒng),然后設(shè)計(jì)了基于實(shí)時(shí)操作系統(tǒng)Nucleus的應(yīng)用軟件,實(shí)現(xiàn)了CT機(jī)掃描系統(tǒng)控制器的上述功能。

3 基于Nios的硬件設(shè)計(jì)

本文使用了Altera 公司的FPGA Cyclone EP1C20,它擁有充足的可編程資源來實(shí)現(xiàn)SOPC。因?yàn)橄到y(tǒng)所有功能均由FPGA實(shí)現(xiàn),硬件電路除FPGA外只需加上存儲器件和一些物理層接口芯片即可。本文使用了一片8M Byte FLASH、一片16M Byte SDRAM,CAN總線收發(fā)器和RS422總線收發(fā)器等作為FPGA的外圍設(shè)備,硬件電路的結(jié)構(gòu)簡單明了,提高了系統(tǒng)的可靠性。FPGA系統(tǒng)運(yùn)行時(shí)鐘為50MHz,保證了系統(tǒng)的運(yùn)算速度。

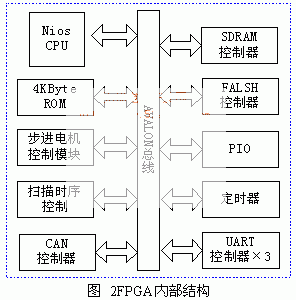

通過Altera的SOPC Builder軟件包可以定制基于Nios軟核的FPGA系統(tǒng),它提供了一些基本的Nios外設(shè)模塊,如UART控制器、定時(shí)器、FLASH控制器、SDRAM控制器等。本文設(shè)計(jì)的CT掃描系統(tǒng)控制器FPGA內(nèi)部結(jié)構(gòu)如圖2所示。

Nios是流水線結(jié)構(gòu)的RISC 軟核處理器,它可以選擇32位架構(gòu)或者16位架構(gòu)。本文使用32位架構(gòu),并在SOPC Builder中設(shè)置了4K Byte數(shù)據(jù)緩存和指令緩存,以節(jié)省CPU讀取數(shù)據(jù)和指令的時(shí)間,提高系統(tǒng)性能。

由圖2可見,Nios軟核通過AVALON總線與各擴(kuò)展模塊相連接。AVALON總線是專門用于Nios連接外設(shè)的一種總線結(jié)構(gòu),它具有分離的地址,數(shù)據(jù)和控制線,并提供動態(tài)動態(tài)總線寬度調(diào)整等功能。Nios軟核為其主設(shè)備。

AVALON總線上的從設(shè)備有SDRAM控制器,F(xiàn)lash控制器、定時(shí)器、通信接口UART控制器和CAN 控制器。在設(shè)計(jì)Nios軟核的外設(shè)時(shí),采用已有的IP核能有效縮短設(shè)計(jì)周期,同時(shí)經(jīng)過充分驗(yàn)證的IP核也保證了設(shè)計(jì)的可靠性。本文根據(jù)需要采用了三個(gè)UART控制器作為Nios軟核的外設(shè),分別用于與上級單元通信、與數(shù)據(jù)采集系統(tǒng)通信和調(diào)試信息輸出;還使用了CAST公司的IP 核作CAN 控制器,它支持CAN 2.0協(xié)議。

在FPGA片內(nèi),使用了4 Kbyte的ROM,此ROM中包含了Altera提供的GERMS Monitor啟動引導(dǎo)程序,它可以實(shí)現(xiàn)啟動引導(dǎo)、程序下載和基本調(diào)試功能。在調(diào)試中,通過調(diào)試串口和GERMS Monitor通信,將可執(zhí)行的映象文件下載到SDRAM或FLASH中。

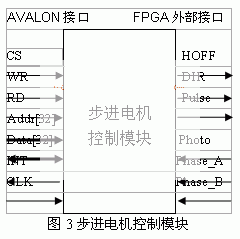

另外,本文根據(jù)應(yīng)用的特殊要求設(shè)計(jì)了自定義模塊——掃描時(shí)序控制模塊和步進(jìn)電機(jī)控制模塊。在SOPC系統(tǒng)中,更容易選擇系統(tǒng)功能是由運(yùn)行于Nios中的軟件實(shí)現(xiàn),還是使用FPGA硬件實(shí)現(xiàn),由此可以均衡系統(tǒng)軟硬件的功能,使效率達(dá)到最高。系統(tǒng)功能用FPGA硬件實(shí)現(xiàn)的優(yōu)勢在于數(shù)據(jù)的并行處理,實(shí)時(shí)響應(yīng)非常快;而用處理器軟件實(shí)現(xiàn)的優(yōu)勢在于通訊和復(fù)雜情況的判斷等。本文中為了提高系統(tǒng)的實(shí)時(shí)性,將步進(jìn)電機(jī)控制在FPGA中實(shí)現(xiàn)。步進(jìn)電機(jī)控制FPGA模塊如圖3所示。

圖3右邊為AVALON總線接口,由片選,地址線、數(shù)據(jù)線、讀寫使能和中斷信號組成。左邊為FPGA的輸出,即與步進(jìn)電機(jī)驅(qū)動器接口:DIR為步進(jìn)電機(jī)運(yùn)行方向控制,Pulse為步進(jìn)電機(jī)的控制脈沖,HOFF為保持信號。下方三個(gè)信號為編碼器的反饋信號,分別是A相脈沖、B相脈沖和初始位置信號。步進(jìn)電機(jī)控制模塊接收Nios通過AVALON總線發(fā)送來的目標(biāo)位置信息,然后根據(jù)當(dāng)前位置及目標(biāo)位置,得到到達(dá)目標(biāo)所需的步進(jìn)電機(jī)的脈沖數(shù),發(fā)出相應(yīng)的脈沖。同時(shí),根據(jù)反饋的編碼器信號,解碼得到電機(jī)當(dāng)前位置信息,并判斷步進(jìn)電機(jī)運(yùn)動是否達(dá)到目標(biāo)位置,控制任務(wù)是否完成。然后產(chǎn)生中斷,通知Nios軟核任務(wù)完成情況。可見運(yùn)行于Nios中的軟件只需將目標(biāo)位置通知電機(jī)控制模塊即可,大大減輕了CPU的負(fù)擔(dān)。

4 軟件設(shè)計(jì)

由前文可以看出,掃描系統(tǒng)控制器需要完成多項(xiàng)功能,軟件體系復(fù)雜,而且通信、掃描控制、電機(jī)控制等環(huán)節(jié)要求很高的實(shí)時(shí)和并發(fā)性。在這種情況下,采用傳統(tǒng)的基于前后臺的嵌入式軟件設(shè)計(jì)方法將存在很大的困難,軟件設(shè)計(jì)結(jié)構(gòu)復(fù)雜,工作量大,且開發(fā)周期長,功能擴(kuò)展受限。嵌入式實(shí)時(shí)操作系統(tǒng)為系統(tǒng)軟件設(shè)計(jì)提供了良好的開發(fā)平臺,承擔(dān)起系統(tǒng)資源管理的責(zé)任。這樣就簡化了應(yīng)用程序設(shè)計(jì),保障了軟件質(zhì)量,縮短了開發(fā)周期。本文采用了ATI公司開發(fā)的Nucleus操作系統(tǒng),Nucleus是一個(gè)搶先式多任務(wù)操作系統(tǒng)內(nèi)核,具有源代碼開放、性價(jià)比高、功能模塊豐富等優(yōu)點(diǎn)。

本文中,軟件結(jié)構(gòu)可分為三個(gè)結(jié)構(gòu)層次,最底層為硬件抽象層,主要由Nios軟核外設(shè)驅(qū)動程序中斷服務(wù)程序以及板級初始化程序組成,外設(shè)驅(qū)動程序包括UART控制器, CAN控制器, 步進(jìn)電機(jī)控制模塊,掃描控制模塊的驅(qū)動程序,此部分是操作系統(tǒng)與底層硬件的接口。第二層為Nucleus操作系統(tǒng)內(nèi)核及其服務(wù),它提供任務(wù)調(diào)度,中斷管理,內(nèi)存管理、定時(shí)控制等服務(wù)。最高層為應(yīng)用軟件層,運(yùn)行在操作系統(tǒng)之上,完成所有的應(yīng)用功能。

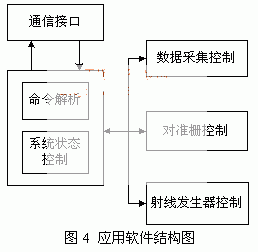

根據(jù)系統(tǒng)功能,應(yīng)用軟件結(jié)構(gòu)如圖4所示:

系統(tǒng)管理單元是系統(tǒng)工作的核心,包括兩個(gè)任務(wù):命令解析任務(wù)和系統(tǒng)狀態(tài)控制任務(wù)。命令解析任務(wù)接收上級控制單元指令,將其解析為各個(gè)子系統(tǒng)需要完成的任務(wù)目標(biāo),并發(fā)送給各個(gè)子系統(tǒng)控制單元。子系統(tǒng)控制單元控制子系統(tǒng)完成指令。系統(tǒng)狀態(tài)控制任務(wù)是一個(gè)狀態(tài)機(jī),控制著CT掃描系統(tǒng)的運(yùn)行狀態(tài)。它根據(jù)當(dāng)前的系統(tǒng)狀態(tài)和上級指令,判斷系統(tǒng)的目標(biāo)動作,控制掃描時(shí)序,同時(shí)和各子系統(tǒng)管理單元通信,同步各子系統(tǒng)管理單的任務(wù)執(zhí)行,并將各子系統(tǒng)狀態(tài)發(fā)送給上級控制單元。本文采用信號量和事件的手段同步各任務(wù)。

數(shù)據(jù)采集管理單元是控制器與數(shù)據(jù)采集系統(tǒng)的接口,它負(fù)責(zé)數(shù)據(jù)采集系統(tǒng)的初始化、數(shù)據(jù)采集參數(shù)設(shè)置、數(shù)據(jù)采集系統(tǒng)狀態(tài)監(jiān)控和對其錯(cuò)誤狀態(tài)進(jìn)行處理。這部程序分包括串口通訊接收任務(wù)和數(shù)據(jù)采集系統(tǒng)管理任務(wù)。

由前文可知步進(jìn)電機(jī)控制功能由FPGA硬件實(shí)現(xiàn),因此對準(zhǔn)柵管理單元的工作變得十分簡單,它從系統(tǒng)狀態(tài)控制部分接收對準(zhǔn)柵開口寬度,將其傳遞給步進(jìn)電機(jī)控制模塊,然后通過步進(jìn)電機(jī)控制模塊的中斷服務(wù)程序,監(jiān)控任務(wù)完成情況。

與數(shù)據(jù)采集控制類似,射線發(fā)生器控制部分負(fù)責(zé)射線發(fā)生器的初始化、射線參數(shù)設(shè)置、監(jiān)控射線發(fā)生器狀態(tài)和異常情況處理。它包括一個(gè)射線發(fā)生控制任務(wù)和CAN通訊處理任務(wù)。射線發(fā)生控制任務(wù)負(fù)責(zé)完成射線發(fā)生器的參數(shù)管理和狀態(tài)監(jiān)控,CAN通訊任務(wù)完成CAN總線數(shù)據(jù)的收發(fā)功能。

上述任務(wù)均為事件驅(qū)動方式,在系統(tǒng)不工作時(shí),Nios處理器處于空閑狀態(tài),這樣可以降低系統(tǒng)功耗。任務(wù)間通訊采用管道(Pipe)的方式,管道的優(yōu)點(diǎn)是可以傳輸變長的數(shù)據(jù)。CT掃描系統(tǒng)控制器需要接收系統(tǒng)配置、掃描、故障診斷等不同長度的上級控制指令,所以在命令解析任務(wù)與通信接口任務(wù)之間采用管道進(jìn)行通訊,另一方面命令解析任務(wù)向各子系統(tǒng)控制任務(wù)發(fā)送的指令長度也是不確定的,所以與三個(gè)子系統(tǒng)管理單元通訊也采用管道的方式。

合理的配置任務(wù)優(yōu)先級是嵌入式系統(tǒng)軟件可靠工作的必要條件。本文中,任務(wù)的根據(jù)重要程度可分為三個(gè)層次:首先是系統(tǒng)狀態(tài)控制,它是系統(tǒng)運(yùn)行的中樞,同時(shí)控制著掃描時(shí)序,必須保證狀態(tài)控制任務(wù)的暢通運(yùn)行,因此它具有最高優(yōu)先級設(shè)為1。其次是與上級控制單元的接口,包括串口通信任務(wù)和命令解析任務(wù),控制器必須準(zhǔn)確的接收上級單元的命令并及時(shí)反饋,所以這兩個(gè)任務(wù)優(yōu)先級設(shè)為2。最后是各子系統(tǒng)管理任務(wù),其中射線管理單元如果誤操作,可能對人員造成損害,所以它的兩個(gè)任務(wù)優(yōu)先級較高,設(shè)為3,其余子系統(tǒng)管理單元任務(wù)較低均設(shè)為4。

本文的應(yīng)用軟件使用GNU交叉編譯器編譯,然后經(jīng)ATI公司的Codelab軟件調(diào)試通過。

5 實(shí)驗(yàn)驗(yàn)證

為驗(yàn)證調(diào)試CT掃描系統(tǒng)控制器,搭建了測試平臺。測試平臺由一臺PC機(jī)、CT數(shù)據(jù)采集系統(tǒng)和對準(zhǔn)柵組成,其中PC機(jī)模擬CT掃描系統(tǒng)控制器的上級單元和 X射線發(fā)生系統(tǒng)。

通過監(jiān)聽與上下級控制單元的通訊,測量對準(zhǔn)柵的開口寬度,測量控制器輸出的數(shù)據(jù)采集和射線發(fā)生控制信號波形,證明,本文設(shè)計(jì)的CT掃描系統(tǒng)控制器能夠滿足多任務(wù)實(shí)時(shí)處理的要求。

6 結(jié)論

本文采用SOPC方式設(shè)計(jì)實(shí)現(xiàn)了多任務(wù),實(shí)時(shí)響應(yīng)的CT掃描系統(tǒng)控制器。硬件設(shè)計(jì)以Nios軟核和FPGA為核心,充分利用SOPC系統(tǒng)的靈活定制的特點(diǎn),簡化了電路結(jié)構(gòu),縮短了設(shè)計(jì)周期,減輕了處理器運(yùn)算負(fù)擔(dān)。同時(shí)基于嵌入式實(shí)時(shí)操作系統(tǒng)Nucleus的結(jié)構(gòu)化、層次化應(yīng)用程序設(shè)計(jì),保證了系統(tǒng)的軟件質(zhì)量和實(shí)時(shí)性。試驗(yàn)表明,本文設(shè)計(jì)的CT機(jī)掃描系統(tǒng)控制器滿足多任務(wù)實(shí)時(shí)處理的要求。

本文作者的創(chuàng)新點(diǎn):使用基于Nios軟核和實(shí)時(shí)操作系統(tǒng)的方式實(shí)現(xiàn)了實(shí)時(shí)多任務(wù)控制系統(tǒng),充分利用了Nios軟核靈活定制的特點(diǎn),使用硬件加速的方式減輕了處理器負(fù)擔(dān),保證了系統(tǒng)性能。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19178瀏覽量

229201 -

FPGA

+關(guān)注

關(guān)注

1626文章

21678瀏覽量

602043 -

控制系統(tǒng)

+關(guān)注

關(guān)注

41文章

6550瀏覽量

110498

發(fā)布評論請先 登錄

相關(guān)推薦

Cyclone_II_EP2C20_原理

DSP+FPGA電機(jī)控制系統(tǒng)

基FPGA Cyclone II_EP2C5 EP2C8的頻

基于cyclone EP1C6的LED 屏設(shè)計(jì)方案

基于PLC的液體CT探測器控制系統(tǒng)設(shè)計(jì)

基于FPGA的激光測距控制系統(tǒng)設(shè)計(jì)

基于FPGA的激光測距控制系統(tǒng)設(shè)計(jì)

基于ARM和FPGA的LED顯示屏控制系統(tǒng)的設(shè)計(jì)

基于ARM與FPGA的嵌入式數(shù)控系統(tǒng)設(shè)計(jì)

基于cyclone EP1C6的LED大屏方案

基于EP1C3的進(jìn)階實(shí)驗(yàn)_Cyclone_PLL_Test1

基于EP1C3的進(jìn)階實(shí)驗(yàn)Cyclone_PLL_Test1

基于Cyclone_EP1C6240C8_FPGA的ADS2807接口程序

如何使用FPGA進(jìn)行串行通信控制系統(tǒng)的設(shè)計(jì)

基于FPGA Cyclone EP1C20實(shí)現(xiàn)CT機(jī)掃描控制系統(tǒng)的應(yīng)用方案

基于FPGA Cyclone EP1C20實(shí)現(xiàn)CT機(jī)掃描控制系統(tǒng)的應(yīng)用方案

評論