作者:劉一平;楊亮亮;凌朝東;李國剛 來源:現代電子技術

1 引言

HHCE(Home Health Care Engineering)這門學科正隨著人類對健康的重視和遠程醫療的發展而逐漸走進人們的生活,它提倡的是一種“在家就醫,自我保健,遠程診斷”的理念,把高科技與醫療結合起來。HHCE的出現符合21世紀社會老齡化、醫療費用日益高漲以及人們生活健康質量高要求的趨勢,同時可實現醫療資源共享,提高邊遠地區的醫療水平,因此具有特別旺盛的生命力。

HHCE系統提供一種對于家庭、社區醫療、出診醫生有效便捷的醫療監測解決方案,具有心電信號監測功能的監測器是HHCE系統的重要組成部分。就國內而言,該類產品的研究也屬于剛起步階段,遠程網絡也只是簡單的完成數據庫醫療數據的存儲和傳輸,還沒有真正完成將網絡與醫療器械相結合。在國際方面,世界各國在此的研究均投入大量資金,但依然主要是使用價格昂貴的儀器完成醫療數據采集,然后依托PC/internet網絡完成數據采集以及網絡診斷。

本設計采用了Altera公司的NiosⅡ軟核處理器作為CPU,并移植了當今主流的μClinux操作系統。該系統具有系統穩定、便攜式、功能可升級擴展、面向用戶、遠程控制等特點。一方面,它將家庭保健和遠程醫療結合起來,主要面向用戶終端設計,使個人能夠方便的對自身心電信號的進行自我檢測與分析,實時了解自己的身體健康狀況;另一方面,采集到的數據還可以通過存儲卡存儲,以便對數據進行長期分析處理和診斷;除此之外,系統還可以通過網絡等遠端通訊設施與醫療保健服務端(如醫院、私人醫師、監護中心、保健中心等)快速建立連接,將測量數據傳遞給遠程數據庫或醫生。有利于醫療信息的數據庫管理和遠程實時監護、診斷,使用戶不用出門就能得到最及時有效的診斷。

2 系統介紹

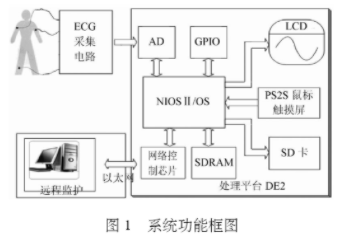

遠程心電醫療信號監測系統主要由心電信號的前端采集與調理模塊、心電信號處理與存儲模塊、數據顯示模塊和遠程傳輸控制模塊等4個關鍵模塊組成,系統功能結構如圖1所示。

該監測系統的硬件平臺采用Altera公司CycloneⅡ2C35 FPGA芯片,采用SOPC(片上可編程系統)技術將NiosⅡ軟核處理器、存儲器、功能接口和擴展I/O口等集成在一塊FPGA芯片上,外圍擴展心電數據采集板、網絡、LCD屏、觸摸屏/鍵盤、SD存儲卡等硬件來實現系統的硬件架構,且帶有可擴展的I/O接口,便于以后系統功能升級與擴展。

3 系統關鍵模塊的設計

3.1 NiosⅡ嵌入式軟核處理器簡介

NiosⅡ系列嵌入式處理器是Altera公司推出的軟核處理器。用戶可以獲得超過200 DMIPS的性能,而只需花費不到35美分的FPGA邏輯資源。NiosⅡ支持MicroC/OS-Ⅱ、μClinux等多種實時操作系統,支持輕量級TCP/IP協議棧,允許用戶增加自定義指令和自定義硬件加速單元,無縫移植自定義外設和接口邏輯,在性能提升的同時,方便了用戶的設計。

NiosⅡ處理器采用Avalon交換式總線,該總線是Altera開發的一種專用的內部連線技術。Avalon交換式總線由SOPC Builder自動生成,是一種用于系統處理器、內部模塊以及外設之間的內聯總線。Avalon交換式總線使用最少的邏輯資源來支持數據總線的復用、地址譯碼、等待周期的產生、外設的地址對齊、中斷優先級的指定以及高級的交換式總線傳輸。

3.2 心電信號采集調理模塊設計

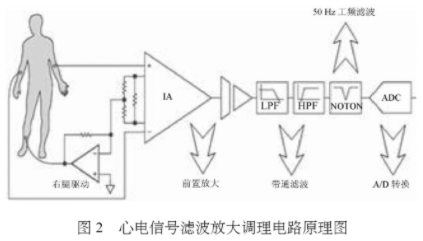

對ECG信號采集采用模塊化的設計方式,主要由前端的導聯傳感器、信號濾波放大調理電路和A/D采樣電路組成。人體心電信號的主要頻率范圍為0.05~100 Hz,幅度約為0~4 mV,信號十分微弱。同時心電信號中通常混雜有其他生物電信號,加之體外以50 Hz工頻干擾為主的電磁場干擾,使得心電噪聲背景較強,測量條件比較復雜。為了不失真地檢測出有臨床價值的心電信號,信號濾波與放大調理部分主要由一下幾個電路組成:前置放大電路、高低通濾波電路、陷波電路與A/D轉換電路,電路原理圖如圖2所示。

首先心電導聯采集過來的微弱心電信號通過前置放大電路進行放大,此部分包括右腿驅動以抑制共模干擾、屏蔽線驅動以消除引線干擾,增益設成10倍左右。設計前置放大采用美國模擬器件公司生產的醫用放大器AD620。AD620由傳統的三運算放大器發展而成,為同相并聯差動放大器的集成。其具有電源范圍寬(±2.3~±18 V),設計體積小,功耗低(最大供電電流僅1.3 mA)的特點,因而適用于低電壓、低功耗的應用場合。此外還具有有較高的共模抑制比,溫度穩定性好,放大頻帶寬,噪聲系數小等優點。放大后的信號經濾波、50 Hz陷波處理后再進行二次放大,后級增益設成100倍左右。由于ECG信號幅度最大就幾mV,而A/D轉換中輸入信號的幅度要求在1 V以上,所以總增益設成1 000倍左右。其中,濾波采用壓控電壓源二階高(低)通濾波電路,用于消除0.05~100 Hz頻帶以外的肌電等干擾信號,工頻中的其余高次諧波也可被濾除掉。同時,采用有源雙T帶阻濾波電路進一步抑制50 Hz工頻干擾。

A/D采樣芯片采用TI公司的8位串行芯片TLC549,該芯片采用SPI接口,僅用三條線即可實現采集控制和數據傳輸;具有4 MHz的片內系統時鐘和軟、硬件控制電路,轉換時間小于17μs,采樣速率達40kS/s;采用差分基準電壓技術這個特性,TLC549可能測量到的最小量值達1 000 mV/256,也就是說0~1 V信號不經放大也可以得到8位的分辨率。

3.3 數據采集控制器設計

為了得到經過前端TLC549芯片轉換的心電信號,必須設計一個數據采集控制器,實現對AD芯片的控制與數字化心電數據的獲取。該控制器根據TLC549芯片的工作時序與后端數據處理的需要,采用VerilogHDL自行設計。該控制器具有多路采集的特點。

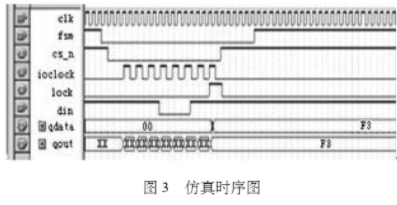

在自TLC549的I/O CLOCK端輸入8個外部時鐘信號期間需要完成以下工作:讀入前次A/D轉換結果;對本次轉換的輸入模擬信號采樣并保持;啟動本次A/D轉換。則一路采集時間為:0.5μs×(3+8×2+1)=10μs,而芯片轉換時間小于17μs,則整個過程時間花費為27μs。為了有效的利用該控制器,在一路A/D轉換期間,同時進行另外一路A/D采樣,這樣就可以在40μs時間內完成對四路信號的采集,大大提高了工作效率。同時,設計中還加入了一個FSM信號來控制采樣時間,從而適應不同頻率信號的采樣頻率。AD芯片的時序仿真圖如圖3所示。

Din為采集數據的串行輸入,時鐘由系統時鐘通過分頻系數得到。設計中,設置了fsm作為采樣控制時鐘,這樣可以根據需要來調整采樣速率。由于進行一次AD采樣的時間很短,無論采用查詢還是中斷直接讀取都是不現實的,這就需要利用緩沖設計,通過把N次轉換的數據暫存在緩沖存儲器中來降低中斷次數。為了取得連續和正確的采集數據,實現無縫緩沖,鑒于FPGA設計的靈活性,本設計采用了雙緩沖存儲的乒乓操作結構。本設計通過將AD采樣時序控制器交替存儲在兩個512 B的雙口RAM(DPRAM)中實現數據的緩存,當其中一個DPRAM1存儲滿后即轉為存儲到另一個DPRAM2中并產生一次中斷,這樣在控制器寫數據到DPRAM2中時系統將有非常充足的時間將DPRAM1中的數據取出。

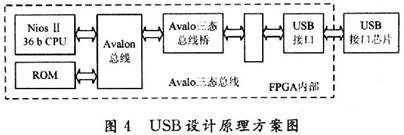

3.4 顯示模塊設計

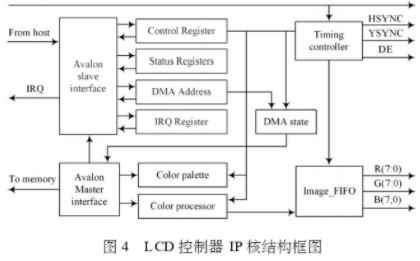

為了能夠直觀地顯示出采集的心電波形,需要顯示設備的支持。本設計采用的LCD面板是TFT 320*240 LCD。該LCD模塊沒有顯示控制器,因此需要設計顯示控制器IP核來驅動LCD面板。本設計實現的顯示控制器IP核采用Verilog HDL設計,支持多種顏色模式,包括18bpp,16bpp,8bpp和自定義模式。圖像存儲器lcd_fifo是采用片內FIFO,可以根據需要進行詞整。256色的顏色查找表采用片內RAM來存儲。圖像信息能夠通過AvaIon總線主端口寫入的突發塊傳輸方式進行傳輸,利用DMA從內存中自動讀取,在SDRAM圖像存儲器image_ram與片上圖像數據緩存器lcd_fifo之間建立了一條專用DMA通道,該控制器結構如圖4所示。

該LCD控制器IP核主要由4個模塊組成:接口模塊、內存模塊、顏色轉換模塊和時序模塊。

接口模塊主要是NiosⅡ處理器對LCD控制器進行控制及狀態讀取。接口模塊主要是以寄存器方式存在的,其中寄存器有:控制寄存器、狀態寄存器、DMA地址寄存器和中斷寄存器。

內存模塊是Avalon總線的主接口部分,在系統啟動之后,利用DMA傳輸模式,通過Avalon總線主端口寫入的突發塊傳輸方式,完成圖像數據存儲器image_ram中的圖像數據到片上圖像數據緩存器lcd_fifo的獨立讀取。采用DAM傳輸方式是為了把NiosⅡ軟核處理器從頻繁地進行數據讀取操作的工作中解脫出來,這樣可以大大提高系統的工作效率。

顏色轉換模塊將讀取后的數據根據4種顏色模式不同進行數據讀取的轉換,其中8bpp和自定義模式由于顏色不足,需要接入顏色查詢表處理。自定義模式可以手動對調色板的地址進行預設來定義輸出的顏色。

時序模塊嚴格按照LCD的時序編寫,其中LCD時鐘為5 MHz。通過控制數據使能信號啟動lcd_fifo數據輸出,逐行掃描顯示。同時,設計該模塊時,在數據有效信號(DE)有效前,須檢查lcd_fifo中是否存有數據,以確定是否進行數據讀取和傳輸;須進行調色板模式設置,在幀傳輸過程中需要進行模式鎖定,以免出現傳輸錯誤;須根據不同bpp模式,確定不同的讀取時間段,18bpp每次都讀取,16bpp間隔1次讀取,8bpp間隔4次讀取。

3.5數據存儲模塊設計

本設計選用SD卡作為外接存儲硬盤。SD存儲卡具有大容量、高性能、安全性好等特點的多功能存儲卡,被廣泛用于數碼相機、掌上電腦和手機等便攜式設備中。SD卡上所有單元由內部時鐘發生器提供時鐘,接口驅動單元同步外部時鐘的DAT和CMD信號到內部所用時鐘。SD卡有兩種通信協議,即SD通信協議和SPI通信協議,與SPI通信協議相比,SD通信協議的最大優點是讀寫速度快,單根數據線理論上可以達到25 MB/s,四線傳輸可以達到100 MB/s,本設計采用的是四線SD通信協議。

本設計中對SD卡的協議采用軟件編寫:首先在SoPC Builder里定義了6個I/O口:SD_CMD,SD_DAT0-DAT3,SD_CLK,分別對應SD卡的命令、數據、時鐘端口,然后在NiosⅡIDE上按照SD卡的傳輸協議編寫C程序來對6個I/O口進行操作,以此來實現SD卡的傳輸協議。在完成SD卡數據塊的讀寫基礎上移植了文件系統。FAT16,這樣在不影響讀寫速度的條件下節省FPGA的資源。

3.6 數據傳輸模塊設計

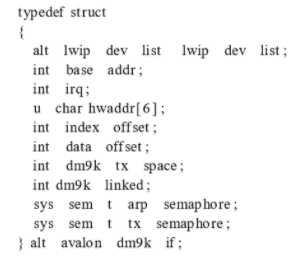

為了實現遠程的數據交換,本系統采用以太網絡進行數據傳輸。設計采用DM9000A作為以太網控制芯片。DM9000A是DAVICOM公司的一款高速網絡控制器,具有通用處理器接口、一個10/100M PHY和4kB的SRAM。為了實現數據的網絡傳輸,設計需要完成的任務有:在NiosⅡ上移植了μClinux操作系統、完成網絡底層驅動程序的設計、基于網絡協議的應用程序開發。其中在NiosⅡ上移植了μClinux操作系統的工作已經完成,因此本設計的關鍵任務是完成網絡驅動程序設計與應用程序開發。

基于DM9000A的HAL設備驅動設計主要分為兩步:首先是DM9000A的Avalon總線接口邏輯設計;其次DM9000A的讀寫驅動程序設計;最后按照HAL的驅動模式將DM9000A的驅動程序移植進HAL。DM9000A是作為Avalon總線的從外設與NiosⅡ進行通信。DM9000A的Avalon總線接口邏輯主要完成芯片信號與Avalon總線接口信號的對接。

DM9000A不允許直接訪問芯片內部的寄存器,需要通過數據端口和索引端口來讀寫。而這兩個端口由CMD管腳控制:當CMD接高電平時為數據端口,CMD接低電平為控制端口。

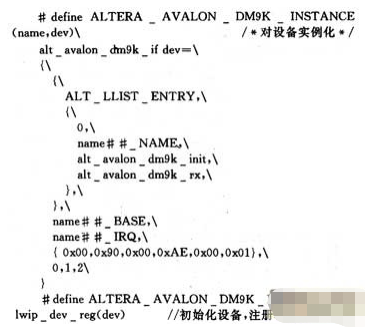

創建HAL設備驅動包括:創建設備實例和登記設備。設計中針對LWIP的結構,定義一個結構體作為DM9000A設備的alt_dev結構:

在NiosⅡ啟動時,將在aIt_sys_init()中對設備初始化,初始化程序如下:

應用程序設計采用TCP/IP、HTTP協議,把監測器作為Web服務器端,遠程PC端作為客戶端通過網頁顯示采集到的心電波形。

4 實驗結果

系統對人體心電信號進行了采集,通過LCD面板進行實時顯示。通過SD卡存儲數據,同時采用以太網網絡將數據發送到遠程的PC端上,以下是對系統功能的驗證與測試結果。

4.1 信號采集調理模塊

心電信號采集調理模塊是自行設計的采集板,主要測量參數為前置放大器的通道帶寬、放大能力和陷波特性。經測試,測試信號在1~1 kHz的頻帶帶寬內放大增益基本穩定在12.1 dB,即其通道帶寬能≥1 kHz;在頻率為20 Hz和50 Hz時,放大器對40~800 mV信號的放大能力增益并無明顯變化,基本穩定在11.7~13.1 dB;同時,陷波器在對50 Hz信號濾波時能將放大增益控制到0.5 dB以下。因此,基于心電信號的特點所設計的采集調理模塊能穩定地獲得人體的心電信號。

4.2 信號顯示模塊

圖5是采集后的心電信號通過本地的LCD面板實時顯示。從顯示結果看,心電信號的PQRST五個特征點明顯,波形平滑,并且在實際測量中穩定無干擾,能真實反映出采集后的心電信號。

4.3 網絡傳輸模塊

在設計中,網絡接口功能的實現使采集到的心電信號通過以太網發送到遠程PC端,實現數據的遠程傳輸。根據TCP/IP協議與HTTP協議,信號經過打包處理后發送到網絡上。在遠程PC端,通過網頁瀏覽器就可以觀看到服務器端采集到的心電波形。圖6是心電信號在遠程PC端的網頁瀏覽器上顯示結果。該測試結果顯示其與本地的LCD面板顯示波形基本一致,實現了遠程傳輸功能。

實驗表明,該心電監護系統能實時準確的實現數據的采集、顯示、存儲和傳輸功能。

5 結 語

本文描述了一種基于NiosⅡ軟核處理器的遠程心電醫療信號監測系統的設計,該設計已完成了系統平臺的搭建,并通過了EDA軟件仿真驗證和在DE2開發板上板級驗證,能夠實現對心電信號的采集調理、信號波形和數據的LCD顯示、數據的存儲、網絡傳輸。

設計中采用了SOPC技術與IP核復用技術,縮短了系統開發周期,同時使系統具有便攜式、靈活性、功能可擴展等功能。通過移植μClinux操作系統,使系統具有了強大的網絡功能與更加強健的系統穩定性。

責任編輯:gt

-

處理器

+關注

關注

68文章

19160瀏覽量

229115 -

操作系統

+關注

關注

37文章

6737瀏覽量

123190 -

監測系統

+關注

關注

8文章

2675瀏覽量

81254

發布評論請先 登錄

相關推薦

基于Nios II軟核處理器的多生理參數測量系統的總體設計

一種基于NiosⅡ軟核處理器的遠程心電醫療信號監測系統設計

基于NiosⅡ軟核處理器的SOPC技術來實現數碼相框的設計

Nios軟核在CT機掃描系統控制器設計中的應用

液晶顯示屏設計方案:基于Nios嵌入式軟核處理器

基于NiosⅡ軟核處理器和μClinux設計遠程心電醫療信號監測系統

基于NiosⅡ軟核處理器和μClinux設計遠程心電醫療信號監測系統

評論