1.PLIC中斷處理

2.sifive中斷的編程模型

3.關于eclic

4.關于jalmnxti

1.PLIC中斷處理

在RISC V體系架構中,對中斷有著一些定義,下面來分析一下這種定義的實現策略。

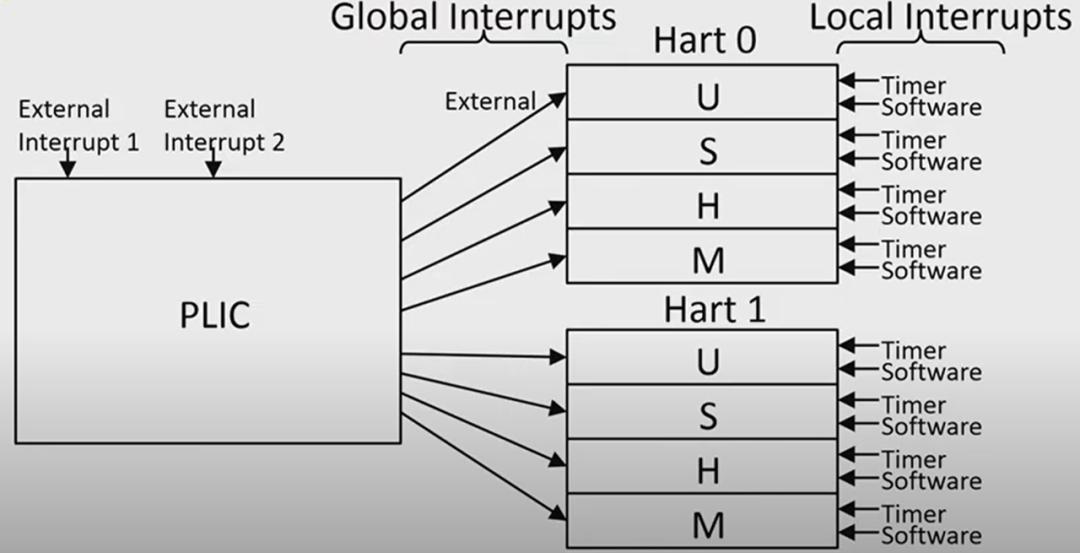

在riscv中一共定義了三種狀態中斷,對于hart層面,hart包含local中斷源和global中斷源。而local中斷只有Timer和Software中斷兩種,而global中斷則稱為external interrupts。只有global中斷源可以被PLIC core響應,通常為I/O device。

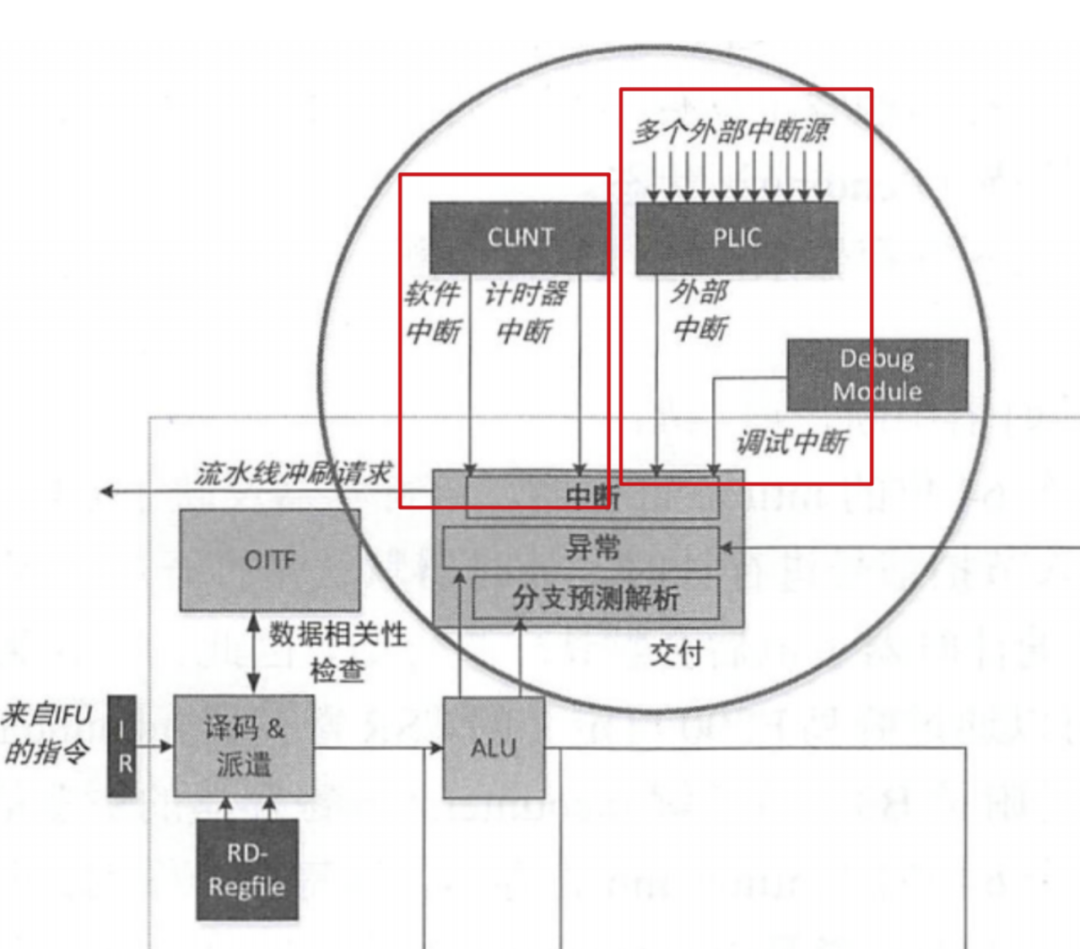

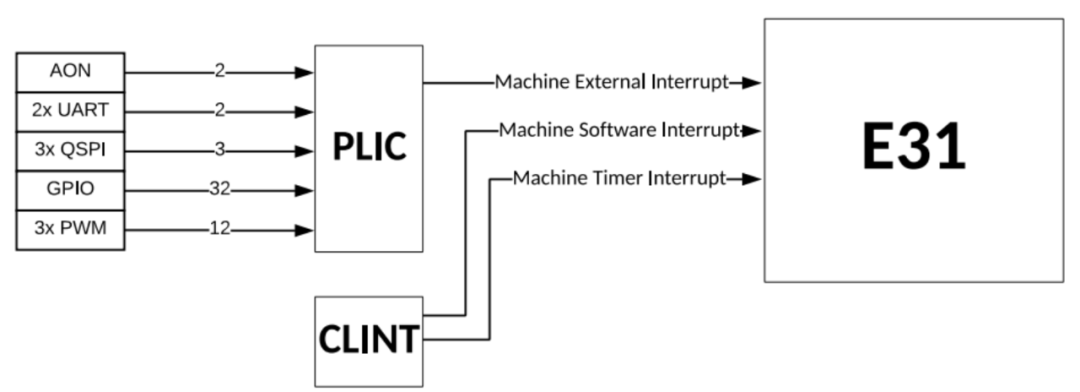

一般來說,timer和software是通過CLINT(CORE LOCAL INTERRUPT),而外部中斷通過PLIC處理。

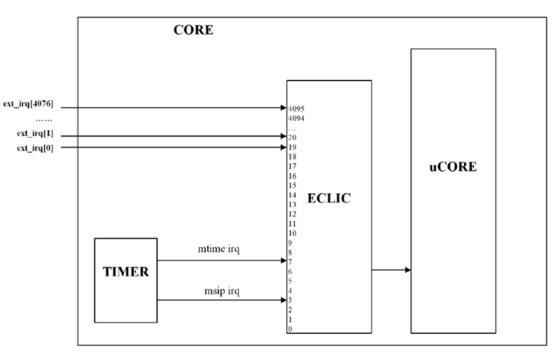

可以看一下蜂鳥處理器的處理流程,另外sifive的E31的中斷也有如下的處理。

2.sifive中斷的編程模型

中斷處理過程有如下的流程

首先mstatus的MIE域被拷貝到mstatus的MPIE,然后mstatus的MIE域被清除。此時全局中斷disable。

程序當前的pc值被拷貝到mepc寄存器中,然后pc值會根據mtvec的值設置其值。如果向量中斷被使能,pc值會變成mtvec.BASE+4xexception處的代碼。

從mstatus.MPP中取出特權模式的狀態

接下來就是處理中斷具體的函數實現

將特權模式的狀態設置到mstatus.MPP

將mstatus.MPIE的數據拷貝到mstatus.MIE中

從mepc中取值放到pc中

最后執行eret恢復到程序正常運行的狀態。

對于CLINT來說,有Software Interrupt和Timer Interrupt,可以直接在寄存器中控制。

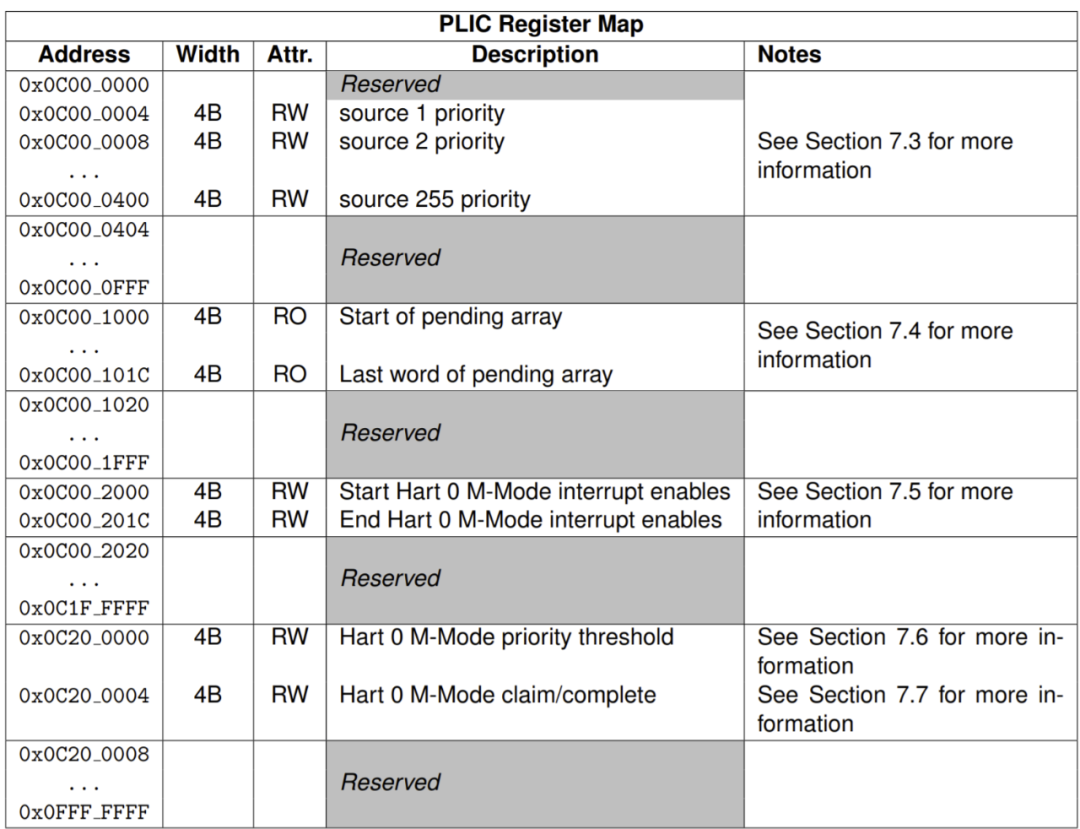

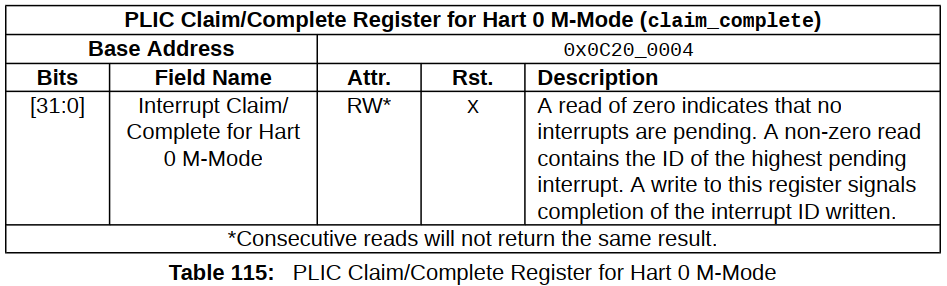

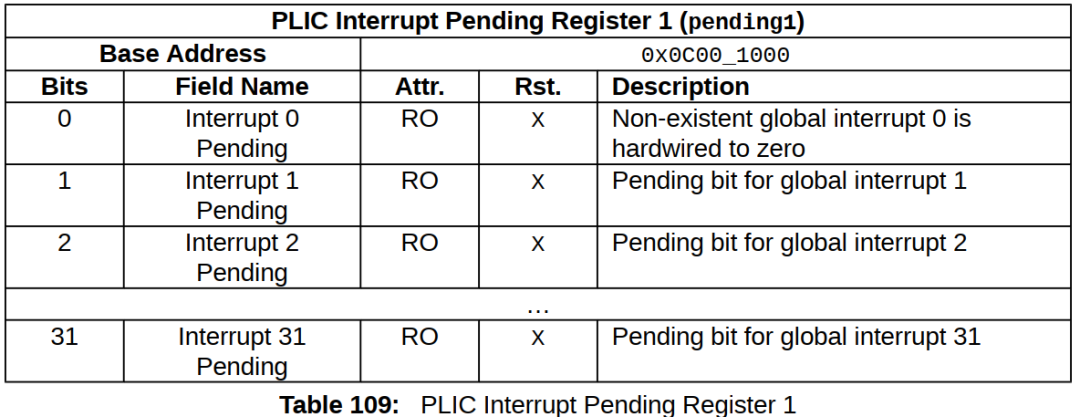

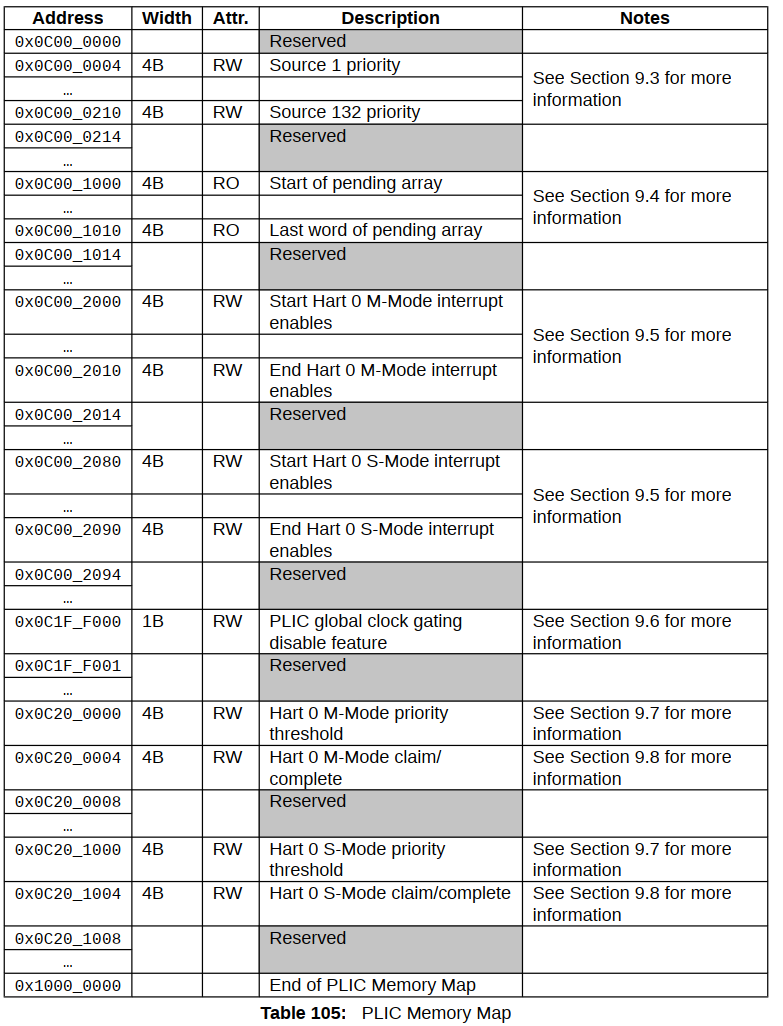

而PLIC實際上可以理解為arm的中斷控制器,存在其map地址。

由于PLIC的使用是針對外部中斷的,所以可以單獨設置每個中斷。可以設置如下的值:

中斷的優先級priotity

中斷掛起位pending

中斷使能enables

中斷閾值priority Thresholds

由于PLIC的實現是獨立于hart的IP設計,所以其設計和布局也不一定完全一致。

3.關于eclic

eclic的設計是芯來科技設計的一種中斷處理方式。

eclic目前也是眾多芯來科技core采用的中斷控制器,也包括gd32vf103系列的芯片。

3號中斷是內核TIMER單元生成的軟件中斷。

7號中斷是內核TIMER單元生成的計時器中斷。

而從19~4095中斷號都是外部中斷,其中斷的編號與中斷的優先級其實沒有關系。

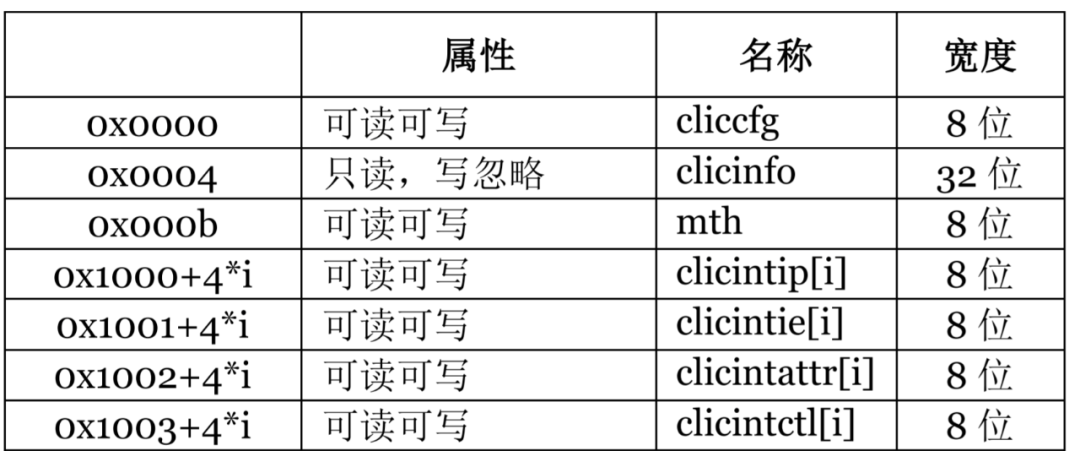

而對于ECLIC的寄存器布局,可見上圖。

cliccfg是中斷全局配置寄存器,可以結合clicintctl[i]配置

clicinfo也是全局寄存器中的數據,對于使用上來說,是只讀的

mth中斷的閾值級別寄存器

clicintip[i]是中斷等待寄存器,也相當于pending寄存器

clicintie[i]為中斷使能寄存器

clicintattr[i]為中斷的屬性,可以設置中斷的上升沿觸發或者下降沿觸發,同時也可以設置中斷從處理是向量中斷還是非向量中斷。

clicintctl[i] 設置中斷優先級級別和優先級,需要配合cliccfg設置閾。

4.關于jalmnxti

這個也是eclic為了減少中斷延時,加速中斷咬尾的自定義指令。

該指令是配合eclic處理機制設計的,其指令功能比較多

開啟中斷使能,處理下一個中斷

返回下一個中斷入口地址

跳轉至中斷handler

中斷處理后返回

由于csrrw ra, CSR_JALMNXTI, ra一條指令可以達到JAL(Jump and Link)的效果,同時硬件上更新Link寄存器作為該指令的PC作為函數調用的返回值,因此從中斷服務程序返回后,又會重新回到csrrw ra, CSR_JALMNXTI, ra指令再次執行,可以重新判斷是否有中斷pending,如果有則跳轉到中斷處理函數,從而實現中斷的咬尾處理,如果沒有中斷等待,則jalmnxti實際上并不會做任何事情。

原文標題:淺析riscv中的plic與eclic

文章出處:【微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

模型

+關注

關注

1文章

3032瀏覽量

48366

原文標題:淺析riscv中的plic與eclic

文章出處:【微信號:Embeded_IoT,微信公眾號:嵌入式IoT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RISCV soft JTAG調試_v1.2

RISCV soft JTAG調試_v1.1

stm32中斷怎么處理的

MCU中斷處理過程,MCU如何處理中斷?

MCU如何處理中斷?中斷處理過程包括哪些步驟?

什么是中斷響應次序?什么是中斷處理次序?

ARM9中斷中(C語言)如何實現復位功能,而不是返回中斷前的狀態?

ARM中的異常中斷是如何實現進入中斷程序的?如何進入呢?

arm處理器有哪些中斷源?arm處理器對異常中斷的響應過程

PLC中斷功能詳解

riscv中的plic中斷處理與eclic詳解

riscv中的plic中斷處理與eclic詳解

評論