關于HDL和行為語句:《一》

1. Verilog HDL和VHDL中,HDL的英文解釋(縮寫拼詞)是:

Verilog HDL(Verilog Hardware Description Language),這里的D是描述Description的首字母。

VHDL(Very High-Speed Integrate Circuit Hardware Description Language),這里的D也是描述的首字母。

也就是說,HDL的D,是描述的意義。HDL也就是硬件描述語言。

2. 為了支持Soc的驗證,支持數模混合,新的System Verilog加入了HVL(Hardware Verification Language),即硬件驗證語言。

3. 合并之前的硬件描述語言功能,稱為HDVL(Hardware Description and Verification Language)

4. 之后EDA,還可能將Design for X的更多功能引入語句,為了不至于在增加縮寫詞的長度,現代的EDA文獻會議中,稱HDL為(Hardware Design Language),即硬件設計語言。這就涵蓋了 EDA語言之后的各種DFx功能。

關于HDL和行為語句:《二》

1. 行為語句Behaviour Statements,是EDA的一次飛躍。它描述電路的外在行為,而不必描述電路的動作細節。

2. 電路的動作和實現細節,交給EDA自動完成,從而解放了設計者。

3. 因此,國外教程解釋,行為語句描述電路“What do”,而不需要描述“How to do”。

4. Verilog對行為語句的描述有特定的要求:

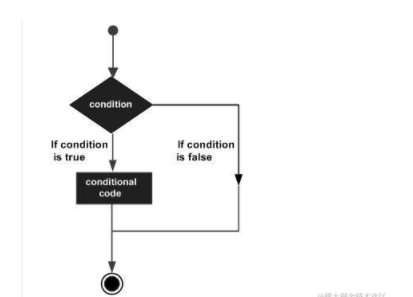

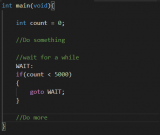

《1》。 行為語句必須放置在一個特定的語法架構中,EDA才對其進行處理(識別為需要綜合的行為);這個特定語法架構,稱為行為體(Behaviour Body)

《2》。 Verilog語法提供兩個行為體,一個是循環行為體(Cycle-Behaviour body);一個是初始化行為體(Initial -Behaviour body)

《3》。 我們知道并常使用的always語句塊,就是循環行為體。Verilog的行為語句,只有放置在它的beginj-end塊之中,才能夠被EDA識別。

5. Verilog的行為語句另一個要素是:行為語句驅動的信號,必須聲明為reg。這里的reg是一個EDA工具的一個軟件對象,并不一定是真的會綜合為Register。

6. Verilog行為語句的第三個要素是:非綜合目的描述時,需要信號敏感表支持,非綜合目的時,循環行為體將在電腦中執行算法,僅僅當信號敏感表中列出的信號發生變更時,非綜合目的的軟件才執行一次該行為體,從而減輕CPU開銷。

7. 但Verilog的信號敏感表,有時也與綜合有關(VHDL與綜合無關)。即信號敏感表中若有而且有一個沿敏感信號,在循環體中未被引用,則Verilog將為之綜合一個寄存器,用這個寄存器捕獲行為體中的所有輸出信號,并用唯一未被引用的沿敏感信號作為時鐘。

一定要實際做一遍,才能得到體驗。所以再次引用林彪的那句話:

“理解的要執行”

“暫時不理解的也要執行”

“在執行中加深理解”

加油,各位!

原文標題:關于HDL和行為語句

文章出處:【微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

HDL

+關注

關注

8文章

327瀏覽量

47344

原文標題:關于HDL和行為語句

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

LTspice的編程語句應該怎么寫?

行為分析智能監測攝像機

有什么好用的verilog HDL編輯工具可用?

鴻蒙TypeScript入門學習第6天:【條件語句】

assign語句和always語句的用法

verilog中initial和always的區別

#2024,立Flag了嘛? #學習spinal HDL還需要學習對應的Scala語言

深入探討嵌入式C編程的goto語句

關于HDL和行為語句詳解學習

關于HDL和行為語句詳解學習

評論