近年來,整個電子行業似乎都為RISC-V感到瘋狂。但什么是RISC-V?您將能如何參與其中?如果您曾經閱讀過相關資料,您會知道它是一種處理器,并且目前市場上已經有相關芯片可以使用。您可能還知道它是“自由和開放的”,主要是因為它令人興奮并擁有龐大的粉絲群。 讓我們撥開迷霧,找出這項技術的真正意義所在。

首先,我們必須弄清楚,RISC-V是一種指令集體系結構或ISA ,而不是處理器。這意味著,如果您選擇基于RISC-V ISA,則RISC-V背后的社區已經對處理器設計的工作方式進行了描述。當我們說“設計”時,實際上是指創建具有所有寄存器,累加器,數學運算,存儲器總線以及其他所有部件的處理器。

ISA記錄了受支持的操作,內存尋址功能,堆棧的功能以及發生中斷時的情況,僅舉幾例。關于支持的操作,它說明了使用多少位對指令進行編碼以及使用哪些位對所需的任何操作數的源進行編碼。

RISC V讓人興奮的原因在于其ISA是免費開放的。開放意味著任何人都可以為它的發展做出貢獻,而自由意味著它不需要花錢就可以使用。 但是,就像Arduino電路板設計是開放和免費使用的一樣,這并不意味著不需要花錢就可以買到一塊電路板,并且同樣適用于構建基于RISC-V的理想設計。

RISC-V在競爭什么?

每個處理器都有一個ISA;幾乎所有專利都是專有的,而其實有些是可許可授權使用 的。Microchip生產的器件使用8位和16位PIC處理器,并且在某處有一個ISA來描述它們。這些是專有的內核,屬于Microchip并在其微控制器中出售。 如果您想構建自己的微控制器,則可能要看一下Arm和MIPS。這些專有核心可作為知識產權(IP)許可。他們背后的企業將把ISA轉換為良好的處理器設計,開發支持它們的工具,創建其他相關基礎結構并向您收取使用費。但這些ISA面臨的挑戰是這些選項不能完全滿足您的期望。

您的新應用可能需要非常快地執行一項任務(例如加密),但功耗卻很小。潛在的可許可處理器IP可能以100條指令執行您的任務。如果現在希望降低功耗,則需要找到專門用于低功耗的硅制造設施(fab),這可能比“通用”制造工藝昂貴,從而導致您難以置信的產品對于您的目標市場而言過于昂貴。

但是,您可能會有一些聰明的工程師,可以通過為處理器創建新指令來優化代碼的執行時間,但是由于ISA是專有的,因此您不允許對其進行修改。因此,您陷入了需要用制造方法解決的處理器性能問題。稍后對此進行更多討論。

開箱即用的RISC-V

RISC-V的出現,基本解決了上述問題。當前,他們定義了32位和64位ISA,并且也正在使用128位ISA。這些基本定義被命名為RV32I和RV64I。如果選擇RV32I,將有49條指令供您使用。順便說一句,“ I”代表“整數”。其中包括所有基本的整數算術和邏輯指令(ADD,SUB,AND,OR,XOR),移位,比較,跳轉和鏈接,以及一些系統指令。如果您希望支持緊湊代碼,則可能對“ C”選項感興趣。這提供了16位指令編碼,類似于Arm Thumb模式。也可以添加乘法和除法(M),原子(A)和浮點(F,D和Q)指令。

下一步是根據硬件描述語言[(HDL)(例如VHDL或Verilog)中所選選項的規范來設計處理器內核。由于這并不容易,所以這就是社區所關注的方面。設計處理器需要很多技巧,因此有很多人和企業為您提供現成的設計。如果您想走“免費”路線,由ETH Zurich和Bologna大學創建。他們的CV32E40P RV32IM C實現可在GitHub 上找到,如果您想了解如何實現這種的方法,指令解碼器也在其上。另一個實現是BOOM項目,這是由加利福尼亞大學伯克利分校開發的高性能且可參數化的體系結構研究核心。

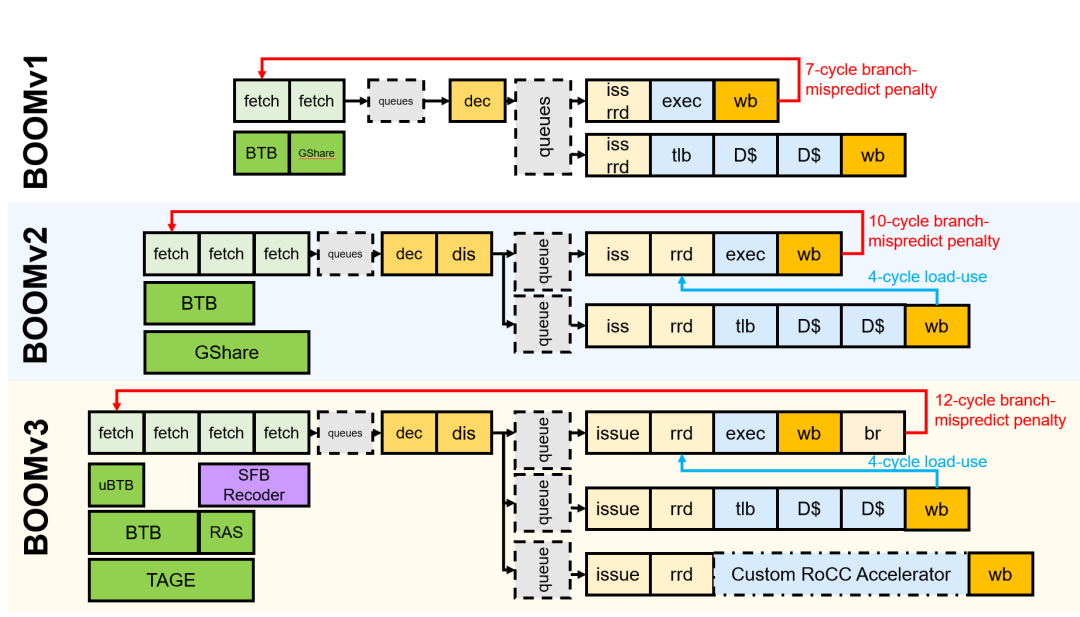

圖1:使用RISC-V實現的BOOM項目開發過程。(來源:加利福尼亞大學)

如果您急于需要一些支持,那么您將需要花一些錢,并從SiFive 之類的企業處獲得實現的許可。它們具有可用的32位和64位設計,你們也可以對其進行定制。

如何試用RISC-V?

盡管RISC-V已經存在了一段時間,但沒有太多可供我們測試的芯片。在行業背景下,RISC-V還是相對較新的。如果您熱衷于微控制器,那么您將了解整個行業中大多數人是如何采用Arm的,而不再使用其專有的內核。那是一項戰略性的長期投資。現在轉向RISC-V只會節省支付給Arm的特許權使用費,并且不會給用戶帶來什么好處。他們還需要使他們的開發團隊在RISC-V上達到最新,將其與所有其他IP(模擬,計時器,總線,接口,內存)集成,更新開發IDE,編譯器,調試器等。

如果您擁有Seagate或Western Digital硬盤驅動器,則可能已經在“使用” RISC-V 。但是您實際上是想在此內核上運行代碼,而不僅僅是擁有使用它的產品。最快的方法是使用模擬器,例如ESEO提供的emulsiV ,該模擬器使用其RISC-V核心實現“ Virgule”(圖2)。

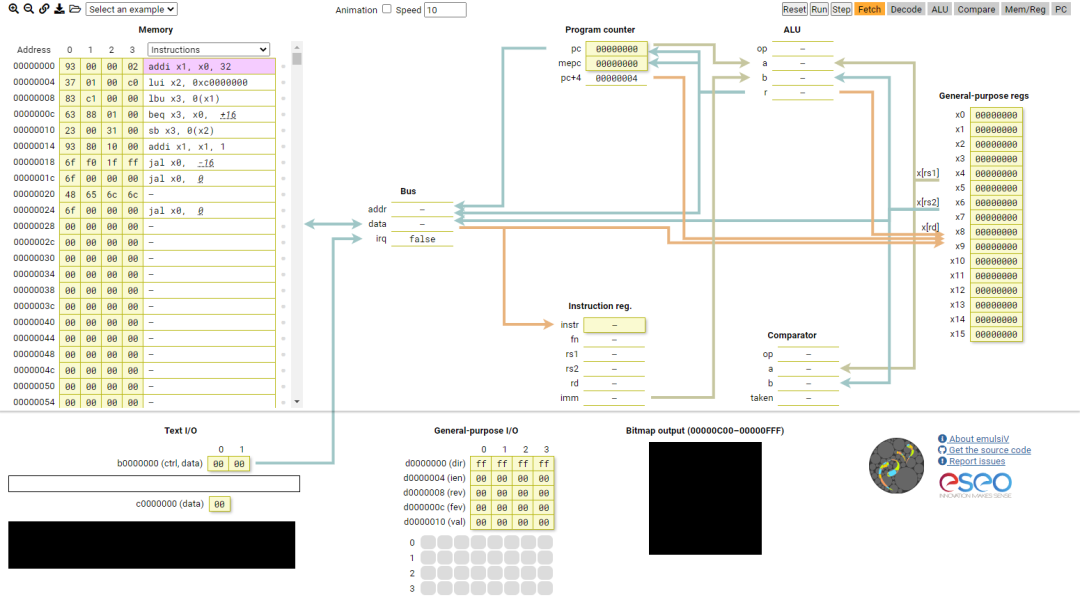

圖2:使用emulsiV模擬器,任何人都可以在其Web瀏覽器中試用RISC-V。

除了處理器之外,模擬器還提供一些指令輸入/輸出,位圖輸出和一些通用I / O(GPIO)。七個示例涵蓋了基礎知識,從添加和輸出ASCII文本到控制GPIO。“ animation”(動畫)選項(復選框的頂部中間)是一個不錯的選擇,它顯示了所有數據的來源以及代碼執行時的去向。 如果愿意,你可以嘗試將清單1中的代碼復制到文本編輯器中,然后將文件另存為program.hex,然后將其上傳到模擬器中。

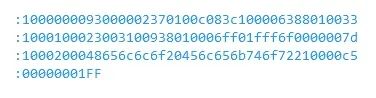

清單1:用于emulsiV模擬器的原始HEX代碼,將其保存并上傳為program.hex。 如果您想以Arduino格式體驗RISC-V,則可通過CrowdSupply 獲得HiFive1 RevB 。它使用SiFive FE310-G002微控制器。這是一款僅具有數字外設(I 2 C,UART,SPI,PWM,GPIO)和某些SRAM的準系統設備,依靠片外QSPI閃存實現非易失性存儲。該評估板包括Wi-Fi和藍牙模塊以及用于USB調試的Segger J-Link。

性能范圍的另一端是Microchip PolarFire SoC 它將四個64位RISC-V內核與一個FPGA一起放置。這提供了一個高度可配置的平臺,該平臺可以運行Linux,同時支持硬實時應用程序。

如何自定義我的RISC-V?

之前,我們提到RISC-V的實際好處是您可以調整指令集以滿足個別應用的需求。這意味著,如果找到的處理器能滿足95%的需求,那么則可以添加一些漂亮的額外功能來實現剩余的5%。假設您的應用大量使用ChaCha 流密碼,如Imperas的應用筆記中所述,Imperas是另一種提供驗證,分析和性能分析工具的RISC-V播放器。

您已經在RISC-V內核上運行了ChaCha實現,并且注意到它正在消耗大量的處理時間。您不僅希望縮短執行時間,而且還希望受益于由于執行時間減少而帶來的功耗下降,也許可以使用它進入低功耗睡眠模式。

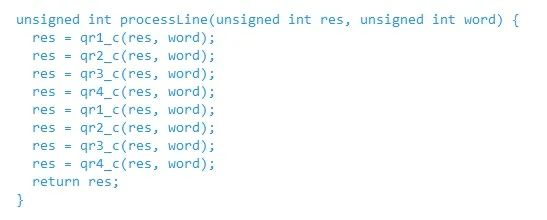

清單2:實現ChaCha流密碼的C代碼。

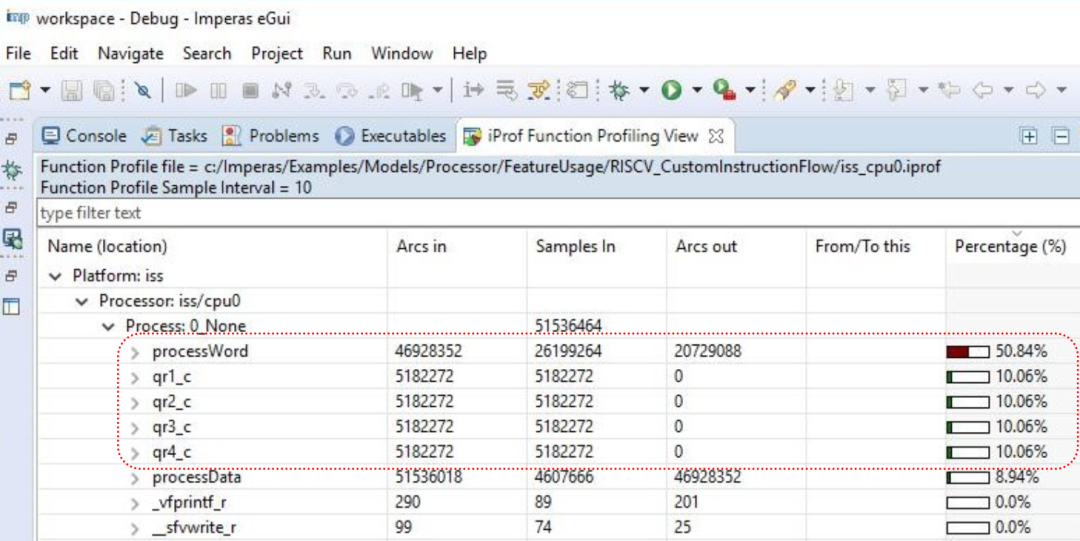

代碼(清單2)在稱為“quarter rounds”的步驟中廣泛使用XOR和旋轉指令,為此已編寫了四個C qrX_c()函數。甲ProcessLine從()函數調用這四個函數來執行加密。對執行時間的分析表明,處理器在此任務上花費了大約55%的時間,其中大約32%的時間分布在quarter-round功能中(圖3)。

圖3:使用標準C編譯的代碼,ChaCha密碼流需要大約55%的處理器時間(來源:Imperas Software Limited)

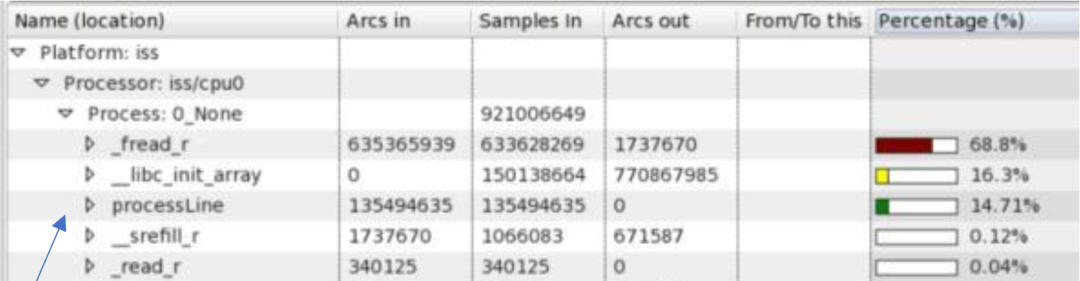

使用RISC-V,我們可以簡單地實現四個專用的quarter-round指令,這些指令在一個周期內執行,而不必依賴C編譯器強制生成的代碼。這是因為ISA中保留了一部分,用于自定義說明。 最初,我們可以將指令添加到RISC-V設計中,并用C編寫該指令的實現。這可以模擬新指令以測試其功能,并檢查性能是否可以提高。在這種情況下,借助定制的RISC-V內核上可用的專用quarter-round指令,processLine()函數所需的可用處理器性能不到15%(圖4)。)。如果這被認為是成功的,則開發團隊可以在Verilog中開發指令的硬件實現。

圖4:通過使用專用的,新開發的指令,ChaCha密碼流處理器的負載下降到不足15%。(來源:Imperas軟件有限公司)

遺憾的是,使用新指令并不像重新編譯C代碼那樣容易(清單3)。修改RISC-V編譯器以利用新指令是一項巨大的工作。取而代之的是,使用內聯匯編器以與手工優化代碼相同的方式調用十六進制編碼的指令。

清單3:使用新的RISC-V指令。

我該如何對此貢獻?

如果您有興趣幫助RISC-V的持續開發,那么您很幸運!RISC-V International 是負責開發和推廣RISC-V的所有事物的值得信賴的組織(圖5)。個人可以作為社區成員加入,或者,如果您想在此基礎上發展職業,那么有很多企業和大學都在積極參與其中。

如果您期望各種各樣的RISC-V微控制器進入市場,您可能會感到失望。GigaDevice提供了一些設備,還有俄羅斯供應商針對智能電表市場提供的另一種設備。但是,他們表現欠佳。因為Arm對大型企業根深蒂固,即使沒有處理器使用費的加工商的財務利益,初創企業也將難以在這個飽和的市場中競爭。

取而代之的是,我們更有可能看到RISC-V用于專門的應用,在這些應用中,定制內核的能力帶來了巨大的好處,例如超低功耗。 RISC-V面臨著有關向中國授予技術許可的問題,它正在證明是從美國獲取IP企業的一種流行替代方案。阿里巴巴宣布以16納米制程制造的16核,2 GHz,64位RISC-V ,并表示正在考慮將該核用于服務器基礎架構。最后,歐洲處理器倡議一直在研究異構架構,這些架構可以同時看到Arm和RISC-V(或其他內核)。這里的目的是通過為多核設計中的每個計算難題使用最佳處理器來獲得兩全其美的效果。

RISC-V并不是首次免費開放嘗試使用處理器IP,但是迄今為止,它是最成功的嘗試。憑借其悠久的歷史,靈活性,開放的態度,學術界的興趣以及廣泛的行業支持,這項技術將在整個職業生涯中陪伴一代或更多的工程師。

參考鏈接:https://mp.weixin.qq.com/s/FyuH51mYp50MXLAUZ7NGmA

編輯:jq

-

ARM

+關注

關注

134文章

9054瀏覽量

366830 -

函數

+關注

關注

3文章

4307瀏覽量

62433 -

C代碼

+關注

關注

1文章

89瀏覽量

14287 -

RISC-V

+關注

關注

44文章

2230瀏覽量

46036

原文標題:電子行業為什么都為RISC-V感到瘋狂?

文章出處:【微信號:TopStorage,微信公眾號:存儲加速器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

RISC-V,即將進入應用的爆發期

加入全球 RISC-V Advocate 行列,共筑 RISC-V 的未來 !

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

risc-v的發展歷史

rIsc-v的缺的是什么?

RISC-V為何如此重要?

RISC-V有哪些優點和缺點

解鎖RISC-V技術力量丨曹英杰:RISC-V與大模型探索

什么是RISC-V?RISC-V的關鍵技術

玄鐵RISC-V生態大會深圳召開,達摩院引領RISC-V創新應用

揭秘電子行業為什么都為RISC-V感到瘋狂?

揭秘電子行業為什么都為RISC-V感到瘋狂?

評論