四、射頻走線與地

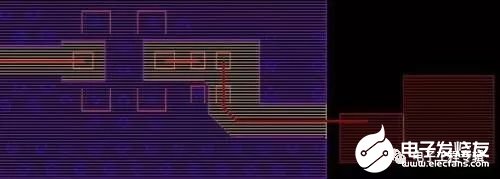

舉個例子來說吧。我們將對多層電路板進行射頻線仿真,為了更好的做出對比,將仿真的PCB分為表層鋪地前的和鋪地后的兩塊板分別進行仿真對比;表層未鋪地的PCB文件如下圖1所示(兩種線寬):

圖1a:線寬0.1016 mm的射頻線(表層鋪地前)

圖1b:線寬0.35 mm的射頻線(表層鋪地前)

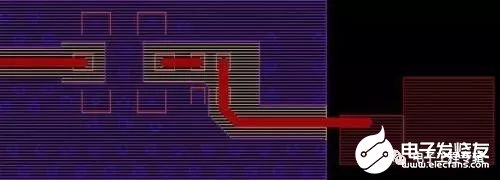

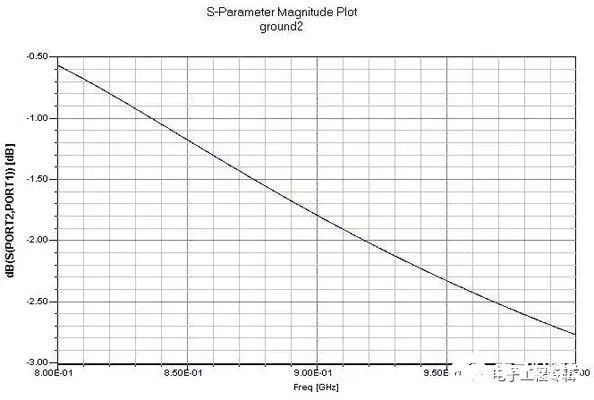

首先將線寬不同的兩塊板(表層鋪地前)由ALLEGRO導(dǎo)入SIWAVE,在目標線上加入50Ω端口。針對不同線寬0.1016mm和0.35mm, 我們的仿真結(jié)果如圖2所示,圖中顯示的曲線是S21,仿真頻率范圍為800MHz-1GHz。

圖2a:表層未鋪地的S21 (線寬0.1016mm)

圖2b:表層未鋪地的S21 (線寬0.35mm)

由圖中可以看到,在800MHz-1GHz的范圍內(nèi),仿真的數(shù)據(jù)展示為小數(shù)點后一到兩位的數(shù)量級,0.35mm的損耗要比0.1016mm的線小一個數(shù)量 級,這是因為0.35mm的線寬在該板的層疊條件下其特征阻抗接近50Ω。因此間接驗證了我們所做的阻抗計算(用線寬約束)是有一定作用的。

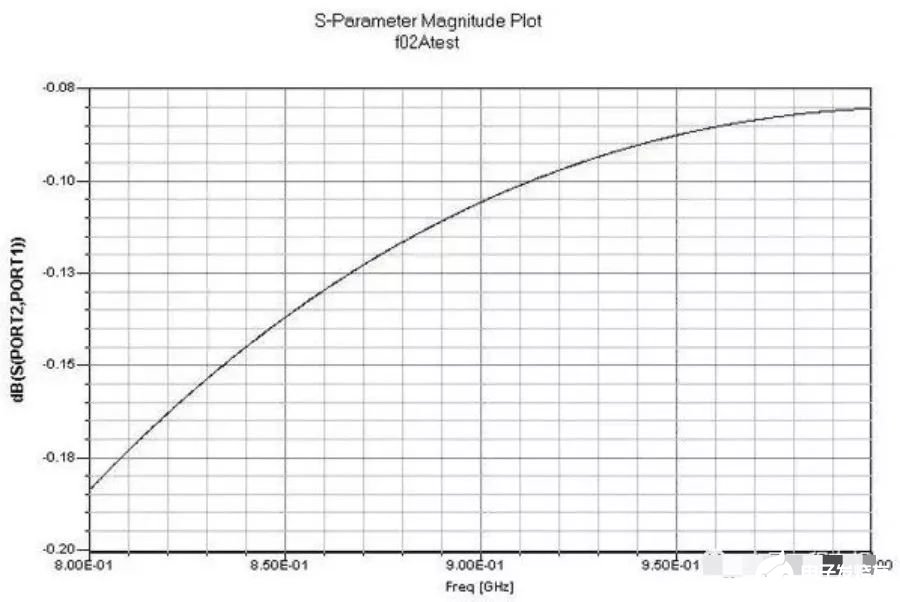

接下來我們做了表層鋪地后的同樣的仿真(800MHz-1GHz),導(dǎo)入的PCB文件如下圖。

圖3a:0.1016 mm的射頻線(表層鋪地)

圖3b:0.35 mm的射頻線(表層鋪地)

圖3:表層鋪過地后的PCB

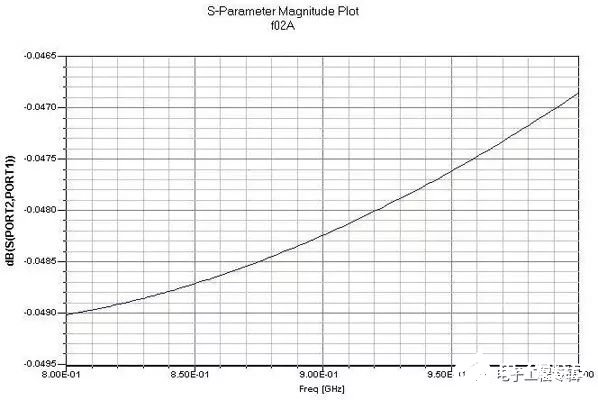

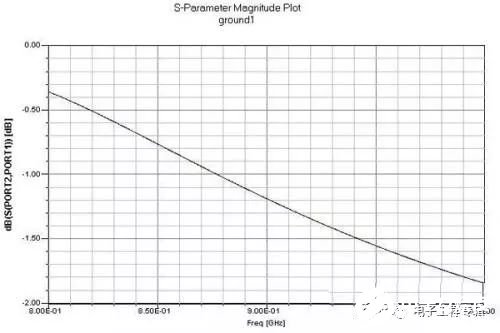

仿真結(jié)果如下圖:

圖4a:表層鋪地后的S21 (0.1016mm)

圖4b:表層鋪地后的S21 (0.35mm)圖4:表層鋪過地后的S21

由圖中看到,仿真的數(shù)據(jù)顯示,該傳輸線的線損已經(jīng)是1-2 dB的數(shù)量級了,當然0.35 mm的損耗要明顯小于0.1016 mm的。另外一個明顯的現(xiàn)象是相對于未鋪地的仿真結(jié)果,隨著頻率由800MHz到1GHz的增加,損耗趨大。我們可以從仿真的結(jié)果中得到這樣一個結(jié)果:

1.射頻走線最好按50歐姆走,可以減小線損;

2.表層的鋪地事實上是將一部分RF信號能量耦合到了地上,造成了一定的損耗。因此PCB表層的鋪地應(yīng)該有所講究。盡量遠離RF線。工程經(jīng)驗是大于1.5倍的線寬。

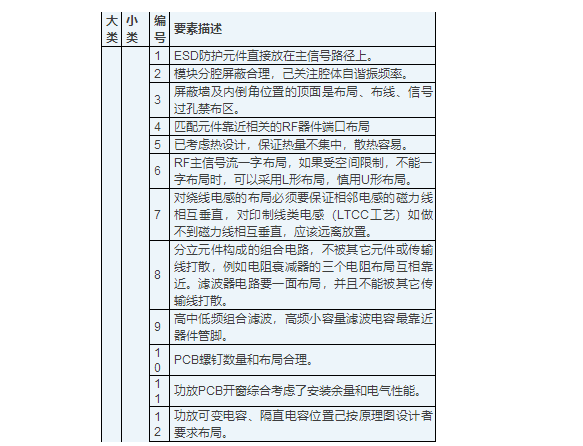

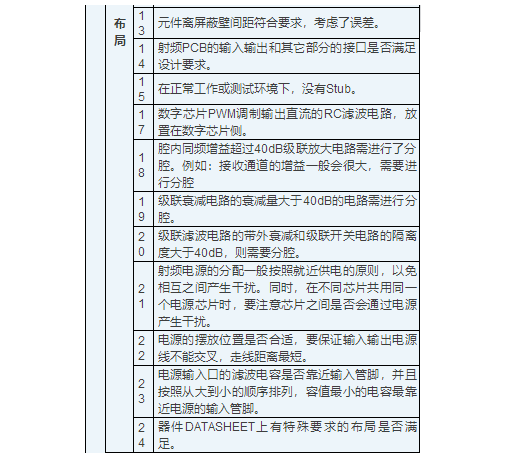

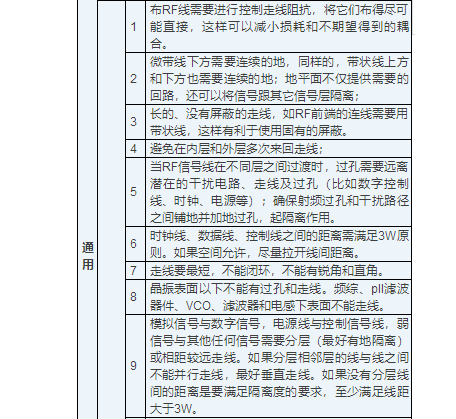

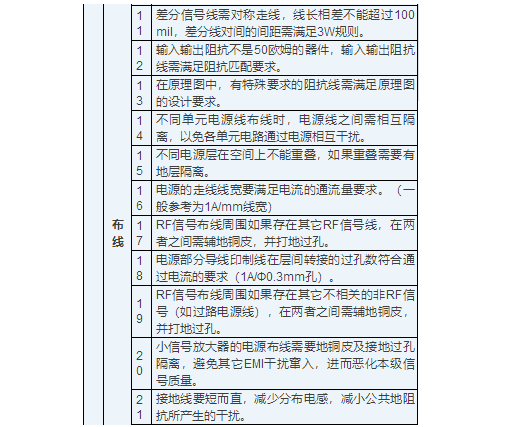

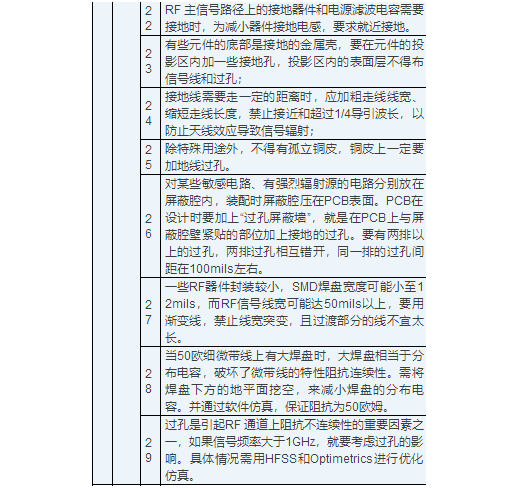

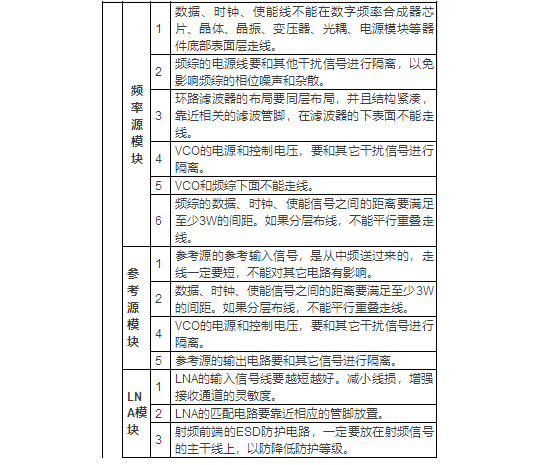

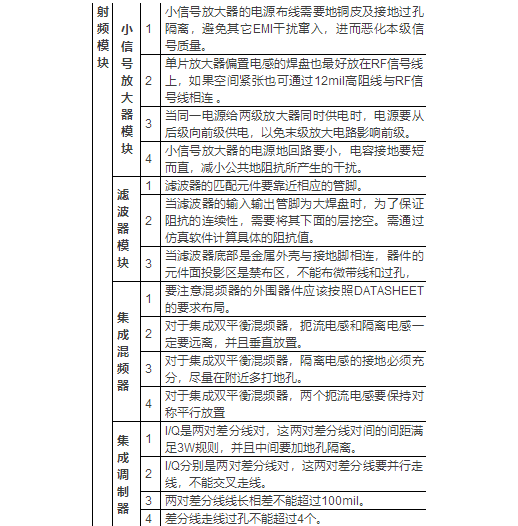

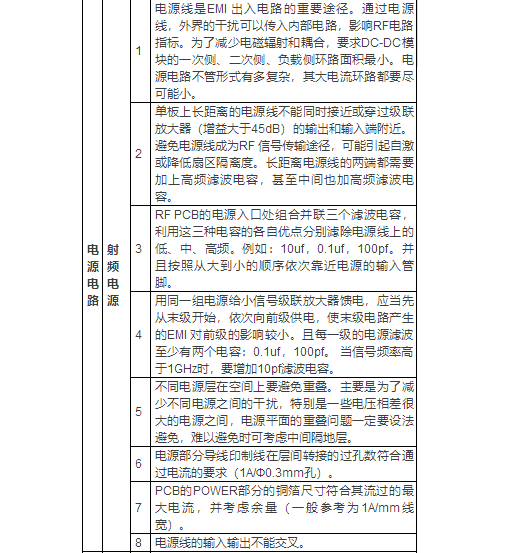

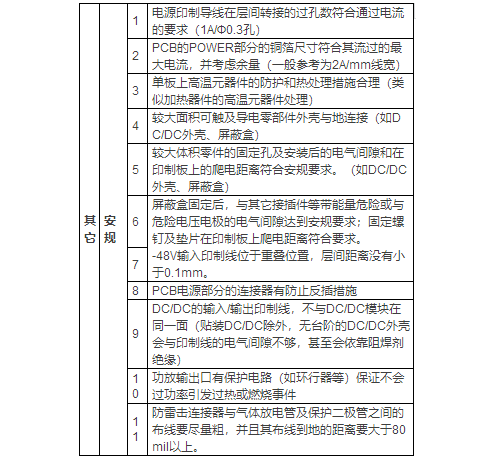

【5】設(shè)計checklist

編輯:jq

-

pcb

+關(guān)注

關(guān)注

4318文章

23022瀏覽量

396424 -

射頻

+關(guān)注

關(guān)注

104文章

5551瀏覽量

167582 -

電路板

+關(guān)注

關(guān)注

140文章

4911瀏覽量

97456

發(fā)布評論請先 登錄

相關(guān)推薦

電路小知識 | 電源選型要點、電路圖的解讀方法、LED及其應(yīng)用示例

PIN二極管在射頻電路中的應(yīng)用

pcb設(shè)計中布局的要點是什么

PCB電路板設(shè)計與制作的步驟和要點

網(wǎng)分射頻線纜的各項指標解讀

矢量網(wǎng)絡(luò)分析儀在射頻電路調(diào)試中的應(yīng)用

PCB射頻電路四大基礎(chǔ)特性及設(shè)計技巧

自舉電路設(shè)計要點有哪些

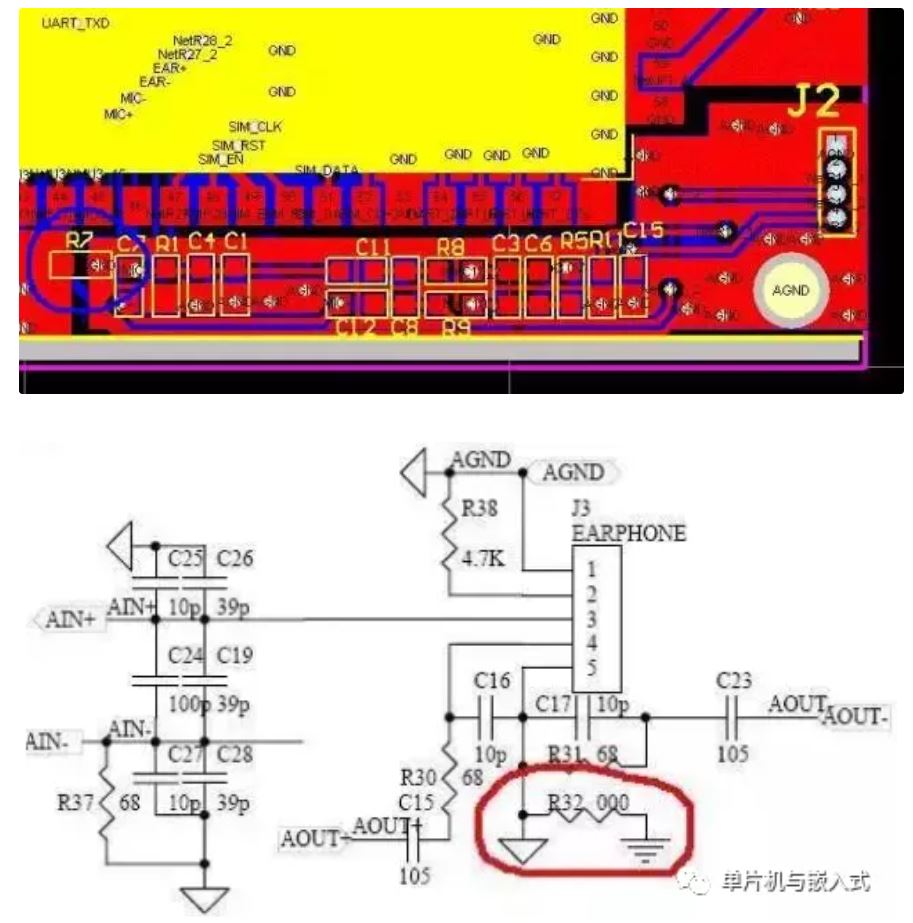

深入研究電路設(shè)計中的“地”之謎:詳解分類與作用應(yīng)用

電路板PCBA里TVS管應(yīng)用選型要點

電路設(shè)計中的“地”

深度解讀射頻電路設(shè)計要點(中)

深度解讀射頻電路設(shè)計要點(中)

評論