作者:張文旭,司錫才,孫強毅

在電子信息領域中,對于接收機的要求是處理的頻帶盡可能寬、動態范圍盡可能大,以便得到更寬的頻率搜索范圍,獲取更多的信息量,并且具有檢測同時到達信號的能力[1]。隨著電子元器件的不斷發展,ADC的采樣速率越來越高,這為接收機實現寬頻帶覆蓋提供了硬件支持,而軟件無線電中基于多相濾波結構的信道化接收又為實現全概率接收提供了理論依據[2]。

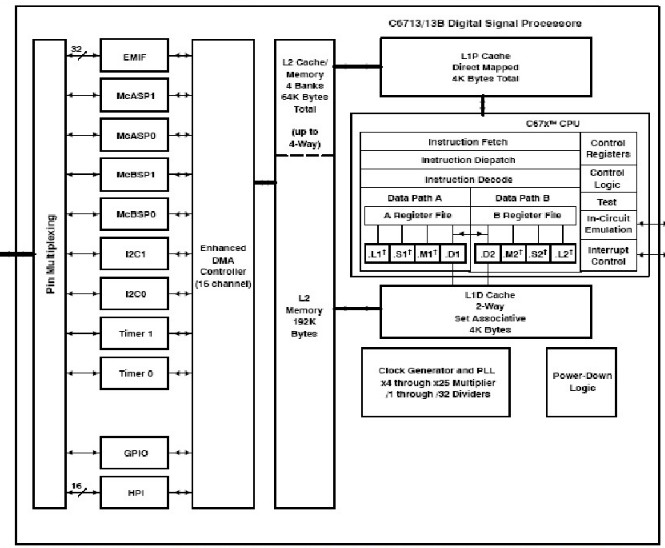

本文介紹一種基于多相濾波結構的高效信道化接收機,該接收機采用了美國國家半導體公司(National Semiconductor)的高速采樣器件ADC08D1000與ALTERA公司的StratixII系列FPGA,可實現瞬時帶寬480MHz的雙通道信道化接收和瞬時帶寬為960MHz的單通道信道化接收。另外,考慮到該信道化接收后續信號處理問題,采用了TI公司的TMS320C6000系列 DSP芯片完成后續信號處理算法。

1 高效信道化接收機結構模型

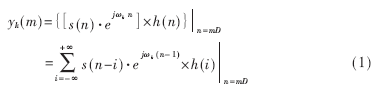

本文設計的信道化接收機結構模型采用多相濾波結構模型。假設輸入信號為s(n),采用低通濾波器沖激響應為h(n),信道數為K,抽取比為D。采用臨界抽取條件,即K=D情況下,可以由低通結構推導出多相濾波結構,即第K路信道的輸出為[3]:

定義:信號D倍抽取后多相結構表達式為sp(m)=s(mD-p),濾波器的多相分量表達式為hp(m)=h(mD+p),用i=iD+p帶入式(1)中,可得:

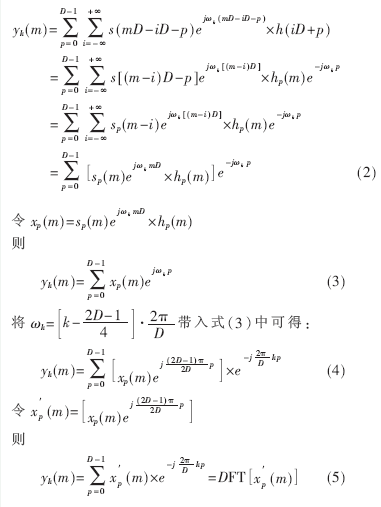

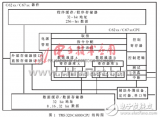

從上述推導和轉換過程即可得到基于多相濾波結構的信道化接收模型,如圖1所示。

從低通濾波結構到多相濾波結構的轉換,可以看出該高效結構中抽取置于混頻之前,可以將高速A/D 轉換后的數據首先進行D倍抽取,然后再混頻、濾波,使得混頻器、濾波器工作速率降了D倍,且后續DFT處理可采用FFT實現,提高了系統的數據處理速度,充分發揮了該結構的高效性。

2 信道化接收機系統實現

2.1 系統硬件設計

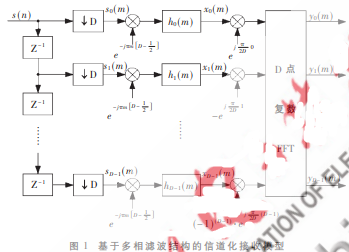

本文設計的高效信道化接收機的硬件原理框圖如圖2所示。由于該設計采用的高速A/D(ADC08D1000)內部集成了雙通道模數轉換功能,采樣速率為 1GHz,所以當芯片工作于交叉采樣模式時,只需將信號接于信號輸入1端,信號輸入2端懸空,即可實現采樣速率為2GHz的采樣。因此該接收機可實現瞬時帶寬為480MHz的雙通道數字信道化接收和瞬時帶寬為960MHz的單通道數字信道化接收。

由于本設計高速A/D輸出數據率在480MHz,因此高速A/D與FPGA接口采用差分信號走線,并且FPGA內部對數據率采取降速處理以便后續處理,解決了高速采樣和后續信號處理之間的瓶頸問題。經過FPGA內部做信道化處理后的信號送入DSP中,可以實現后續相應的信號處理算法。另外,可通過USB接口芯片將所需數據傳給PC機,完成數據的存儲、處理與顯示等。

2.2 均勻濾波器組劃分

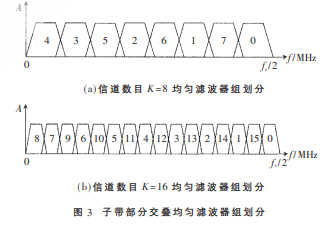

基于多相濾波結構的信道化接收機模型,本系統設計中對于?棕k的選擇按照其實信號多相結構選取為 系統實現的瞬時帶寬為480MHz和960MHz兩種,其各自的信道數目分別為K=8和K=6,各自均勻濾波器組劃分情況如圖3所示。圖3(a)為瞬時帶寬為480MHz,信道數目為K=8時的均勻濾波器組劃分;圖3(b)為瞬時帶寬為960MHz,信道數目為K=16時的均勻濾波器組劃分[5]。兩種情況下均勻濾波器組劃分均采用了子帶部分交疊的劃分形式,過渡帶為5MHz。

系統實現的瞬時帶寬為480MHz和960MHz兩種,其各自的信道數目分別為K=8和K=6,各自均勻濾波器組劃分情況如圖3所示。圖3(a)為瞬時帶寬為480MHz,信道數目為K=8時的均勻濾波器組劃分;圖3(b)為瞬時帶寬為960MHz,信道數目為K=16時的均勻濾波器組劃分[5]。兩種情況下均勻濾波器組劃分均采用了子帶部分交疊的劃分形式,過渡帶為5MHz。

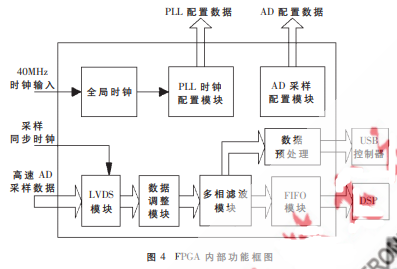

2.3 FPGA內部功能實現

該信道化接收系統FPGA內部功能主要包括系統全局時鐘模塊、PLL時鐘配置模塊、A/D采樣配置模塊、LVDS模塊、數據調整模塊以及FIFO模塊。高速A/D采樣得到的480MHz數據經過FPGA內部自帶的LVDS模塊,將2×16bit數據按照1:4分成2×64bit數據,相當于抽取比D=8,即輸出數據率fout=fs/D=960MHz/8=120MHz,按照臨界抽取條件,信道數目K=D=8,瞬時帶寬為480MHz時,子帶寬度B0=60MHz。實現單通道瞬時帶寬960MHz的信道化結構時,信道數目和抽取比為K=D=16,子帶寬度依然為B0=60MHz。經過LVDS輸出的數據率為120MHz,送入數據調整模塊后進行多相濾波結構的信道化處理,其處理結果通過高速FIFO與DSP完成數據傳輸。具體FPGA內部功能框圖如圖4所示。

3 實驗測試結果

在完成了基于多相濾波結構的信道化接收機設計與調試的基礎上,對該接收系統進行了實際測試。

3.1 對高速A/D數據采集的測試

輸入信號頻率為500MHz,信號形式分別為連續波和脈沖波,A/D采樣速率為2GHz,利用FPGA自帶的SignalTapⅡ嵌入式邏輯分析觀察LVDS模塊調整后的多路信號波形。測試結果如圖5所示。

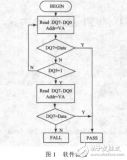

3.2 多相結構信道化測向情況測試

根據FPGA內部多相濾波結構的實現,其后續采用了CORDIC算法來實現瞬時幅度、瞬時相位的提取。實驗中選擇輸入信號為100MHz的連續波信號,瞬時帶寬為480MHz,采樣速率為960MHz,利用DSP讀取高速FIFO中的數據,借助CCS開發環境,將得到的數據以波形顯示,如圖6所示。其中 dsp_reg2為3表示信道3截獲了信號,與圖3(a)信道劃分情況相符;而圖形顯示的是CORDIC算法輸出的瞬時相位曲線。

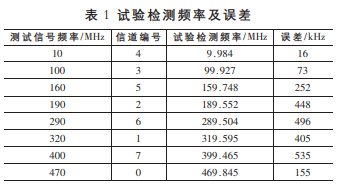

3.3 截獲信號頻率測試情況

輸入8個不同頻率的余弦信號,檢測系統截獲信號的信道編號是否正確以及記錄截獲信號的頻率。對照表1可知,系統輸出的信道編號是正確的。由于信道化系統的采樣時鐘可能存在偏差和抖動,從而導致相位差測頻算法測頻出現偏差,即理論上各個信道中心頻率與實際有一定的偏差,故試驗檢測頻率與測試信號頻率有一些偏差,但是已達性能指標要求。

本文介紹了一種基于多相濾波結構的高效信道化接收機的設計與實現。借助采樣速率1GHz、集成雙通道的高速A/D,該信道化接收機可以實現雙通道瞬時帶寬 480MHz和單通道瞬時帶寬960MHz的寬頻帶覆蓋。利用LVDS模塊實現了高速數據的降速,并在FPGA內部實現了多相濾波結構的數字信道化接收,采用CORDIC算法實現了瞬時幅度和瞬時相位的提取,并通過實際測試驗證了高速數據采集、均勻信道化接收和瞬時相位提取的正確性。該高效結構的信道化接收在FPGA內部實現,具有結構化設計靈活、方便的特點,且利用DSP可以實現后續的相關信號處理算法,適合工程應用。

責任編輯:gt

-

dsp

+關注

關注

552文章

7962瀏覽量

348252 -

芯片

+關注

關注

453文章

50387瀏覽量

421783 -

接收機

+關注

關注

8文章

1179瀏覽量

53407

發布評論請先 登錄

相關推薦

急求TMS320C6000系列DSP的書

基于TMS320C6000的優化策略分享

TMS320C6000 DSP 優化應用報告

TMS320C6000 EMIF到TMS320C6000主機端口接口

基于TMS320C6000系列DSP芯片實現高效信道化接收機的設計

基于TMS320C6000系列DSP芯片實現高效信道化接收機的設計

評論