目前世界上有兩種文明,一種是人類社會組成的的碳基文明,一種是各種芯片組成的硅基文明——因為幾乎所有的芯片都是以單晶硅為原料制作的,芯片系統的總數比人類的數量還多出數十上百倍。芯片大家族里面也分各種不同類型的芯片,從古老的用電子管堆出來的成噸的邏輯門到現在的超級數據中心,電子技術的發展走過了一代又一代,到了今天,各種芯片更是百花齊放,芯片廠商百家爭鳴。

可是,這么多芯片,按照功能分類,有專門用于計算的、有專門用于控制的、有專門用于存儲的……按照集成電路規模分,有超大規模,大規模,和古老的中規模、小規模。而具體到了類型,又有CPU,SoC,DSP……有這么多的芯片,真的區分清除也是要花上一番功夫的,這篇文章就可以帶領大家了解一些基礎的、用來處理數據的集成電路芯片。

在這些專門用于處理數據的芯片中,最常用的就是由微處理器構成的微處理器系統,小到一塊單片機,大到數據中心的幾十路幾十核地表最強處理器,都是由簡單的微處理器系統發展而來,微處理器是應用最廣泛的芯片。首先了解微處理器及微處理器系統,對接下來了解各種芯片及控制系統的很有幫助。

微處理器系統

微處理器系統,囊括了各種類型的計算機,微控制器/單片機。世界上的微處理器系統的總數比人類總數還多得多。它的基本工作原理是用程序控制系統的行為。

微處理器系統的基本操作過程是中央處理器(Central Processing Unit, CPU)不斷地從存儲器取指并執行,實現對系統的全面管理。

一、CPU結構和功能CPU的結構

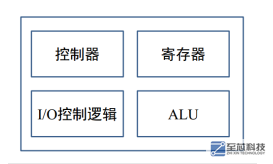

(下圖為CPU的結構)

1) 控制器:完成指令的讀入、寄存、譯碼和執行。

2) 寄存器:暫存用于尋址和計算過程的產生的地址和數據。

3) I/O控制邏輯:負責CPU中與輸入/輸出操作有關的邏輯。

4) 算數邏輯運算單元(Arithmetic & Logic Unit, ALU):運算器核心,負責進行算術運算、邏輯運算和移位操作,用來進行數值計算和產生存儲器訪問地址。

CPU的功能:

1) 與存儲器之間交換信息。

2) 和I/O設備之間交換信息。

3) 為了使系統正常工作而接收和輸出必要的信號,如復位信號、電源、輸入時鐘脈沖等。

二、微處理器系統的結構

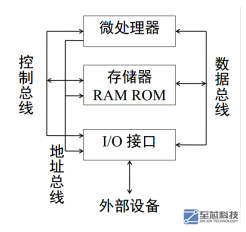

(下圖為微處理器系統的結構)

1) CPU的外部特征就是數量有限的輸入輸出引腳。

2) 數據總線:用于CPU和存儲器或I/O接口之間傳送數據,雙向通信;數據總線的條數決定了CPU和存儲器或I/O設備一次最多能交換數據的位數,是微處理器的位數的判據,例如:Intel 386DX、ARM Cortex-M3是32位微處理器;Intel采用了IA-64架構的處理器、PowerPC 970是64位處理器;類似地,還有更加古老的8位、16位處理器等。

3) 地址總線:CPU通過地址總線輸出地址碼用以選擇某一存儲單元或某一成為I/O端口的寄存器,單向通信;地址總線的條數決定了地址碼的位數,進而決定了存儲空間的大小,例如:地址總線寬度(條數)為8,則可以標記2^8 = 256個存儲單元,若每個存儲單元的字長為8 bit,則最大可以接入系統的存儲空間為256kB。

4) 控制總線:用來傳送自CPU發出的控制信息或外設送到CPU的狀態信息,雙向通信;

微處理器系統的程序設計語言:程序設計語言(Programming Language),又稱為編程語言,是用來定義計算機程序的,通過代碼向處理機發出指令。編程語言讓開發者能夠準確地提供計算機所使用的數據,并精確地控制在不同情況下所應當采取的行動。最早的編程語言是在計算機發明之后產生的,當時是用來控制提花織布機及自動演奏鋼琴的動作。在電腦領域已發明了上千不同的編程語言,而且每年仍有新的編程語言誕生。很多編程語言需要用指令方式說明計算的程序,而有些編程語言則屬于聲明式編程,說明需要的結果,而不說明如何計算。

機器語言:機器語言的每條語句即是處理器可以直接執行的一條指令,這些指令是以二進制0、1序列的形式表示,對應數字集成電路的高低電平。不同的處理器指令的機器代碼各不相同,完成的具體功能也將不相同,按著一種計算機的機器指令編寫的程序,不能在另一種計算機上執行。

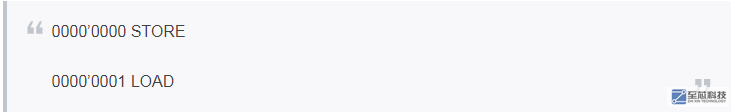

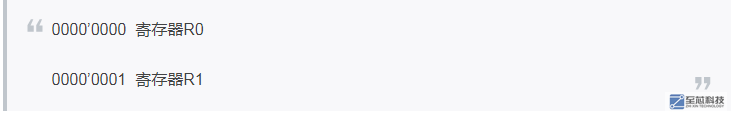

示例:(僅作為示例,不代表真實硬件的機器代碼)

指令的機器代碼:

地址的機器代碼:

優點:功能和代碼一一對應,CPU可以直接執行,效率最高。

缺點:只有二進制0、1序列,枯燥,難以辨識。

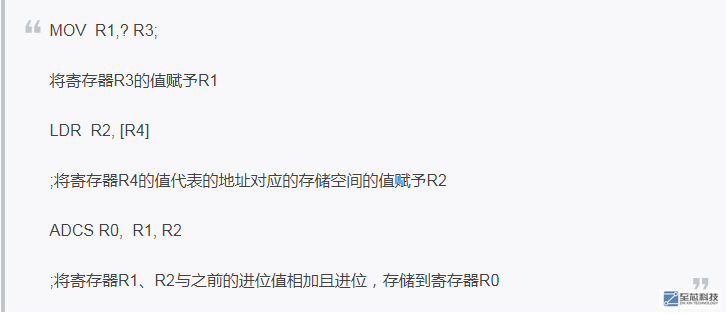

匯編語言:用簡潔的英文字母、符號串來替代一個特定的機器語言指令——二進制0、1序列:用助記符(Memoni)代替操作碼,用地址符號(Symbol)或標號(Label)代替地址碼。匯編語言與機器語言一一對應,所以和機器語言一樣對計算機硬件的依賴性很大。

示例:加法運算(分號表示接注釋)

優點:匯編語句和機器語言一一對應,助記符與標號往往與實際意義相關,相比于機器語言,更加直觀,容易理解,執行效率上類似。

缺點:不同的處理器指令集不同,移植性不好;即使完成簡單的數據處理(如累加,簡單排序等)所需的代碼體積很大,處理實際問題所需的工作量夸張,成本高。

高級語言:使用接近于數學語言或人類語言的表達描述程序。

特點:相比于面向機器開發的機器語言和匯編語言,高級語言擁有較高的可讀性,并且代碼量大大減少;高級語言通常遠離對硬件的直接操作,安全性較高,也有部分高級語言可以使用調用匯編語言的接口操控硬件;高級語言有很多成熟、易于使用、可移植的數據結構與算法,使開發流程大大簡化,節省開發成本,易于維護;發展迅速,社區完備,可以很方便地求助,解決遇到的各種問題;已經有很多各具特色、用以解決不同領域問題且發展相當完備的高級語言供開發者選用,如:適合初學者了解編程思想的Basic;效率頗高,接近于硬件操控,適合系統、硬件驅動編程與嵌入式開發的C/C++;跨平臺、可移植特性優良的Java;搭配Visual Studio可以快速開發項目的C#.NET;適合于數據分析、人工智能,越來越被青睞的Python;Microsoft公司為未來的量子計算而開發的Q#,等等。諸如MATLAB、HTML、JavaScript這樣的用以在不同領域大顯身手的語言亦可以稱之為高級語言。

示例:加法運算

優點:不依賴于硬件,移植性好;不用場合選用適合的語言,開發效率高。

缺點:不直接使用硬件,需要編譯-鏈接執行或解釋執行,沒有利用到具體硬件的特點,效率相比于機器語言和匯編語言不高;先天的特點決定了高級語言在底層的設計中無法完全取代機器語言和匯編語言。

可以看出,微處理器系統的核心部件是CPU,使用微處理器系統控制外部的設備工作的實質就是使用編寫軟件程序的手段來控制外部設備。由于CPU已經是一個完整的、封裝好的部件,系統的設計人員只能通過編寫軟件,再經由編譯器或解釋器翻譯為機器能夠理解的代碼來執行。

CPU并沒有專門的硬件電路來實現完全地控制外部設備的運行,這種實現方式是軟件實現,是一種通用的實現,控制信號從軟件到硬件要經過若干次轉化,但有的時候,工程和設計領域往往需要高速高性能的芯片來實現控制與計算,這時候就需要更加強大的CPU或將幾個CPU用一些技術并行起來協同工作,成本就會增加。這時候,可以不妨試試設計專門的硬件來滿足工作的需求。

三、專用集成電路

專用的集成電路(Application Specific Integrated Circuit, ASIC)是一種為專門目的而設計的集成電路。是指應特定用戶要求和特定電子系統的需要而設計、制造的集成電路。ASIC的特點是面向特定用戶的需求,ASIC在批量生產時與通用集成電路相比具有體積更小、功耗更低、可靠性提高、性能提高、保密性增強、成本降低等優點。

ASIC分為全定制和半定制。全定制設計需要設計者完成所有電路的設計,包括芯片設計的所有流程,因此需要大量人力物力,靈活性好但開發效率低下。如果設計較為理想,全定制能夠比半定制的ASIC芯片運行速度更快。

半定制ASIC使用準邏輯單元(Standard Cell),設計時可以從標準邏輯單元庫中選擇SSI(小規模集成電路,如門電路)、MSI(中規模集成電路,如加法器、比較器等)、數據通路(如ALU、存儲器、總線等)、存儲器甚至系統級模塊(如乘法器、微控制器等)和IP核,這些邏輯單元已經布局完畢,而且設計得較為可靠,設計者可以較方便地完成系統設計。

當今ASIC的設計方向已經越來越多地使用可編程邏輯器件來構造,開發門檻和難度不斷降低,流程不斷簡化,成本不斷下降,業務也開始變得豐富且多元化。目前ASIC已經走向了深度學習、人工智能、第五代移動通信技術(5G)等高新技術領域,在可編程邏輯器件兩大巨頭Xilinx和Altera的推動下,可以預見未來的ASIC設計將是可編程邏輯器件(尤其是現場可編程門陣列,FPGA)的天下。

四、可編程邏輯器件

可編程邏輯器件(Programmable Logic Device, PLD)是一種通用集成電路,它是ASIC的一個子集,邏輯功能可以按照用戶對器件編程來確定。一般的PLD的集成度很高,足以滿足設計一般的數字系統的需要。這樣就可以由設計人員自行編程而把一個數字系統“集成”在一片PLD上,而不必去請芯片制造廠商設計和制作ASIC芯片了,因為如果芯片需求量不大,設計制造ASIC的單片成本是很高的。

PLD與一般數字芯片不同的是:PLD內部的數字電路可以在出廠后才規劃決定,甚至可以無限制改變,而一般數字芯片在出廠前就已經決定其內部電路,無法在出廠后再次改變,事實上一般的模擬芯片、通信芯片、微控制器也都一樣,出廠后就無法再對其內部電路進行更改。最近鬧得沸沸揚揚的Intel公司的芯片漏洞事件,就是因為CPU的內部電路已經無法更改,所以只能設計新的CPU芯片來解決,或是損失一些性能用軟件修補的方法來彌補。

五、可編程邏輯器件的發展歷程

最早的可編程邏輯器件(PLD)是1970年制成的可編程只讀存儲器(PROM),它由固定的與陣列和可編程的或陣列組成。PROM采用熔絲技術,只能寫一次,不能擦除和重寫。隨著技術的發展,此后又出現了紫外線可擦除只讀存儲器(UVEPROM)和電可擦除只讀存儲器(EEPROM)。由于其價格便宜、速度低、易于編程,適合于存儲函數和數據表格。

可編程邏輯陣列(PLA)于20世紀70年代中期出現,它是由可編程的與陣列和可編程的或陣列組成,但由于器件的價格比較貴、編程復雜、資源利用率低,因而沒有得到廣泛應用。

可編程陣列邏輯(PAL)是1977年美國MMI公司率先推出的,它采用熔絲編程方式,由可編程的與陣列和固定的或陣列組成,采用雙極性工藝制造,器件的工作速度很高。由于它的設計很靈活,輸出結構種類很多,因而成為第一個得到普遍應用的可編程邏輯器件

通用陣列邏輯(GAL)是1985年Lattice公司最先發明的可電擦寫、可重復編程、可設置加密位的PLD。GAL在PAL的基礎上,采用了輸出邏輯宏單元形式(EECMOS)工藝結構。在實際應用中,GAL對PAL仿真具有百分之百的兼容性,所以GAL幾乎完全代替了PAL,并可以取代大部分標準SSI、MSI集成芯片,因而獲得廣泛應用。

可擦除可編程邏輯器件(EPLD)是20世紀80年代中期Altera公司推出的基于UVEPROM和CMOS技術的PLD,后來發展到采用EECMOS工藝制作的PLD,EPLD的基本邏輯單元是宏單元,宏單元是由可編程的與陣列、可編程寄存器和可編程I/O三部分組成的。從某種意義上講,EPLD是改進的GAL,它在GAL基礎上大量增加輸出宏單元的數目,提供更大的與陣列,集成密度大幅提高,內部連線相對固定,延時小,有利于器件在高頻下工作,但內部互連能力較弱。

復雜可編程邏輯器件(CPLD)是20世紀80年代末Lattice公司提出了在線可編程技術(SP)以后于20世紀90年代初推出的。CPLD至少包含三種結構:可編程邏輯宏單元可編程I/O單元和可編程內部連線,它是在EPLD的基礎上發展起來的,采用EECMOS工藝制作,與EPLD相比,增加了內部連線,對邏輯宏單元和I/O單元也有很大改進。

現場可編程門陣列(FPGA)器件是Xilinx公司1985年首家推出的,它是一種新型的高密度PLD,采用CMOS-SRAM工藝制作。FPGA的結構與門陣列PLD不同,其內部由許多獨立的可編程邏輯模塊(CLB)組成,邏輯塊之間可以靈活地相互連接,CLB的功能很強,不僅能夠實現邏輯函數,還可以配置成RAM等復雜的形式。配置數據存放在芯片內的SRAM中,設計人員可現場修改器件的邏輯功能,即所謂的現場可編程。FPGA出現后受到電子設計工程師的普遍歡迎,發展十分迅速。

FPGA和CPLD都具有體系結構和邏輯單元靈活、集成度高以及適用范圍寬的特點。這兩種器件兼容了簡單PLD和通用門陣列的優點,可實現較大規模的電路,編程也很靈活,與ASIC相比,具有設計開發周期短、設計制造成本低,開發工具先進、標準產品無須測試、質量穩定等優點,用戶可以反復地編程、擦除、使用,或者在外圍電路不動的情況下用不同軟件就可實現不同的功能以及可實時在線檢驗。

CPLD是一種比PLD復雜的邏輯元件。CPLD是一種用戶可根據各自需要而自行構造邏輯功能的數字集成電路。與FPGA相比,CPLD提供的邏輯資源相對較少,但是經典CPLD構架提供了非常好的組合邏輯實現能力和片內信號延時可預測性,因此對于關鍵的控制應用比較理想。

FPGA是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為ASIC領域中的一種半定制電路而出現的,提供了豐富的可編程邏輯資源、易用的存儲、運算功能模塊和良好的性能,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

FPGA和CPLD因為結構上的區別,各具自身特色。因為FPGA的內部構造觸發器比例和數量多,所以它在時序邏輯設計方面更有優勢:而CPLD因具有與或門陣列資源豐富、程序掉電不易失等特點,適用于組合邏輯為主的簡單電路。總體來說,由于FPGA資源豐富功能強大,在產品研發方面的應用突出,當前新推出的可編程邏輯器件芯片主要以FPGA類為主,隨著半導體工藝的進步,其功率損耗越來越小,集成度越來越高。

在微處理器系統上,軟件設計師用程序設計語言控制整個系統的正常運轉,而在可編程器件領域,操作的對象不再是一組組數據類型,而是一些硬件器件,如存儲器,計數器等,甚至是一些更加底層的觸發器、邏輯門,有的甚至要精確到集成晶體管開關級的控制。并且很多器件不再是順序的阻塞式工作,而是并行的觸發工作,經典的程序流程控制思想在可編程器件領域不適用。設計人員需要使用一種能夠構造硬件電路的語言,即硬件描述語言。

六、硬件描述語言

硬件描述語言(Hardware Description Language, HDL)是一種用形式化方法描述邏輯電路和系統的語言。利用這種語言,邏輯電路系統的設計可以從上層到下層(從抽象到具體)逐層描述自己的設計思想,用一系列分層次的模塊來表示極其復雜的邏輯系統。

然后,利用電子設計自動化(EDA)工具,逐層進行仿真驗證,再把其中需要變為實際電路的模塊組合,經過自動綜合工具轉換到門級電路網表。接下來,再用專用集成電路(ASIC)或現場可編程門陣列(FPGA)自動布局布線工具,把網表轉換為要實現的具體電路布線結構。據統計,目前在美國的硅谷約有90%以上的ASIC和PLD采用硬件描述語言進行設計。

硬件描述語言HDL的發展至今已有30多年的歷史,其成功地應用于設計的各個階段:建模、仿真、驗證和綜合等。到20世紀80年代,已出現了上百種硬件描述語言,對設計自動化曾起到了極大的促進和推動作用。但是,這些語言一般各自面向特定的設計領域和層次,而且眾多的語言使用戶無所適從。

因此,需要一種面向設計的多領域、多層次并得到普遍認同的標準硬件描述語言。20世紀80年代后期至90年代,VHDL和Verilog HDL語言適應了這種趨勢的要求,先后成為電氣和電子工程師協會(Institute of Electrical & Electronics Engineers, IEEE)標準。

現在,隨著超大規模FPGA以及包含SoC內核FPGA芯片的出現,軟硬件協調設計和系統設計變得越來越重要。傳統意義上的硬件設計越來越傾向于與系統設計和軟件設計結合。硬件描述語言為適應新的情況,迅速發展,出現了很多新的硬件描述語言,像System Verilog,SystemC、Cynlib C++等;另一方面,PLD設計工具在原先僅支持硬件描述語言設計輸入的基礎上,日益增加對傳統高級設計語言(如C/C++)的設計支持。

目前,硬件描述語言可謂是百花齊放,有VHDL、Verilog HDL、Superlog、SystemC、System Verilog、Cynlib C++、C Level等。整體而言,在PLD開發領域應用最廣的還是VHDL和Verilog HDL。隨著邏輯系統開發規模的不斷增大,SystemC和System Verilog等系統級硬件描述語言也得到越來越多的應用。

VHDL

早在1980年,因為美國軍事工業需要描述電子系統的方法,美國國防部開始進行VHDL的開發。1987年,IEEE將VHDL制定為標準。參考手冊為IEEE VHDL語言參考手冊標準草案1076/B版,于1987年批準,稱為IEEE 1076-1987。然而,起初VHDL只是作為系統規范的一個標準,而不是為設計而制定的。第二個版本是在1993年制定的,稱為VHDL-93,增加了一些新的命令和屬性。

雖然有“VHDL是一個4億美元的錯誤”這樣的說法,但VHDL畢竟是1995年以前唯一制定為標準的硬件描述語言,這是它不爭的事實和優勢;但同時它的使用確實比較麻煩,而且其綜合庫至今也沒有標準化,不具有晶體管開關級模擬設計的描述能力。目前來說,對于特大型的系統級邏輯電路設計,VHDL是較為合適的。

實質上,在底層的VHDL設計環境是由Verilog HDL描述的器件庫支持的,因此,它們之間的互操作性十分重要。目前,Verilog和VHDL的兩個國際組織OVI(Open Verilog International)、VI正在籌劃這一工作,準備成立專門的工作組來協調VHDL和Verilog HDL語言的互操作性。OVI也支持不需要翻譯,由VHDL到Verilog的自由表達。

Verilog HDL

Verilog HDL是在1983年,由GDA(Gateway Design AUTOMATION)公司的Phil Moorby首創的。Phil Moorby后來成為Verilog-XL的主要設計者和Cadence公司的第一合伙人。在1984-1985年,Phil Moorby設計出了第一個名為Verilog-XL的仿真器;1986年,他對Verilog HDL的發展又作出了另一個巨大的貢獻:提出了用于快速門級仿真的XL算法。

隨著Verilog-XL算法的成功,Verilog HDL語言得到迅速發展。1989年,Cadence公司收購了GDA公司,Verilog HDL語言成為Cadence公司的私有財產。1990年,Cadence公司決定公開Verilog HDL語言,于是成立了OVI組織,負責促進Verilog HDL語言的發展。

基于Verilog HDL的優越性,IEEE于1995年制定了Verilog HDL的IEEE標準,即Verilog HDL 1364-1995;2001年發布了Verilog HDL 1364—2001標準,在這個標準中,加入了Verilog HDL - A標準,使Verilog HDL有了模擬設計描述的能力

SystemC

隨著半導體技術的迅猛發展,SoC已經成為當今集成電路設計的發展方向,智能手機,平板電腦里的處理器,嚴格地來說實際上是SoC,因為其上集成了CPU、圖形處理單元(Graphic Processing Unit, GPU)、數字信號處理器(Digital Signal Processor)、基帶(Baseband)信號處理器等。在系統芯片的各個設計(像系統定義、軟硬件劃分、設計實現等)中,集成電路設計界一直在考慮如何滿足SoC的設計要求,一直在尋找一種能同時實現較高層次的軟件和硬件描述的系統級設計語言

SystemC正是在這種情況下,由Synopsys公司和Coware公司積極響應目前各方對系統級設計語言的需求而合作開發的。1999年9月27日,40多家世界著名的EDA公司、IP公司、半導體公司和嵌入式軟件公司宣布成立“開放式SystemC聯盟”。著名公司Cadence也于2001年加入了SystemC聯盟。SystemC從1999年9月聯盟建立初期的0.9版本開始更新,從1.0版到1.1版,一直到2001年10月推出了最新的2.0版。

七、常見的數據處理芯片

既然已經梳理了兩大類(微處理器,專用集成電路)芯片的概念和原理,接下來就了解一下常見的芯片

日常生活中最常見得到的微處理器系統就是我們身邊的微型計算機,也就是個人電腦(Personal Computer, PC),可以使臺式機、筆記本,或是PC界的新秀——各種炫酷的二合一設備。這些看起來復雜無比的電子系統都是由最簡單的微處理器系統發展起來的。

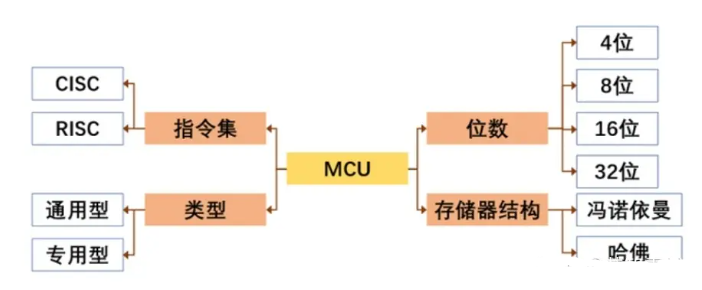

但是生活中并不需要那么多的電腦,比如想要做一臺能夠自動控制加熱保溫的電飯煲,其CPU性能可能只需要電腦這樣的大家伙的九牛一毛即可,也不需要復雜的輸入輸出設備,在設計上大可以大刀闊斧地將用不到的部分砍掉,靈活地將CPU、時鐘發生器(Clock)、隨機存儲器(Random Access Memory, RAM)、只讀存儲器(Read-Only Memory, ROM)和需要的外部設備集成起來小型化,這種經過大改觀的微處理器系統,其所有部分都集成在了一塊芯片上,稱為微控制器或單片機(Micro Controller Unit, MCU)。

目前MCU是應用最廣泛的一種電子控制芯片,其控制程序可以由特殊的燒錄工具下載到ROM中,行使系統的功能。這些ROM可以使以是PROM、UVEPROM、EEPROM等,若MCU上沒有集成ROM,也可以外接ROM。按照系統結構,微處理器系統可以分為馮·諾依曼結構(也稱普雷斯頓結構)和哈佛結構,其區別是程序與數據的存放方式不同,同樣地,MCU芯片也可以分為這兩種結構,靈活地滿足需要。

MPU

微處理器單元(Micro Processor Unit, MPU),就是把很多CPU集成在一起并行處理數據的芯片。通俗來說,MCU集成了RAM,ROM等設備;MPU則不集成這些設備,是高度集成的通用結構的中央處理器矩陣,也可以認為是去除了集成外設的MCU。

PLD(CPLD/FPGA)

因為目前廣泛使用的PLD是CPLD和FPGA,因此把這兩種芯片作為例子介紹。前面已經介紹過,CPLD/FPGA的內部結構和CPU完全不同,內部電路可以被多次修改,可以按照用戶的編程形成不同的組合邏輯電路、時序邏輯電路結構,是一種“萬能”的芯片,CPLD/FPGA看起來像一個CPU。

其實不然,因為使用CPLD/FPGA實現控制是純硬件實現,實質上和使用成千上萬基本邏輯門搭建的數字邏輯電路沒有區別。因此可以直接用HDL編程在CPLD/FPGA里搭建出一個“CPU”(有時還有硬盒和軟核之分,限于篇幅,不再贅述),再做好相應的I/O、總線,就是一個簡單的微處理器系統了。

但是這樣一來,又變成了軟件控制,PLD的硬件控制優勢蕩然無存。故CPLD/FPGA經常和實際的CPU搭配使用,在CPLD/FPGA上編寫一些較復雜算法的運算電路,當CPU處理到這些復雜任務時,就交由CPLD/FPGA進行處理,處理結束以后再將結果返回給CPU,提高控制系統的整體性能。

自然界的物理量分為模擬(Analog)量和數字(Digital)量兩種。模擬量在一定范圍內的取值是連續的,個數是無窮的;數字量在一定范圍內的取值是離散的,個數是有限的。計算機只能處理離散的數字量,所以模擬信號必須經過變換才能交由計算機處理。

將自然界的物理量轉化為連續變化的電流或電壓(故稱“模擬”),在滿足奈奎斯特采樣定理(Nyquist Sampling Theory,也稱香農采樣定理,Shannon Sampling Theory)的條件下采樣,得到時域離散信號,再經量化器(可以是線性量化和非線性量化)量化后數字信號,最后經過一道編碼得到二進制的0、1數字信息,才能交由計算機處理。

以上的這一道變換稱為模數轉換(A/D),可以將這部分電路集成到一塊芯片上,這就是模數轉換電路(Analog Digital Circuit, ADC),相應的也有數模轉換(D/A)和數模轉換電路(Digital Analog Circuit, DAC)芯片,進行D/A的時候同樣要在數學和信息論上滿足相關定理。

DSP

數字信號處理器(Digital Signal Processor, DSP)是用來高速處理數字信號的專用芯片。

經過ADC轉化好的數字信號,數據量往往很龐大,直接交由CPU處理的效率是不高的,并且CPU還要進行更多的通用計算的任務。因此,常常采用專用的電路來處理數字信號,如數字濾波、快速傅里葉變換、時頻分析、語音信號和圖像信號的處理加工等。這些運算往往很復雜,很多涉及復數的累加、累乘運算。

舉個例子:離散傅里葉變換的計算就十分復雜,但是運用時域抽取或頻域抽取的快速傅里葉變換算法后就可以大大減少運算量,但是電路較為復雜。將能完成這些復雜運算的電路集成在一塊芯片上,能在一個時鐘周期完成一次乘加運算,使其能完成如基2-FFT蝶形運算、音頻濾波、圖像處理等復雜運算,這樣的芯片叫做DSP。

DSP也是一種特殊的CPU,特別適合信號的處理,如3G中的Node B就大量使用了DSP進行信號處理。DSP對于流媒體的處理能力遠遠的優于CPU,現在手機上的語音信號都是由DSP處理的。現階段DSP的概念正在變得模糊,如ARM9的架構就不像是一顆CPU,更像是一顆DSP。現在有很多芯片,其上都集成了DSP,GPU,基帶處理器等,越來越多的傳統上分立的芯片被集成到一起,協同工作以提高效率,降低能耗,這也是未來的一個趨勢。

SoC

隨著半導體技術、移動互聯網和智能終端的迅猛發展,傳統的微處理器系統的發展已經跟不上時代的潮流,現代信息技術迫切地需要一種功能多,性能強,功耗低的芯片來滿足越來越多的智能設備的需求。SoC便應運而生。

SoC的全稱是System on a Chip,顧名思義,就是在一塊芯片上集成一整個信息處理系統,稱為片上系統或系統級芯片。這個定義現在也不盡明確,因為不同用途的SoC上集成的部件是不一樣的,一般說來,SoC是一個完整的整體,已經擁有了整個數字系統的完整功能它也是一種ASIC,其中包含完整的控制系統并有嵌入式的軟件。

SoC也代表著一種技術,是一種以確定系統功能為目標,各個模塊的軟硬件協同開發,最后把開發成果集成為一塊芯片的技術。由于功能豐富,又要求有不俗的性能發揮,SoC已然是功能最為豐富的硬件,其上集成了CPU、GPU、RAM、ADC/DAC、Modem、高速DSP等各種芯片,有的SoC上還必須集成電源管理模塊,各種外部設備的控制模塊,充分考慮各總線的分布利用……現如今,智能手機里的SoC上就集成了以上的部件和基帶處理器等很多相關的通信模塊。

SoC的電路相比于傳統的微處理器系統更加復雜,其對設計和制造工藝的要求自然更上一層樓,對軟硬件協同開發的依賴性相當高。迄今為止,在半導體行業首屈一指的企業才有自主設計制造SoC的能力,目前在性能和功耗敏感的終端芯片領域,SoC已占據主導地位,人們每天使用的手機里面,就有一顆顆性能強勁,永遠在線的SoC在為我們服務。

就連傳統的軟件大廠微軟也推出了基于高通公司的驍龍835平臺的Windows操作系統;而且SoC的應用正在擴展到更廣的領域,SoC在無人機技術、自動駕駛,深度學習等行業也有越來越多的應用,用一塊單芯片就能實現完整的電子系統,是半導體行業、IC產業未來的發展方向。

編輯:jq

-

dsp

+關注

關注

552文章

7962瀏覽量

348265 -

cpu

+關注

關注

68文章

10825瀏覽量

211149 -

adc

+關注

關注

98文章

6438瀏覽量

544096 -

soc

+關注

關注

38文章

4122瀏覽量

217938

原文標題:簡談CPU、MCU、FPGA、SoC這些芯片異同之處

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MCU和FPGA的區別分析

接口芯片是cpu與外設之間的界面嗎

soc芯片和mcu芯片區別在哪

mcu芯片和電源芯片有什么區別

SoC芯片與CPU芯片有什么區別

CPU、MPU、MCU、SOC的差異

MCU分類有哪些 soc芯片和mcu芯片區別

淺談CPU、MCU、FPGA、SoC這些芯片之間有何不同

淺談CPU、MCU、FPGA、SoC這些芯片之間有何不同

評論