本講使用matlab產生待濾波信號,并編寫testbench進行仿真分析,在Vivado中調用FIR濾波器的IP核進行濾波測試,下一講使用兩個DDS產生待濾波的信號,第五講或第六講開始編寫verilog代碼設計FIR濾波器,不再調用IP核。

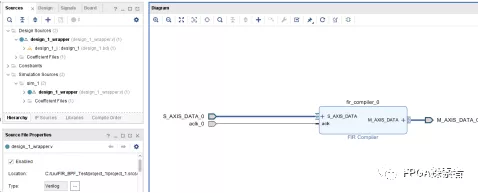

本例使用上一講的FIR濾波器IP核工程。

matlab與FPGA數字濾波器設計(2)——Vivado調用IP核設計FIR濾波器

matlab與FPGA數字濾波器設計(1)——通過matlab的fdatool工具箱設計FIR數字濾波器

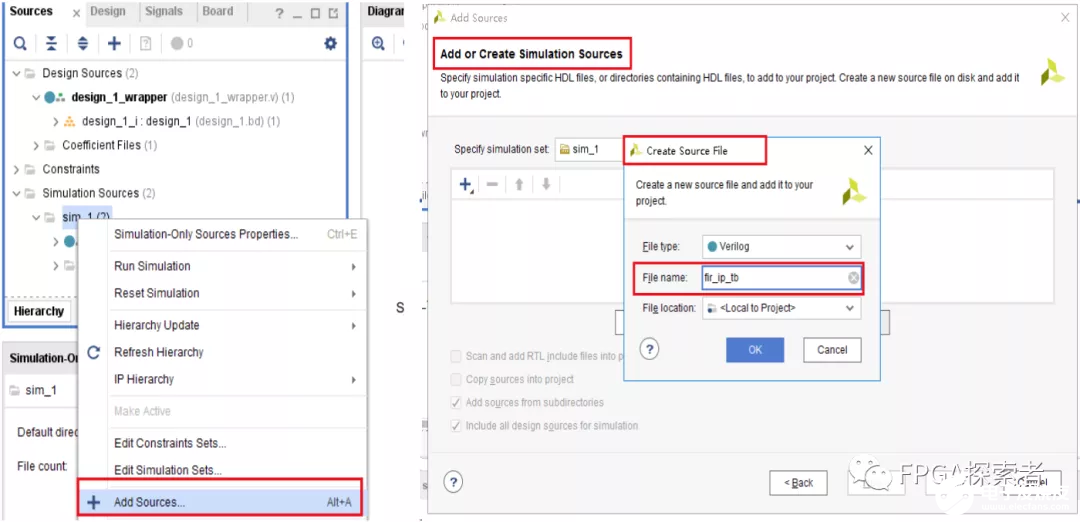

1. 新建仿真文件

(1) Simulation Sources -》 sim_1 -》右鍵 Add Sources;

(2) Add or Create Simulation Sources,新建仿真文件 fir_ip_tb;

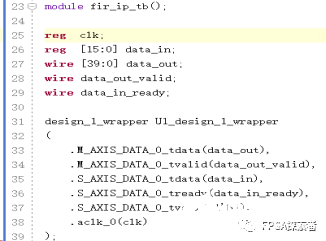

2. 編寫testbench

(1) 例化加入的IP核,其中:

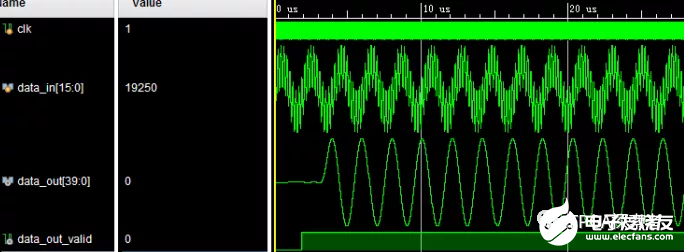

輸入時鐘引腳為 clk,設置為32MHz(此處暫時還未設定頻率);

輸入數據引腳為data_in,位寬16-bit,表示待濾波數據;

輸出數據引腳為data_out,位寬40-bit,表示濾波后的數據;

輸出數據有效信號引腳data_out_valid,位寬1-bit,輸出狀態,為高電平時表示輸出的data_out有效;

輸入數據準備好信號引腳data_in_ready,位寬1-bit,輸出狀態,為高電平時表示準備好接收輸入數據;

輸入有效信號S_AXIS_DATA_0_tvalid,為1時表示輸入信號有效,為0時即使有輸入信號data_in到 fir 的 ip 核 ,ip 核也不做處理,此處直接讓其恒為1,輸入數據恒有效;

總結,需要給ip核輸入的數據目前只有兩個,一個是時鐘,一個是待濾波數據。

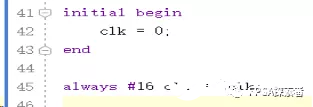

(2) 產生32MHz時鐘信號;

初始 initial 時設置時鐘信號clk為低電平0,always 表示一直執行,#16表示每隔16 ns(單位是在仿真文件開頭自動有定義ns)時鐘取反一次,即每隔 16ns 時鐘 0/1間隔變化,相當于32ns一個時鐘周期,約等于32MHz;

3. 產生待濾波數據data_in

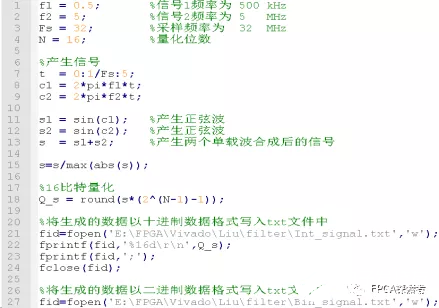

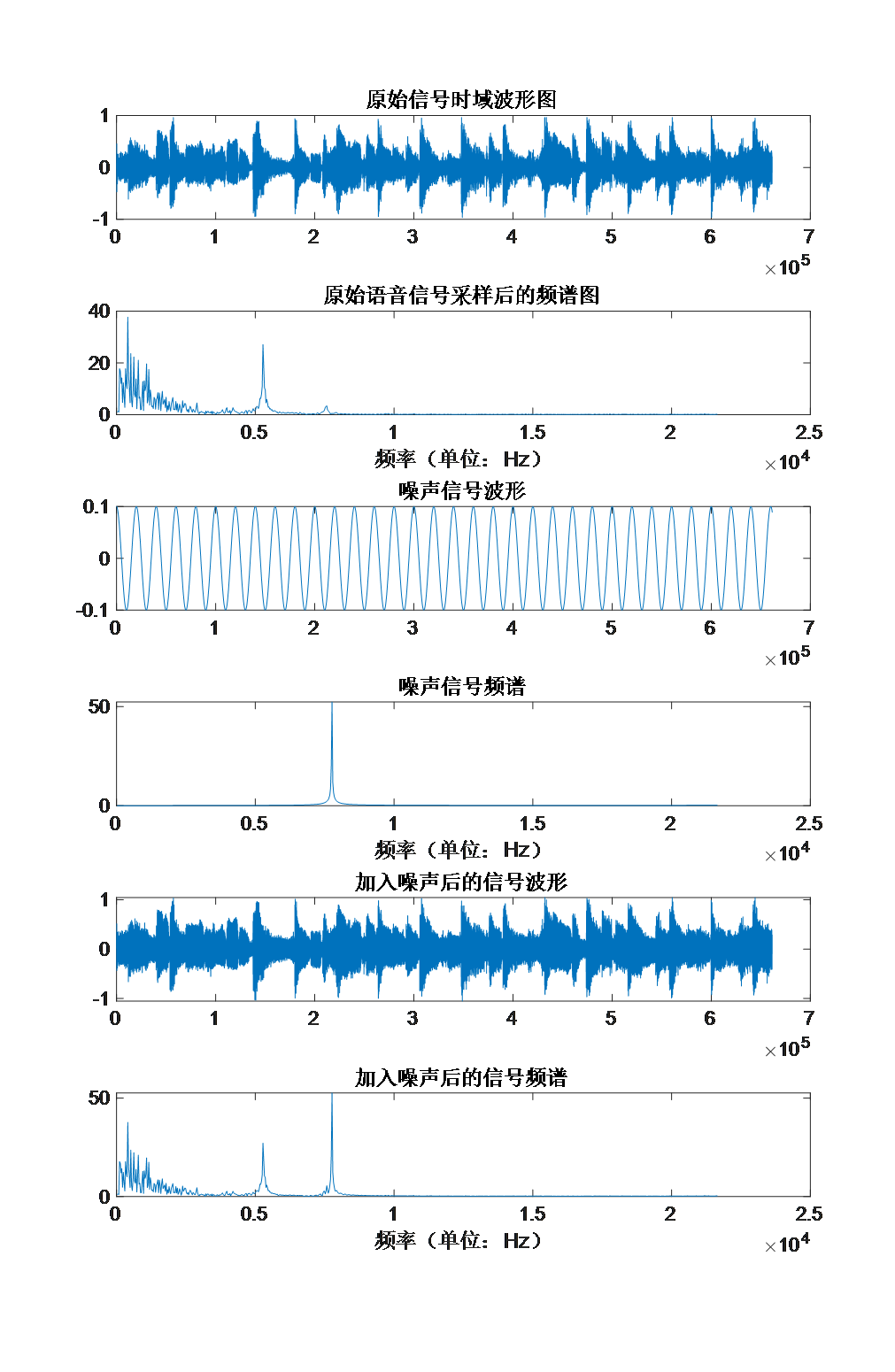

(1) 編寫matlab程序,產生兩個信號0.5MHz和5MHz,采樣頻率32MHz,采樣5個周期,進行16-bit量化,并把量化后的數據寫到 .txt 文件中;

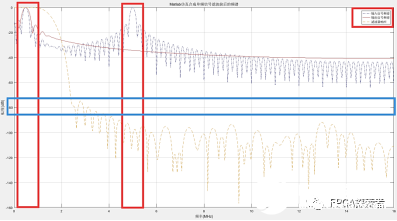

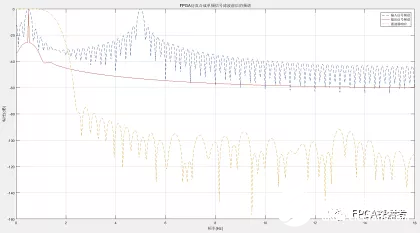

可以看到,在 0.5MHz 和 5MHz處有兩個峰,表示抽樣后的兩個信號,經過濾波器之后,5MHz 信號被濾除,只剩下 0.5MHz 信號,藍色框內可以看到,在 3MHz 以后濾波器的響應已經低于 -80dB,相當于濾波后的幅度是濾波前的1/10000,濾波效果很好。

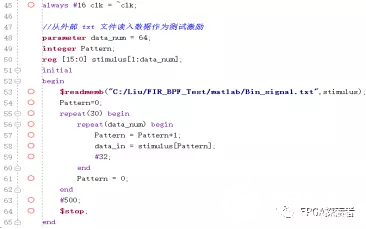

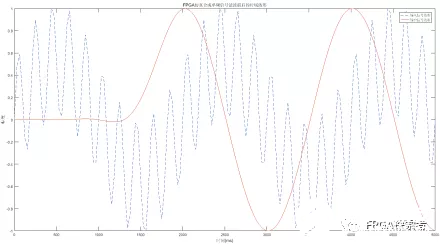

使用 32MHz 的采樣時鐘采樣 0.5MHz 待濾波信號(相當于0.5MHz信號疊加了5MHz噪聲),每個周期采樣 64 個點,在testbench中讀取一個周期的64個點,重復30個周期得到30個周期的輸入待濾波信號給FIR濾波器;

4. 仿真結果分析

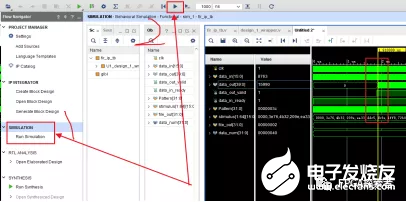

點擊1處開始仿真,Vivado中一般默認只會仿真1us,這時候只看到了初始化的一部分,是看不到后續結果的,點擊2處進行仿真,會將所有的仿真步驟完成,執行到上圖中第64行的 $stop 語句停止仿真;

5. 仿真結果分析

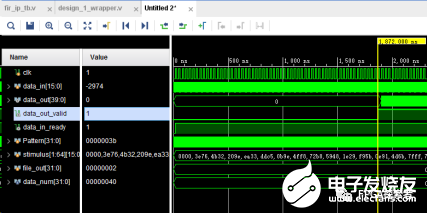

(1) data_out_valid:初始為0,在1.872 ns跳變為1,輸出數據開始有效,在為0的那段時間輸出數據data_out無效,這段時間內是FIR的IP核進行一些內部的配置和初始化;

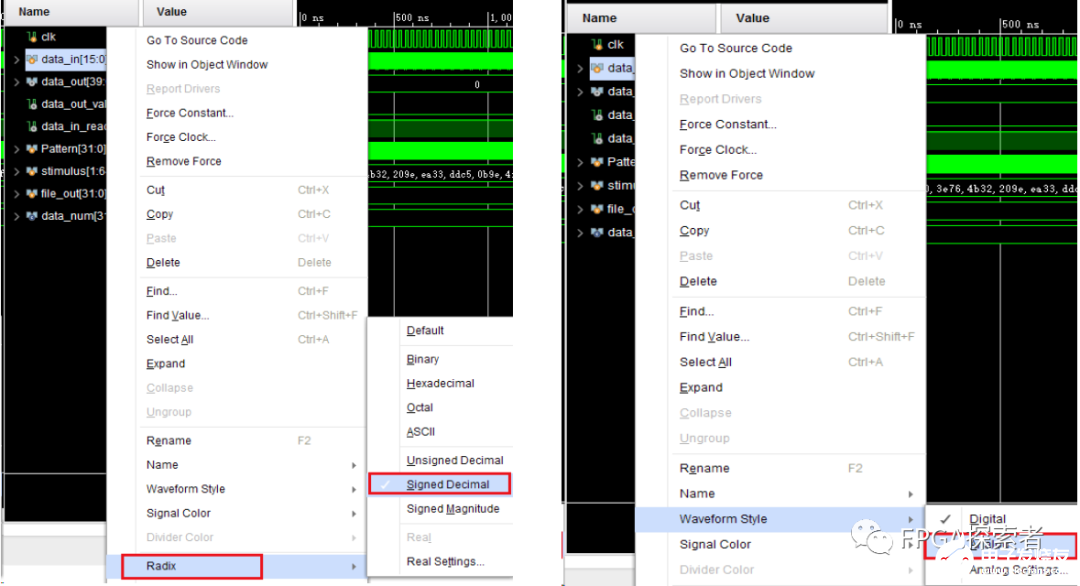

(2) 更改數據表示模式

對data_in,右鍵設置其數據格式Radix為有符號的十進制數(Signed Decimal),設置其波形為模擬波形(Analog);

對 data_out 同樣設置;

對 Pattern 設置 無符號十進制,不需要設置波形。

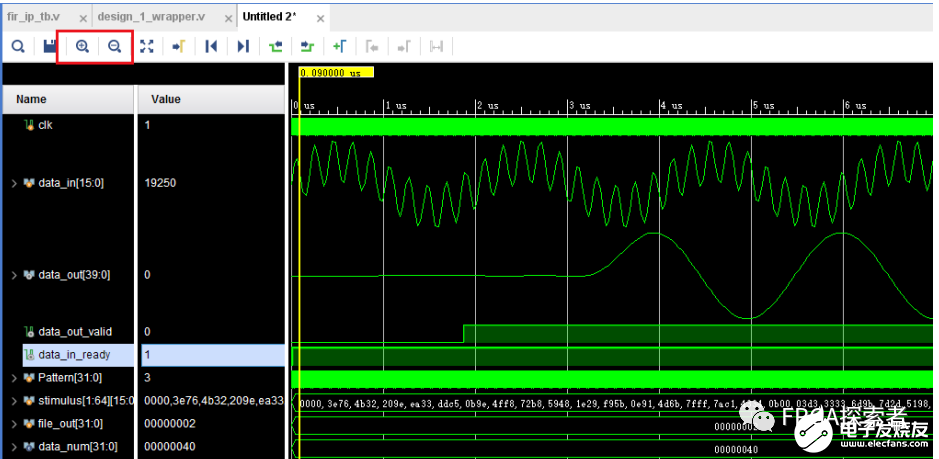

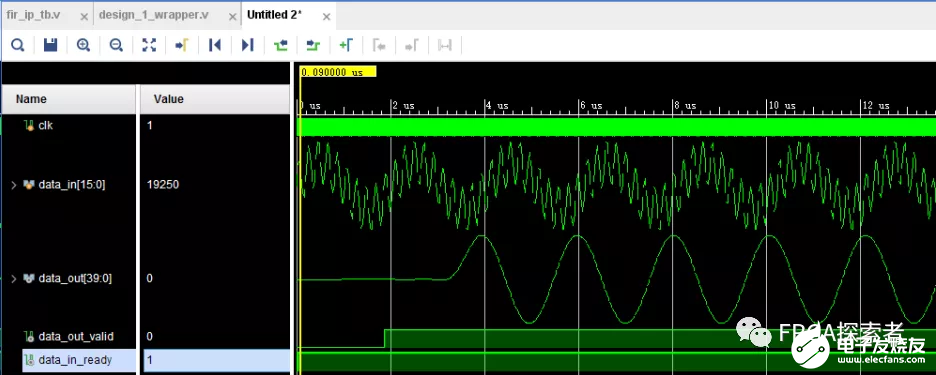

(3) 點擊放大縮小可以查看整個仿真的效果

通過下面幾圖,可以看到仿真效果很好,5MHz高頻噪聲濾除干凈,肉眼觀察不出來。

(4) Matlab數據分析

肉眼觀察時域的仿真圖無法得知高頻噪聲具體被濾掉了多少,是否還混有噪聲,此時需要將濾波后的數據按照前文讀取仿真數據的方式,將仿真得到的濾波后的數據寫入.txt文件,再通過 matlab 讀取 FPGA 濾波后的數據并進行FFT 頻譜分析,通過頻域的波形來觀察濾波效果,通過 matlab 仿真,可以看到高頻信號的確被濾除。

下一講使用兩個 DDS 產生待濾波的信號,結合FIR濾波器搭建一個信號產生及濾波的系統,并編寫testbench進行仿真分析。

編輯:lyn

-

matlab

+關注

關注

182文章

2963瀏覽量

230170 -

仿真

+關注

關注

50文章

4044瀏覽量

133419 -

fir濾波器

+關注

關注

1文章

95瀏覽量

19026 -

Vivado

+關注

關注

19文章

808瀏覽量

66329

發布評論請先 登錄

相關推薦

編寫高效Testbench的指南和示例

Matlab/Simulink/Stateflow建模開發及仿真測試

基于MATLAB的數字濾波器語音信號去噪

使用matlab產生待濾波信號并編寫testbench進行仿真分析

使用matlab產生待濾波信號并編寫testbench進行仿真分析

評論