一、IBERT與GT收發器概述

1. IBERT

IBERT(Integrated Bit ErrorRatio Tester,集成誤比特率測試工具),是Xilinx提供用于調試FPGA高速串行接口比特誤碼率性能的工具,最常用在GT高速串行收發器測試:

(1)基于PRBS模塊的誤碼率測試;

(2)測量眼圖;

IBERT核心是為PMA評估和演示而設計,GT收發器的所有主要物理介質連接(PMA)功能都得到支持和可控,包括:TX預加重/后加重、TX差速擺動、RX均衡、決策反饋均衡器(DFE)、鎖相環(PLL)分頻設置等。

2. GT

GT(Gigabyte Transceiver,G比特收發器),通常也稱Serdes、高速收發器。Xilinx的7系列FPGA根據不同的器件類型,集成了GTP、GTX、GTH以及GTZ四種串行高速收發器。按支持的最高線速率排序,GTP是最低的,用于A7系列;GTZ最高,用于少數V7系列;K7和V7中常見的是GTX和GTH。ZC706中包含16個GTX。

GT的應用非常廣泛,高速ADC和DAC使用的JESD204B、高速接口SRIO(Serial RapidIO)、Aurora、PCIE、千兆網、XAUI萬兆網等都是基于GT實現。在使用GT之前,首先需要進行IBERT測試,給出誤碼率、眼圖等信息,保證GT收發器工作正常。若IBERT測試不通過,則根據近端、自環和遠端的測試去排除PCB走線、阻抗、時鐘、復位、電源等原因。

二、IBERT配置

1. 在“IP Catalog”中找到IBERT

雙擊IP核進行配置。

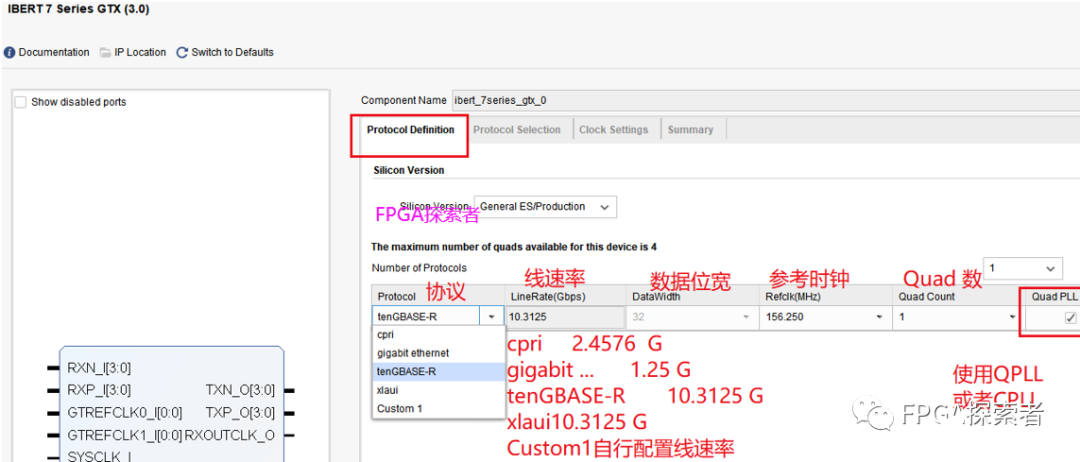

2. 第一頁配置高速串行協議

第一頁協議選項中默認為Custom1,可以自行輸入線速率、時鐘等參數,其余協議選項是對應著固定的線速率和時鐘,比如tenGBASE-R對應10.3125G通信速率的萬兆網通信,使用時鐘頻率156.25MHz,選擇使用QPLL鎖相環,選擇后整個Quad的4個GT共用一個QPLL(Quad PLL),否則每個Channel通道各自使用自己的CPLL(Channel PLL)。

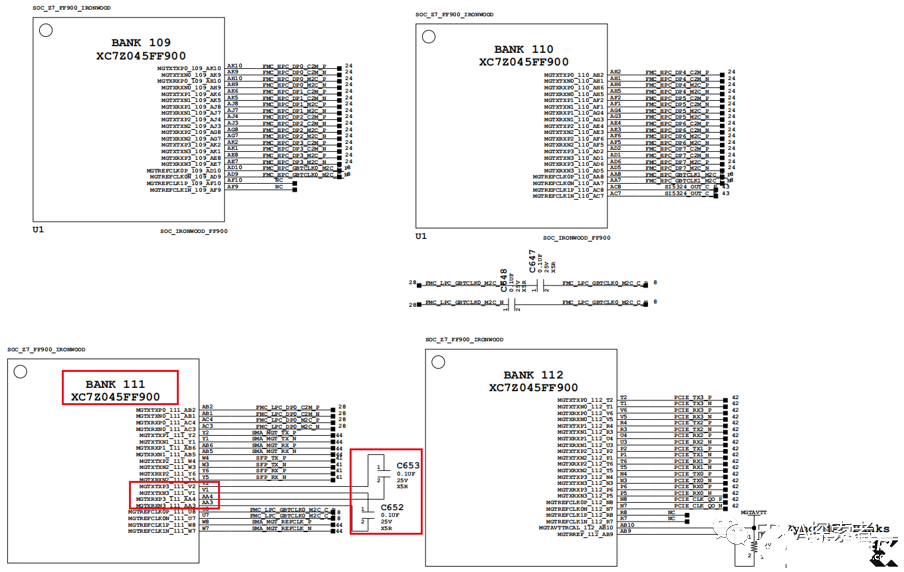

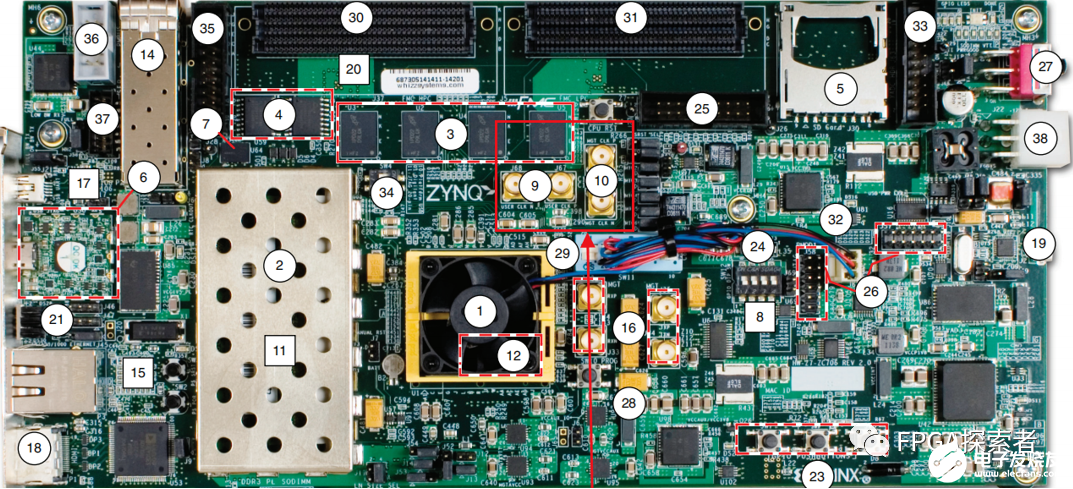

ZC706原理圖第8頁(公眾號回復【ZC706原理圖】獲取),ZC706中的BANK109~112四個Bank是高速收發器Bnak,每個Bnak中含有4個獨立的GT收發器和一個QPLL,組成一個Quad,每個GT稱為一個Channel。其中,Quad109和Quad110是FMC_HPD,Quad111支持Channel0是FMC_LPC,Channel1使用SMA接口輸出,Channel2連接光纖SFP+,Channel3直接TX和RX連接形成自環,用于測試GT,Quad112用于PCIE。

在使用過程中,出于對時鐘的考慮:

Quad109的參考時鐘0來源于FMC_HPC板卡,參考時鐘1未連接(NC);

Quad110的參考時鐘0來源于FMC_HPC板卡,參考時鐘1來源于一個時鐘芯片SI5324,但是需要進行相應配置才能輸出(IIC配置寄存器);

Quad111的參考時鐘0來源于FMC_LPC板卡,參考時鐘1通過SMA接頭由外部輸入;

Quad112的參考時鐘0來源于PCIE設備,參考時鐘1未連接(NC);

綜上考慮,在ZC706沒有連接FMC和PCIE設備情況下,只能使用Quad111的參考時鐘1,通過外部SMA接入差分的參考時鐘。Quad111中的Channel3恰好已經設計成自環,剛好選定Quad111進行IBERT測試。

重要!由于相鄰Bnak可以相互借用時鐘,所以,這里在使用Bnak111的參考時鐘1的前提下,也可以選擇Bnak110和Bnak112上的GT進行IBERT測試,但是不能使用Bnak109,因為Bank111的時鐘無法給Bank109使用,但是可以給Bnak110和Bank112使用。

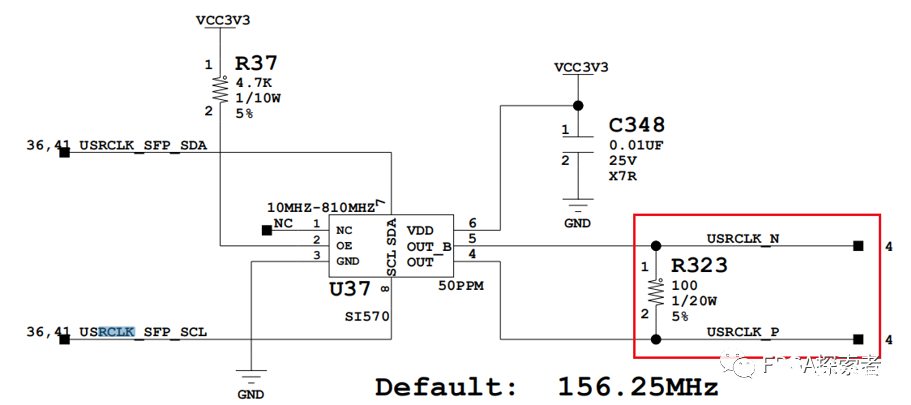

在ZC706板上,如下圖所示,有一個一上電就會輸出的差分時鐘USRCLK,默認輸出頻率156.25MHz,恰好可以用來作為時鐘,并將其通過SMA接頭的USER_SMA_CLOCK輸出,外部使用SMA接頭射頻線將USRCLK和USER_SMA_CLOCK連接,即為Quad111引入了一組156.25MHz的差分時鐘。(注意!兩根射頻線必須等長)

標號9和10的兩對SMA接口使用等長的射頻線連接,絲印號P端連接P端,N端連接N端。

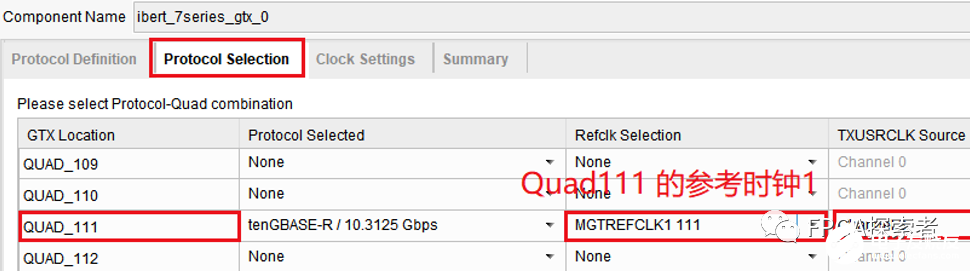

3. 第二頁配置Quad和參考時鐘

根據2的說明,這里選擇QUAD_111,并將參考時鐘選擇Quad111的參考時鐘1(MGTREFCLK1),由于使用整個Quad的四個通道,并且使用QPLL,所以這里的Channel任選一個Channel0 ~ Channel3即可。

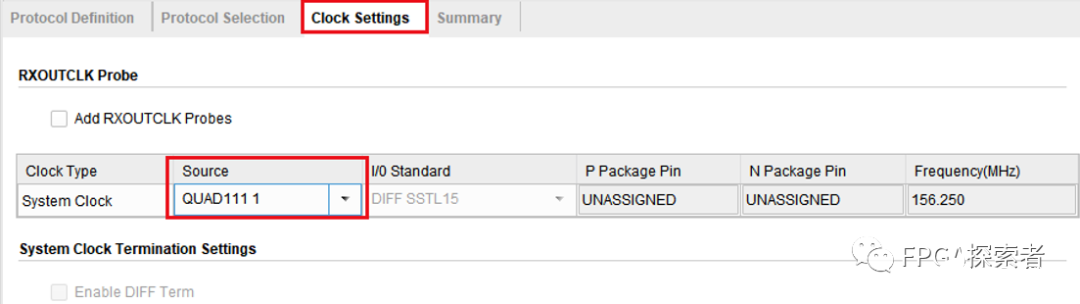

4. 第三頁配置時鐘來源

時鐘來源配置為Quad111的參考時鐘1。

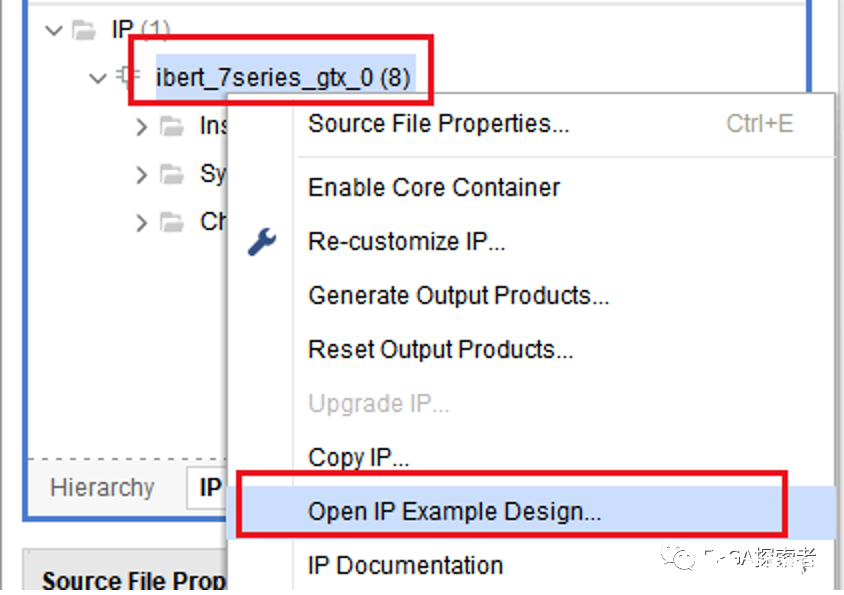

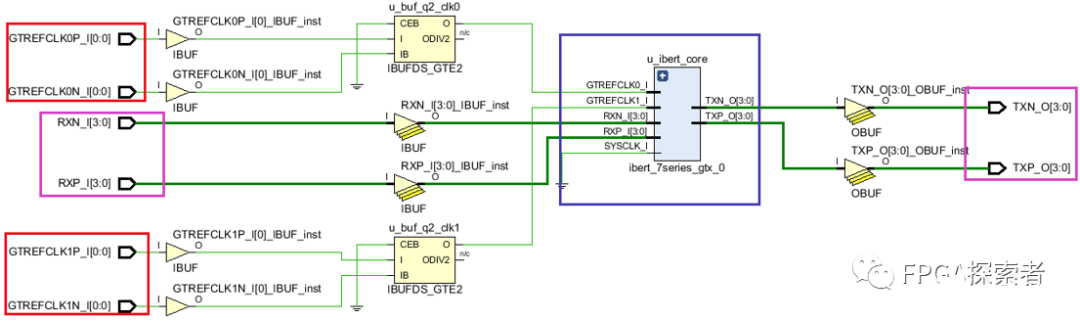

三、示例工程

示例工程生成參考:如何使用Xilinx官方例程和手冊學習IP核的使用——以高速接口SRIO為例

四、時鐘配置

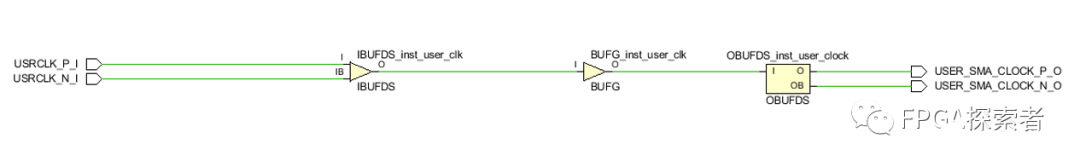

增加差分輸入時鐘USRCLK,首先輸入使用IBUFDS差分輸入轉單端得到user_clk信號,然后使用全局緩沖BUFG資源將user_clk綁定全局時鐘網絡,最后使用OBUFDS單端轉差分輸出。

FPGA從外部輸入時鐘時,必須使用全局時鐘輸入管腳輸入,必須經過全局時鐘緩沖IBUFG(單端時鐘)或IBUFGDS(差分時鐘),否則布線報錯,常見的使用方式是IBUF或IBUFDS后加一個BUFG組合。

BUFG,全局緩沖,輸出到達FPGA內部個邏輯單元的時鐘延遲和抖動最小。

參考 https://blog.csdn.net/zkf0100007/article/details/82559250

wire user_clk; IBUFDSIBUFDS_inst_user_clk( .O(user_clk), // Buffer output .I(USRCLK_P_I), // Diff_p bufferinput .IB(USRCLK_N_I) //Diff_n buffer input ); wireuser_clk_bufg; BUFGBUFG_inst_user_clk ( .O(user_clk_bufg), // 1-bit output: Clock output .I(user_clk) ); OBUFDSOBUFDS_inst_user_clock ( .O (USER_SMA_CLOCK_P_O), // Diff_p output .OB(USER_SMA_CLOCK_N_O), //Diff_n output .I (user_clk_bufg) //Buffer input );

IBUFDS+BUFG+OBUFDS。

設置XDC時鐘約束和管腳約束:

create_clock -name usrclk -period 6.4 [get_ports USRCLK_P_I] create_clock -name user_sma_clk -period 6.4 [get_portsUSER_SMA_CLOCK_P_O] set_property PACKAGE_PIN AF14 [get_ports USRCLK_P_I] set_property IOSTANDARD LVDS_25 [get_ports USRCLK_P_I] set_property PACKAGE_PIN AD18 [get_ports USER_SMA_CLOCK_P_O] set_property IOSTANDARD LVDS_25 [get_ports USER_SMA_CLOCK_P_O]

五、誤碼率及眼圖測試

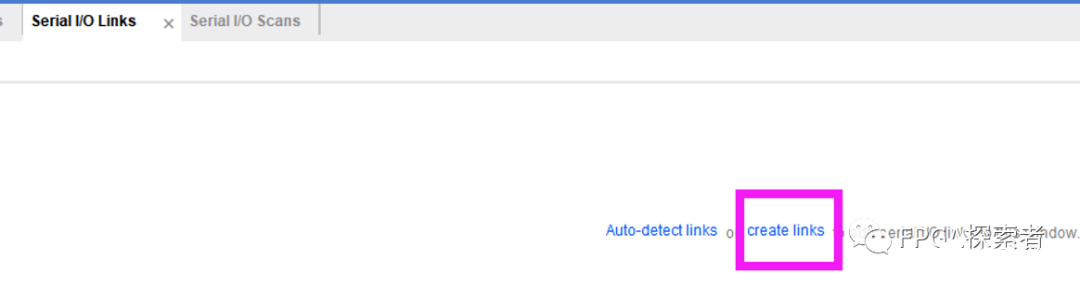

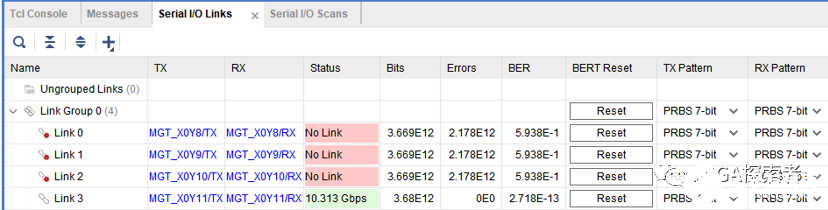

編譯、布局布線并生成Bitstream,下載到ZC706。在Vivado下方出現“Serial I/O Links”,點擊Auto-detect links會自動檢測已經連通的鏈路,點擊Create Link可以觀察工程中配置的所有鏈路。

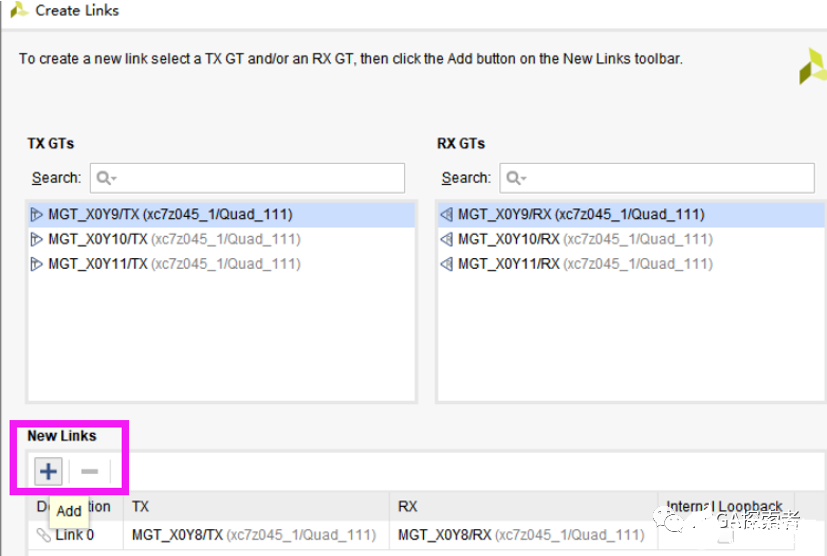

點擊Create Link,點擊“+”號選擇上方的鏈路,點擊4次選擇4個鏈路。

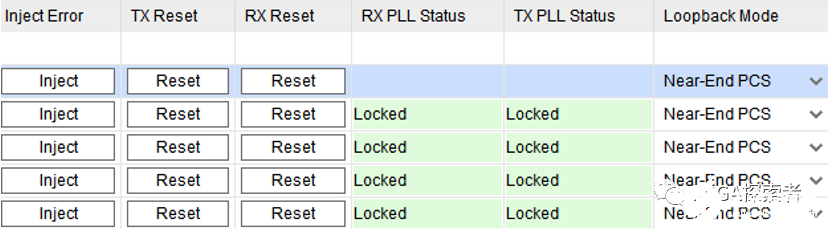

由于Quad111的Channel3是直接TX和RX直連構成自環,所以下載IBERT后在Link3上就已經實現連通,通信速率10.313Gbps,誤碼率10的-13次方,測試時可以點擊Reset復位重測,更改Links里面的配置時也需要Reset復位一下,否則誤碼率較高。

配置4個通道均為近端PCS自環或者近端PMA自環(Near-End),內部構成自環,4個鏈路均進行近端內部自環測試,兩個FPGA通信時可以配置遠端PCS自環或者遠端PMA自環測試鏈路(Far-End)。

更改上述配置后,先Reset復位,否則誤碼率較高。

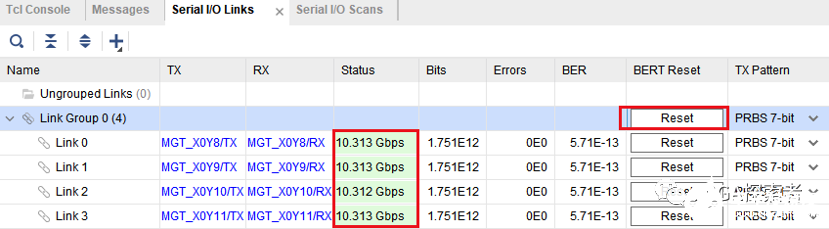

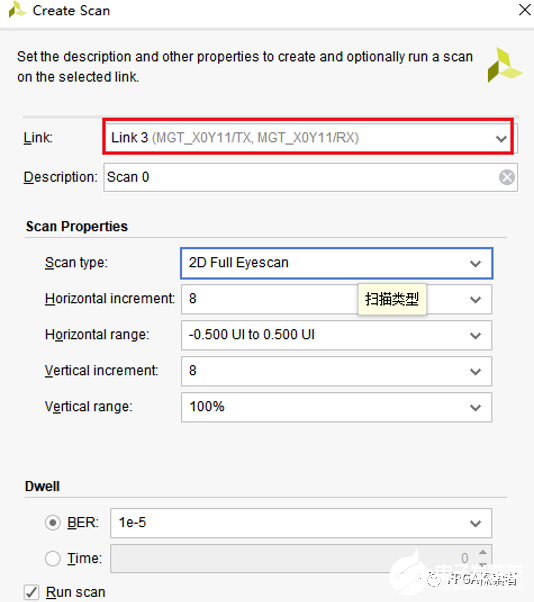

創建眼圖的掃描。

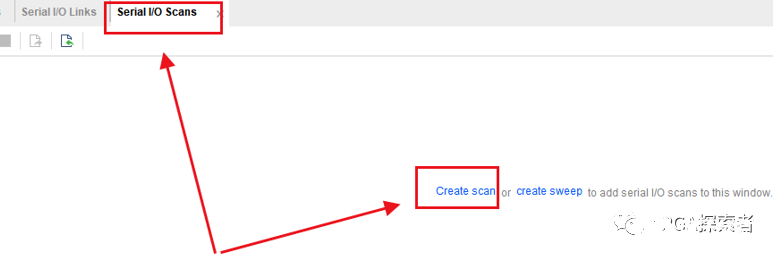

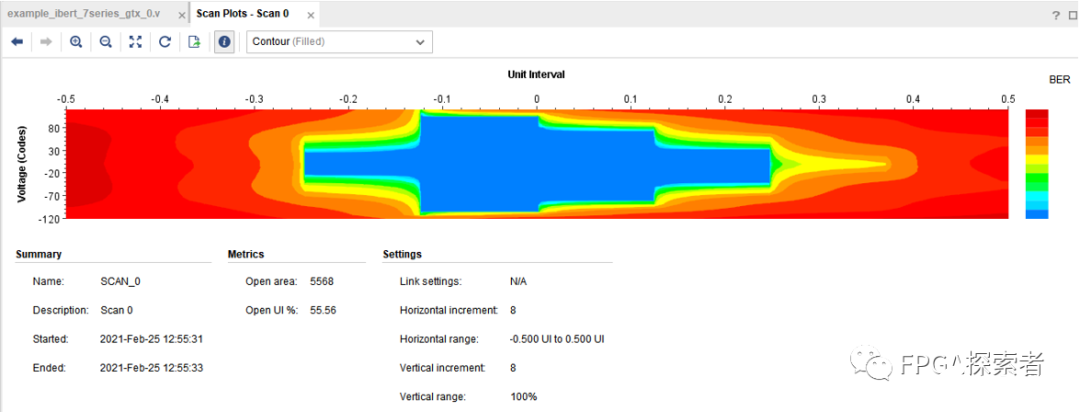

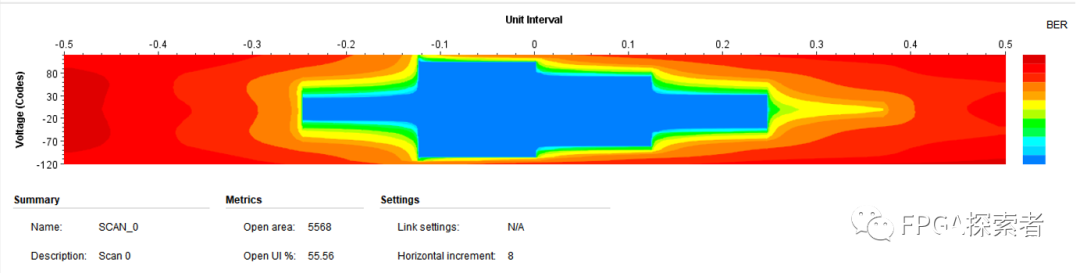

可見在中心位置處眼圖張的比較開(藍色),信道質量較好,橫著看張開的范圍較小,主要原因是運行的線速率太高,如果使用1.25G的千兆網協議,則眼圖會更好。

從信號完整性的角度來看,眼圖中間的藍色區域越大,GTX所對應的PCB高速電路的信號完整性越好。

編輯:lyn

-

收發器

+關注

關注

10文章

3339瀏覽量

105546 -

IP核

+關注

關注

4文章

318瀏覽量

49271 -

GT

+關注

關注

0文章

14瀏覽量

24620

發布評論請先 登錄

相關推薦

內置誤碼率測試儀(BERT)和采樣示波器一體化測試儀器安立MP2110A

關于ZC706評估板的IBERT誤碼率測試和眼圖掃描詳細分析

關于ZC706評估板的IBERT誤碼率測試和眼圖掃描詳細分析

評論