摘要: 為了滿足瞬變電磁探測中晚期電磁信號采集的要求,選擇高性能24位模數轉換器AD7762,以FPGA為控制核心實現信號的高精度采集,結合USB2.0接口芯片CY7C68013-A,將采集的數據高速傳輸至上位機,上位機采用LabVIEW作為開發平臺,完成數據顯示和分析功能。實驗結果表明,基于FPGA的電磁信號采集系統具有良好的性能指標和擴展性,測量準確,能夠滿足電磁探測數據采集的要求。

瞬變電磁探測是應用較為廣泛有效的地下礦產勘探、地質調查方法之一。它通過發射機發射激勵場源,當發射電流關斷時在地下導電性的介質或地質體中感生渦流形成瞬變二次磁場,在一次場間隙時間內測量二次場隨時間衰減響應,最后通過數據反演解釋,直接給出探測區域的地下視電阻斷面圖。

瞬變電磁信號采集系統采集到的二次場電磁信號動態范圍大、信號微弱、頻帶寬,特別是中晚期響應幅值小、衰減慢,幅值從毫伏級(或微伏級)衰減到微伏級(或納伏級),觀測時間需要幾百微秒到幾毫秒甚至幾秒,晚期信號反映深層地下結構,測量數據的質量直接影響后期處理解釋,需要精確地采集瞬變響應信號[1]。晚期瞬變電磁信號變化緩慢,傳統16位分辨率的采集系統已經不能滿足要求,為了提高分辨率,增強信噪比,本設計采用24位采集技術與雙級程控放大濾波去噪,實現瞬變電磁信號的高分辨率采集,結合FPGA在數據獲取方面優越的實時與并行控制性能,簡化了硬件電路結構,有利于系統的功能升級,可以快速實現多路電磁信號的高精度采集。

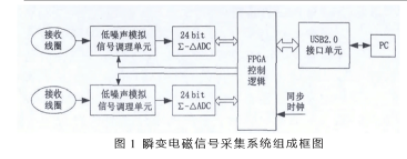

1 系統總體結構

瞬變信號采集系統由接收線圈、低噪聲模擬信號調理電路、24位ADC單元、FPGA、USB2.0接口單元等組成。低噪聲模擬信號調理電路采用雙級程控放大濾波去噪技術,對接收線圈接收到的電磁信號放大、濾波;FPGA作為整個采集系統的控制邏輯核心,完成采集過程的邏輯控制,獲取采樣數據;USB2.0接口芯片CY7C68013-A將數據高速傳輸至上位機,上位機采用LabVIEW作為開發平臺,完成采樣參數的設置控制、數據分析和顯示功能,瞬變電磁信號采集系統組成框圖如圖1所示。

2 系統硬件設計

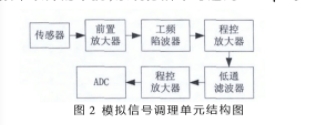

2.1 模擬信號調理單元

瞬變電磁信號中含有天然低頻電磁噪聲、工頻噪聲、風動噪聲成分,如果不進行處理,噪聲將與有用信號一起輸出,嚴重影響測量結果的準確度。模擬信號調理電路設計采用雙級程控放大與低通濾波去噪相結合的方式,去除信號中的噪聲,并使被測電壓范圍和A/D采樣范圍相匹配。

模擬信號調理單元結構圖如圖2所示。前置放大器采用低噪聲高輸入阻抗的AD8421,前放與雙級程控放大器之間加入抑制工頻及其諧波干擾的陷波器。為了提高信噪比,雙級程控放大器采用ADI公司的AD8231,AD8231可以通過引腳編程選擇增益,最大為128,當增益G=1時,共模抑制比(CMRR)為80 dB,共模抑制比隨增益提高而增加,最高可達110 dB,輸入偏置電壓漂移最大為50 nV/℃,可以有效改善電磁數據采集系統的溫漂性能[2]。瞬變電磁信號放大后,再通過低通濾波器去除頻帶以外的干擾,系統分辨率可達到0.05 μV。

2.2 24位模數轉換器單元

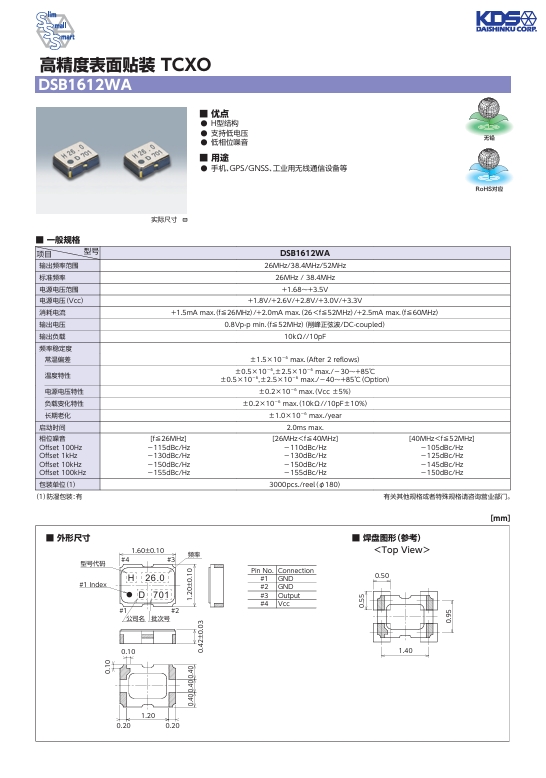

系統采用兩片單通道24位并行輸出Sigma-Delta模數轉換芯片AD7762,其具有寬頻帶差分信號輸入,最高轉換速率可達625 kS/s。能根據需求靈活地通過軟件設置來改變過采樣因子, 當輸入時鐘頻率一定時,過采樣因子越大,輸出速率越低,但信噪比越高,這一特性正好符合電磁采集的要求,即頻率越低,要求信噪比越高[3],其具有較寬的動態范圍和輸入帶寬,適合于低功耗數據采集應用。

AD7762是對噪聲敏感的模擬器件,所以在電路及PCB設計時需要做到以下幾個方面:A/D模擬電源單獨供電(模擬電源與數字電源分開供電,電源輸入引腳增加三端濾波器,減少電源噪聲對A/D干擾);模擬地和數字地單點接地;差分輸入線等長;采用精確的參考電壓源[4]。

AD7762內部自帶一個2.0 V的基準電壓,當有效精度接近或超過20位時,內部基準無法提供穩定的電壓,為了保證A/D轉換的精度,采用外部低噪聲基準電壓,選用ADI公司的高精度電壓參考源芯片ADR434,它具有低噪聲、高精度和出色的長期穩定性,輸出電壓為4.096 V,電壓可以穩定到1.5 mV。

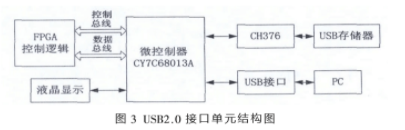

2.3 USB2.0接口單元

USB2.0接口單元主要由微控制器、數據存儲模塊、液晶顯示模塊組成,如圖3所示。微控制器采用Cypress公司的CY7C68013-A,由它完成數據采集控制及數據采集后與PC之間的高速數據傳輸。數據存儲模塊采用CH376控制器,將采集到的電磁數據以二進制文件形式保存到USB存儲設備中。

3 系統軟件設計

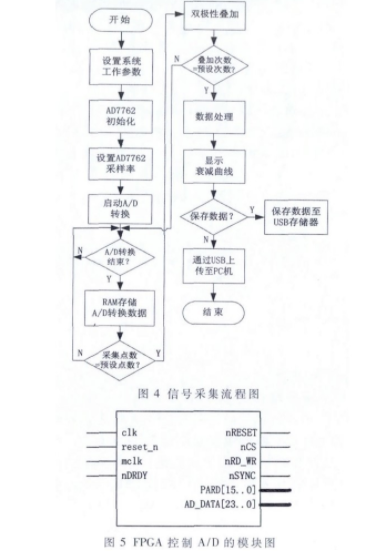

3.1 信號采集流程

系統首先通過設置AD7762工作模式及其采樣率啟動采集,系統工作參數設置包括設置放大倍數、設置采樣點數、設置疊加次數。由于每次啟動AD7762會有一定延遲,為了保證與發射機同步的精度,AD7762啟動后一直工作,當系統檢測到同步信號后,將24位轉換數據暫存在FPGA內部的RAM中。

每次采集點數達到所需時,系統從RAM中讀出轉換數據,通過檢驗數據是否有效,以FPGA硬件方式實現數據的疊加平均,經過處理后的數據可通過液晶顯示電磁信號電壓衰減曲線,也可通過USB傳輸至上位機,實現數據分析和顯示。信號采集控制的流程圖如圖4所示。

3.2 AD7762采樣控制程序

AD7762采樣控制模塊采用Verilog HDL語言編寫,固化在FPGA內,完成A/D初始化控制及A/D數據讀控制,其中A/D初始化控制完成對A/D內部控制寄存器的寫操作,而A/D數據讀控制完成對A/D數據的讀取,FPGA提供AD7762工作所需的時鐘信號。具體控制邏輯根據AD7762的時序圖設計,FPGA控制A/D的模塊圖如圖5所示。

模塊中FPGA通過 PARD[15..0]向AD7762寄存器寫入配置數據及讀取轉換后的結果,AD_DATA[23..0]輸出24位A/D轉換數據[5], nRESET是A/D的復位信號,reset_n是系統的復位信號,mclk接FPGA內部PLL輸出20 MHz時鐘信號,n_SYNC是同步信號。

3.3 USB固件程序

固件程序主要實現芯片的初始化、處理USB標準設備請求和控制芯片CY7C68013接收應用程序的控制指令等功能。在使用FX2芯片進行應用開發時,利用其固件框架可以簡化、加速開發,它提供任務調度、標準設備請求解析和USB中斷處理三類子函數[6]。通過編寫固件初始化函數TD_Init()即可完成芯片端點和外設的配置等[7],系統中設置端點6為輸入端點,16位數據自動輸入。

4 系統測試

4.1 短路噪聲測試

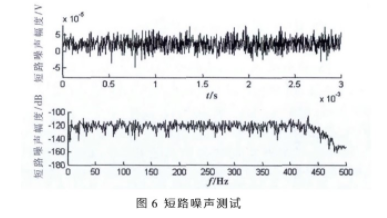

將采集系統的模擬信號輸入端短路,模擬通道增益設置為1,記錄系統在短路情況下噪聲的時間序列并進行頻譜分析。如圖6所示為短路噪聲測試結果,從時域波形看峰值約為 0.1 mV,頻譜分析結果顯示整個頻帶短路噪聲幅度低于110 dB。

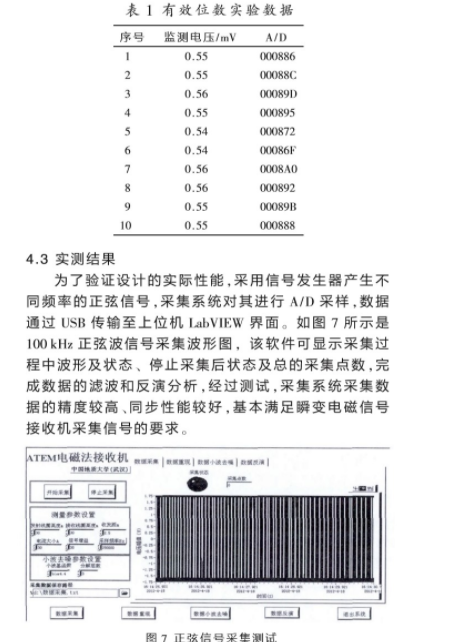

4.2 有效采樣位數實驗

為了驗證設計采用24位模數轉換器AD7762的有效采樣位數,采用SG1060A數字合成信號發生器給出基準信號,同時用LNI公司的LNI-T UT805A型5位半數字萬用表進行監測。實驗信號為0 V基準電壓,每隔60 s取一次采樣數據,萬用表監測電壓與輸出的24位采樣數據的關系如表1所示。實驗結果表明,系統有效采樣位數可達到18位。

針對瞬變電磁信號的特點設計了基于FPGA的電磁信號采集系統,實驗測試結果表明,采集系統取得了良好的性能。采用FPGA控制系統設計更為靈活方便,減少外部控制線的數量,使系統減小干擾,更為可靠;采用USB2.0標準接口,提高了數據的傳輸速率,具有良好的可擴展性,功耗低,兩個通道可同時采集,實現瞬變電磁信號的多通道采集,數據可以上傳存儲在PC中,實現進一步的分析和處理。

參考文獻

[1] 牛之璉。 時間域電磁法原理[M]。 長沙: 中南大學出版社, 2007:88-93.

[2] 韓祖淵, 張赤斌, 徐揚。 基于ARM7的高精度陣列式皮帶秤微控制器的設計[J]。 儀表技術與傳感器, 2010(9):

60-62.

[3] 裴婧, 蔣奇云。 基于AD7762的廣域電磁接收機采集器設計[J]。 地球物理學進展, 2010, 25(3):1110-1114.

[4] 彭輝。 24通道高精度A/D數據采集模塊的研制[J]。 現代電子技術, 2008(14):41-42,48.

[5] 王霖郁, 張建宏。 基于AD7762和FPGA的數據采集系統設計[J]。 電子科技, 2012, 25(6):30-33.

[6] 夏益明,王廣君。基于USB總線的高速數據采集系統[J]。國外電子元器件, 2003(10):20-23.

[7] 焦斌亮, 韓志學。基于EZ-USB FX2實現的高速數據采集系統[J]。 儀表技術與傳感器, 2005(7):21-22.

編輯:jq

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602044 -

芯片

+關注

關注

454文章

50460瀏覽量

421980 -

電路

+關注

關注

172文章

5852瀏覽量

171945 -

電磁信號放大器

+關注

關注

0文章

4瀏覽量

1895

發布評論請先 登錄

相關推薦

音頻信號采集為什么要用專用的CODEC來實現,普通高精度高采樣率ADC可以嗎?

藍牙AOA高精度定位系統效果怎么樣

工業制造領域高精度人員定位系統(源碼)

基于FPGA的圖像采集與顯示系統設計

什么是高精度定位平板?

北斗高精度定位終端的工作原理和精度范圍

什么是TCXO晶振?它為什么能提供高精度的時鐘信號?

AD7175-2適合做高精度數據采集嗎?

矽力杰多通道高精度DAC

剖析FPGA的高精度電磁信號采集系統設計

剖析FPGA的高精度電磁信號采集系統設計

評論