每一個做數字邏輯的都繞不開跨時鐘域處理,談一談SpinalHDL里用于跨時鐘域處理的一些手段方法。

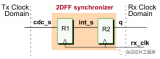

打拍處理 跨時鐘域信號的打拍處理往往用于單比特信號或類似于格林碼這種信號的跨時鐘域處理。其邏輯電路很簡單。SpinalHDL提供了BufferCC用于實現這種跨時鐘域打拍處理方式:

BufferCC(input: T, init: T = null, bufferDepth: Int = 2)

bufferDepth可用于指定打拍級數。input信號的時鐘域為源時鐘域,BUfferCC調用的地方的時鐘域為目的時鐘域。 在日常的電路設計里,計數器是常見的DFX信號,有些情況下需要將一個時鐘域的DFX信號轉換到另一個時鐘域進行HPI讀取,這種情況也可以通過打拍進行處理,不過前提是需轉換成格林碼,如此在源時鐘域和目的時鐘域需分別做一次轉換與反轉換。但如果計數器采用格林碼進行計數則可以少進行一次轉換。SpinalHDL有提供一個GrayCounter方法用于生成格林碼計數器:

GrayCounter(width: Int, enable: Bool)

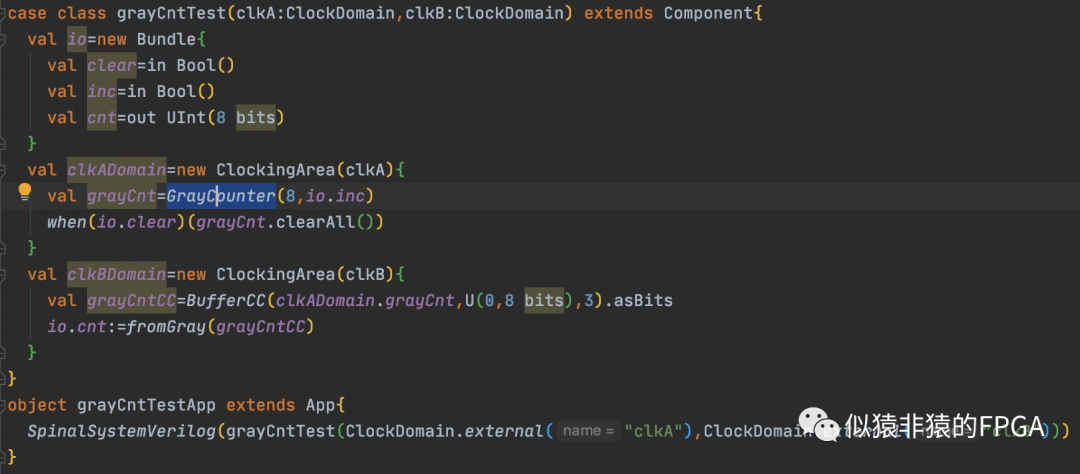

提供一個小demo,GtayCounter+BufferCC:

這里GrayCounter在時鐘域clkA中實現,通過BufferCC將其跨時鐘域至clkB,bufferDepth為3.Tips:BufferCC的第二個參數init數據類型是T,而T《:Data,即意味著init數據類型為“硬件”數據類型,因而上面init賦值需為U(0,8 bits)而不能直接寫0》》脈沖信號處理 脈沖信號的跨時鐘域處理,SpinalHDL提供了PulseCCByToggle方法:

PulseCCByToggle(input: Bool,clockIn: ClockDomain,clockOut: ClockDomain): Bool

握手處理

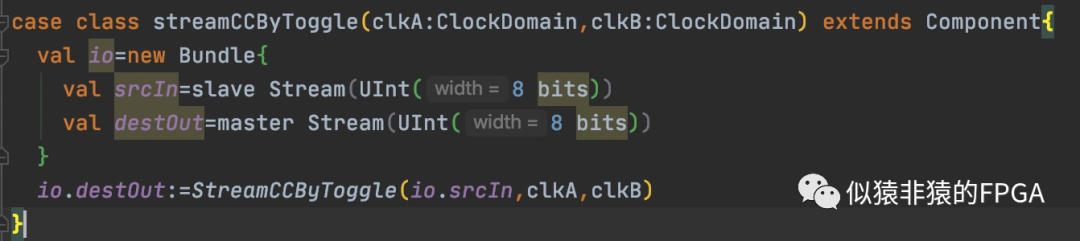

對于吞吐要求不是特別高的場合,跨時鐘域信號采用握手形式 進行處理也是一種不錯的選擇。SpinalHDL有兩個抽象類型個人一直很喜歡:Stream,Flow。這兩種形式基本囊括了所有的信號交互行為,其也可以說是SpinalHDL lib庫的基石。針對跨時鐘域的握手處理,SpinalHDL有一個StreamCCByToggle可以使用:

StreamCCByToggle(input: Stream[T], inputClock: ClockDomain, outputClock: ClockDomain): Stream[T]

其輸入參數包含源時鐘域信號,源時鐘域,目的時鐘域,其返回一個目的時鐘域的Stream信號:

這里srcIn隸屬于時鐘域clkA,destOut隸屬于時鐘域clkB。 除了StreamCCByToggle,SpinalHDL里還有一個FlowCCByToggle。由于Flow類型沒有反壓,因而從低時鐘域向高時鐘域進行傳輸則沒什么問題,但從高時鐘域向低時鐘域進行轉換則存在丟失數據的風險。》》FIFO跨時鐘域緩存 對于高吞吐的多比特信號跨時鐘域處理,則往往采用FIFO的形式進行處理。在SpinalHDL里則有StreamFifoCC供使用:

val myFifo = StreamFifoCC( dataType = Bits(8 bits), depth = 128, pushClock = clockA, popClock = clockB)myFifo.io.push 《《 streamAmyFifo.io.pop 》》 streamB

編輯:lyn

-

電路設計

+關注

關注

6665文章

2426瀏覽量

203300 -

計數器

+關注

關注

32文章

2253瀏覽量

94351 -

時鐘域

+關注

關注

0文章

52瀏覽量

9528

原文標題:跨時鐘域那點事兒

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

極限失控的大模型使電力系統面臨的跨域攻擊風險及應對措施

單芯片運行六個操作系統,芯馳科技交卷跨域融合

航盛與高通發布全新一代墨子艙駕跨域融合平臺

利用LWIP實現的Web server,如何修改響應報文中HTTP header里面的Access-Control-Allow-Origin的值?

黑芝麻智能與斑馬智行達成單芯片跨域融合平臺項目合作

介紹一個IC設計錯誤案例:可讀debug寄存器錯誤跨時鐘

關于跨時鐘域的詳細解答

關于跨時鐘域的詳細解答

評論