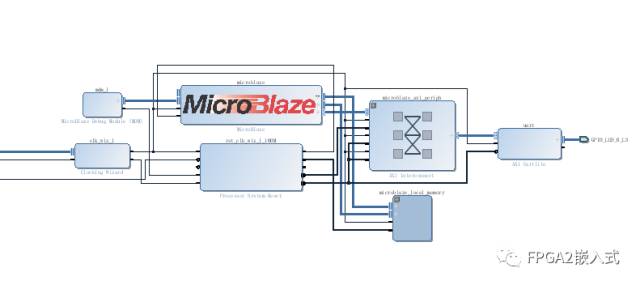

在一個項目中,當你使用microblaze作為控制器來進行系統調度的時候,一般是建議將所有模塊封裝成AXI形式的IP核,這樣好管理,也容易調試。不過在初期的時候是不建議這樣做的,因為你的模塊并沒有完全被驗證是沒問題的,所以還是使用.v文件,等后面這一功能驗證通過,再把它封裝成IP核形式。

1. AXI IP核簡介

用過Microblaze或者看例程的人肯定都知道,Xilinx提供了很多AXI形式的IP核,像常用的UART、IIC、SPI等IP核。我們只要把他們在畫布里調出來,然后使用自動連接形式,便能把對應接口連接起來,接著在軟件上調用其相應的函數便可以工作了。

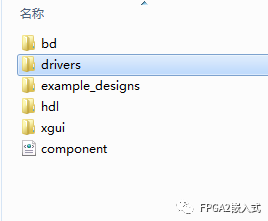

但是當我們自己封裝了一個AXI形式的IP核后,又該怎么去使用呢?這不是官方IP,沒有相應的函數呀?不知道大家是否有印象,上一篇文章介紹IP封裝的時候說過,封裝成AXI形式的IP核,會生成一些東西,如下圖所示,這個可千萬別去刪,大有用處的。

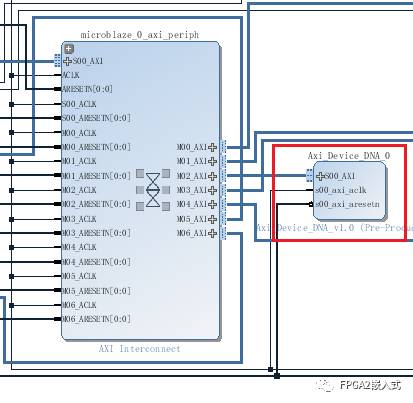

里面的drivers這個文件夾其實放的就是AXI的驅動函數。例如我們生成一個AXI的IP核(紅框處)

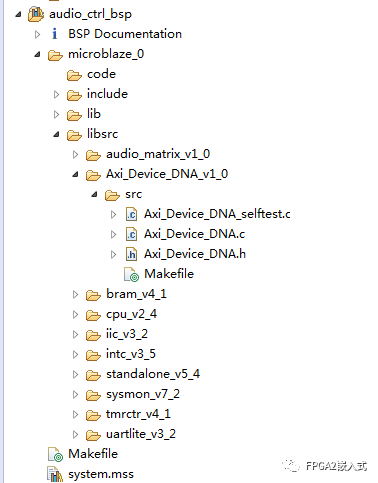

編譯通過后生成軟核工程,可以看到,我們自己加入的IP核是有被關聯進來的。在“Axi_Device_DNA_v1_0”這個文件夾下包含有.c和.h文件,這個就是我們添加的IP核對應的驅動,它和iic、定時器、uart等IP核在同一個庫里。這些都是IP核必須使用到的函數文件。

2. AXI IP核使用

看見自制的IP核都能給你生成驅動函數是不是覺得很高級,很爽呢!如果這樣想那你就確實too young too simple了。打開它的.c和.h文件給你看看吧。

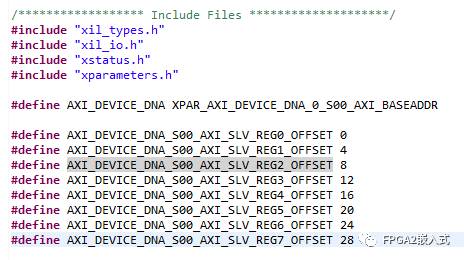

寄存器定義

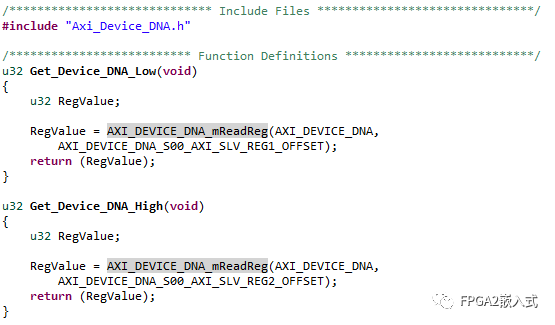

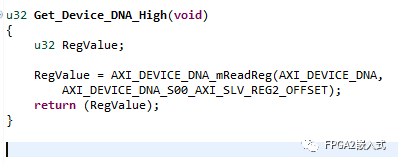

獲取DNA數據高位、低位數據的函數

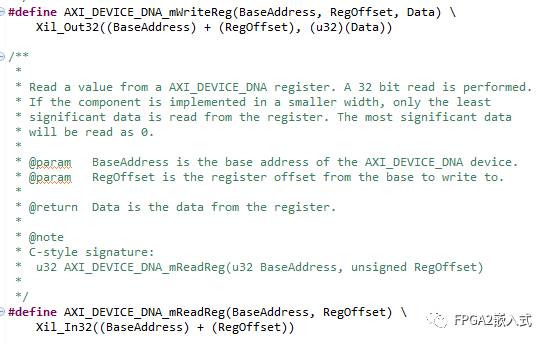

讀寫函數

是的,就只有這些,沒有了!所以別以為能像IIC之類的IP核一樣,會給你很全的函數,讓你一次寫一大串或讀一大串數據的,如果真能根據不同IP功能給你定制不同函數,那就智能到逆天了···

不過人家都給你讀寫寄存器的函數和寄存器的定義,也就已經夠了,都說下層基礎決定上層建筑,有了這兩個基本函數,你想自己做什么功能還不行?MCU控制的本質不也就是讀寫對應的寄存器,偷懶也得有個度的哈哈~就像這樣,自己封裝個函數就行了。

當然,你也可以不用Xilinx給你生成的讀寫函數,自己寫也是可以的,不過不建議這么做,畢竟人家都給了,一方面可以給你節省編碼時間,另一方面也保證了函數的穩定性,避免開發出錯。

3. 總結

在封裝成AXI IP 核時會有一個頂層的AXI時序代碼,這個用戶一定要熟悉,并且對應的寄存器要設置好,這樣使用起來才不會有錯誤。不然容易出現寄存器讀寫不成功或者操作錯寄存器導致數據不對。總之還是一句話,實踐出真知,想了解深入得去用了才知道才會使用。

編輯:lyn

-

Xilinx

+關注

關注

71文章

2163瀏覽量

121005 -

MicroBlaze

+關注

關注

3文章

68瀏覽量

21533 -

IP核

+關注

關注

4文章

326瀏覽量

49428

原文標題:使用MicroBlaze調用AXI IP核

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

芯驛電子 ALINX 推出全新 IP 核產品線,覆蓋 TCP/UDP/NVMe AXI IP 核

Xilinx DDS IP核的使用和參數配置

MicroBlaze V軟核處理器的功能特性

基于TI Sitara系列AM5728工業開發板——FPGA視頻開發案例分享

esp32在靜態IP下,域名無法解析怎么解決?

關于FPGA IP核

FPGA優質開源模塊-SRIO IP核的使用

如何使用MicroBlaze調用AXI IP核詳細解析

如何使用MicroBlaze調用AXI IP核詳細解析

評論