Xilinx提供超低延時編解碼方案,在ZCU106單板上可以驗證。文檔MPSoC VCU TRD 2020.2 Low Latency NV16 提供了詳細命令。

下面的命令,能表現得更加穩定。

注意,其中每行最后的,表示本行沒有結束,下一行也是本行內容。一定要保證最后的后面,沒有任何字符,要注意不能有空格字符。

發送端命令:

gst-launch-1.0 -v v4l2src device=/dev/video0 io-mode=4

! video/x-raw(memory:XLNXLL), format=NV16, width=3840, height=2160, framerate=60/1

! omxh265enc num-slices=8 periodicity-idr=240 cpb-size=500 gdr-mode=horizontal

initial-delay=250 control-rate=low-latency prefetch-buffer=true

target-bitrate=25000 gop-mode=low-delay-p

! video/x-h265, alignment=nal ! queue max-size-buffers=0 ! rtph265pay

! udpsink buffer-size=60000000 host=127.0.0.1 port=5004 async=false

max-lateness=-1 qos-dscp=60 max-bitrate=120000000 -v

在執行上述命令前,需要配置視頻輸入pipeleine為4K的NV16模式,并根據接收單板指定其中的IP。

接收端命令:

gst-launch-1.0 udpsrc port=5004 buffer-size=60000000

caps=application/x-rtp, media=video, clock-rate=90000, payload=96, encoding-name=H265

! rtpjitterbuffer latency=17 ! rtph265depay ! h265parse

! video/x-h265, alignment=nal ! omxh265dec low-latency=1 internal-entropy-buffers=5

! video/x-raw(memory:XLNXLL) ! queue max-size-bytes=0

! fpsdisplaysink name=fpssink text-overlay=false video-sink=kmssink bus-id=a00c0000.v_mix sync=true -v

原文標題:【工程師分享】ZCU106的超低延時gstreamer編解碼命令

文章出處:【微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

Xilinx

+關注

關注

71文章

2163瀏覽量

121004

原文標題:【工程師分享】ZCU106的超低延時gstreamer編解碼命令

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

Multi-Scaler IP的Linux示例以及Debug(上)

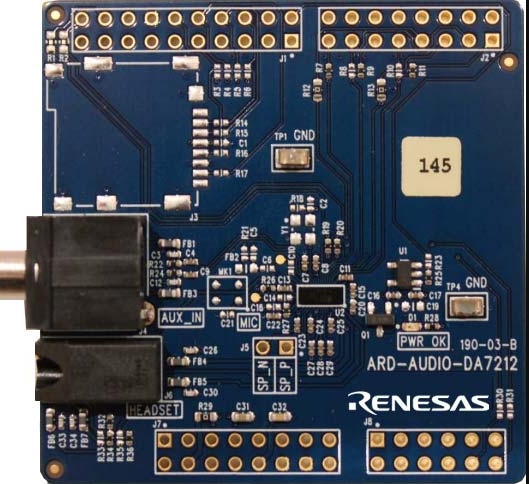

超低功耗立體聲編解碼器Arduino評估板ARD-AUDIO-DA7212數據手冊

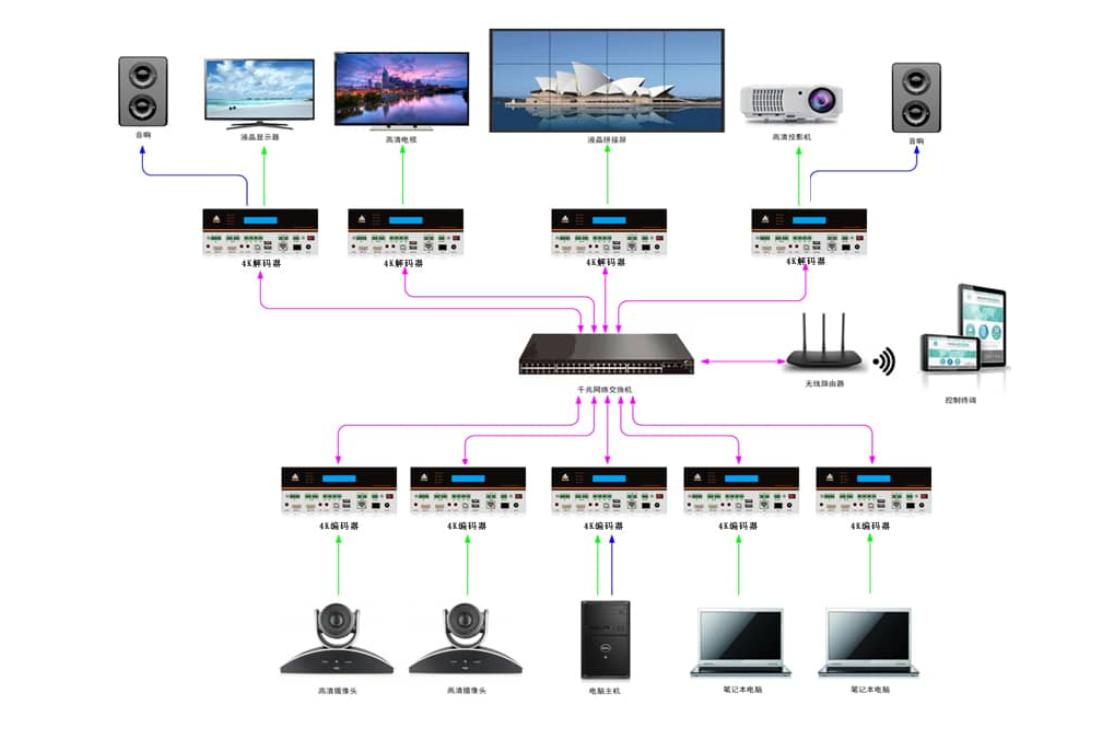

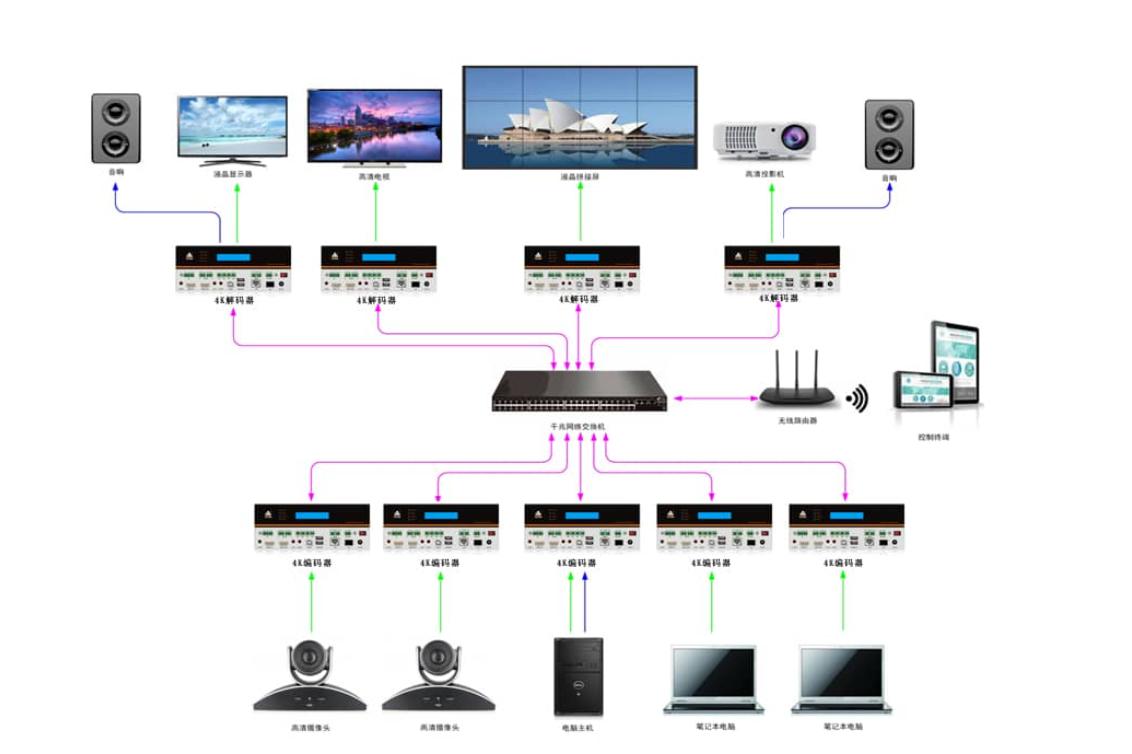

千視電子攜手AMD 優化 NDI 和 NDI|HX 編解碼解決方案

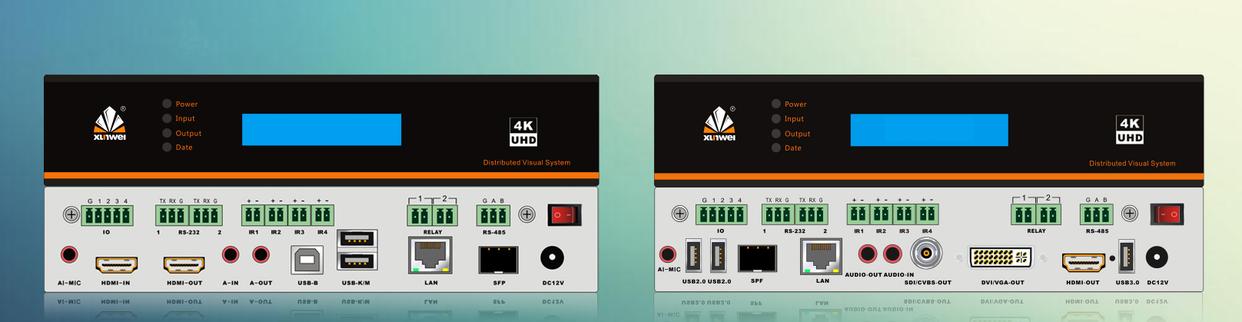

編解碼一體機的主要應用場景是什么?

編解碼一體機相對于傳統的編解碼設備有哪些優勢?

編解碼一體機:技術、應用與挑戰

音頻處理的新選擇:編解碼一體機

什么是編解碼一體機?

Xilinx提供在ZCU106單板上可以驗證的超低延時編解碼方案

Xilinx提供在ZCU106單板上可以驗證的超低延時編解碼方案

評論