雷擊是常見的物理現象,也是電源適配器最主要的電壓應力來源。如果防護不當會造成電源損壞或重啟,從而影響電子設備正常工作,因此電源適配器需滿足安規標準定義的雷擊電壓等級要求。

本期芯朋微技術團隊將為大家分享雷擊標準、雷擊實驗配置、差模及共模干擾路徑分析和設計原則。

雷擊標準

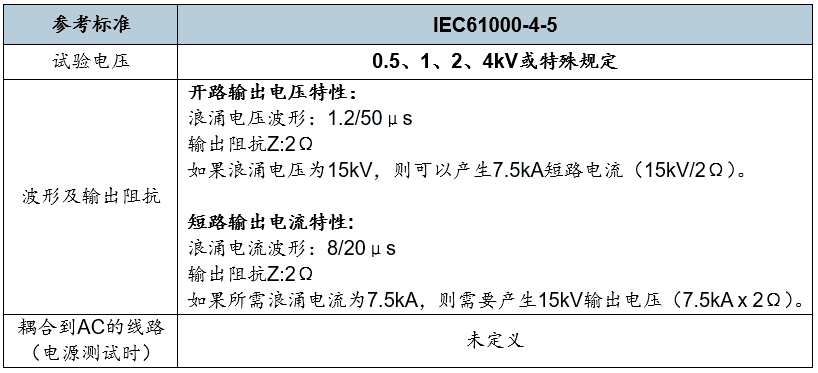

IEC61000-4-5為常用的雷擊測試標準,其定義及實驗規程如下:

一般情況下,在交流線路上施加±1kV~±6kV的浪涌電壓。試驗源為測試設備(EUT)的交流線路和系統外殼的接地點。測試過程中,EUT直接暴露在浪涌能量下,必須完好無損,雷擊測試完成后,還能繼續正常工作。

雷擊實驗的配置

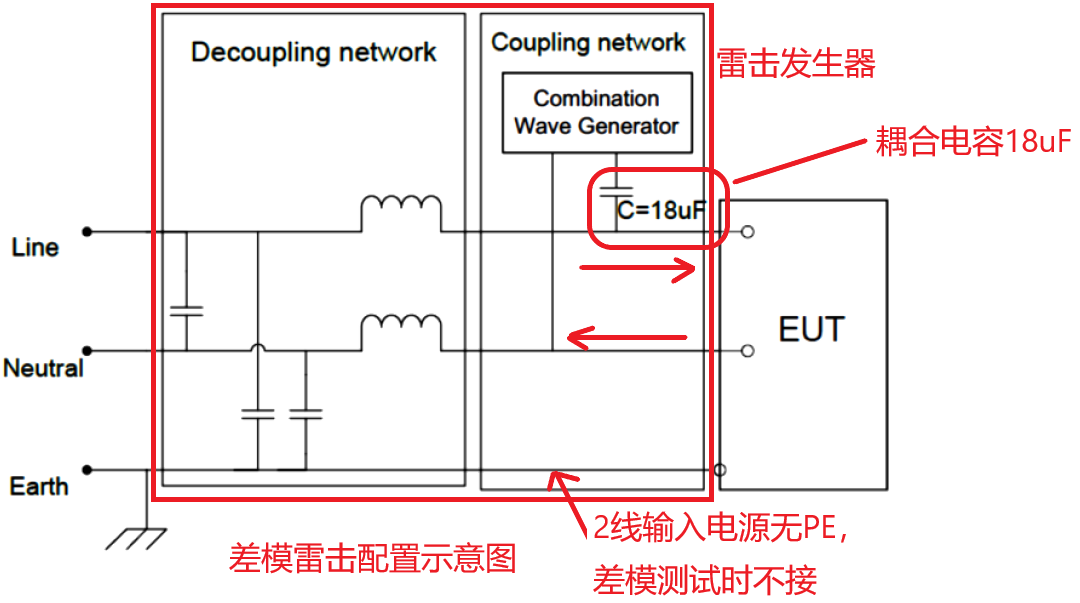

圖3 差模雷擊配置示意圖

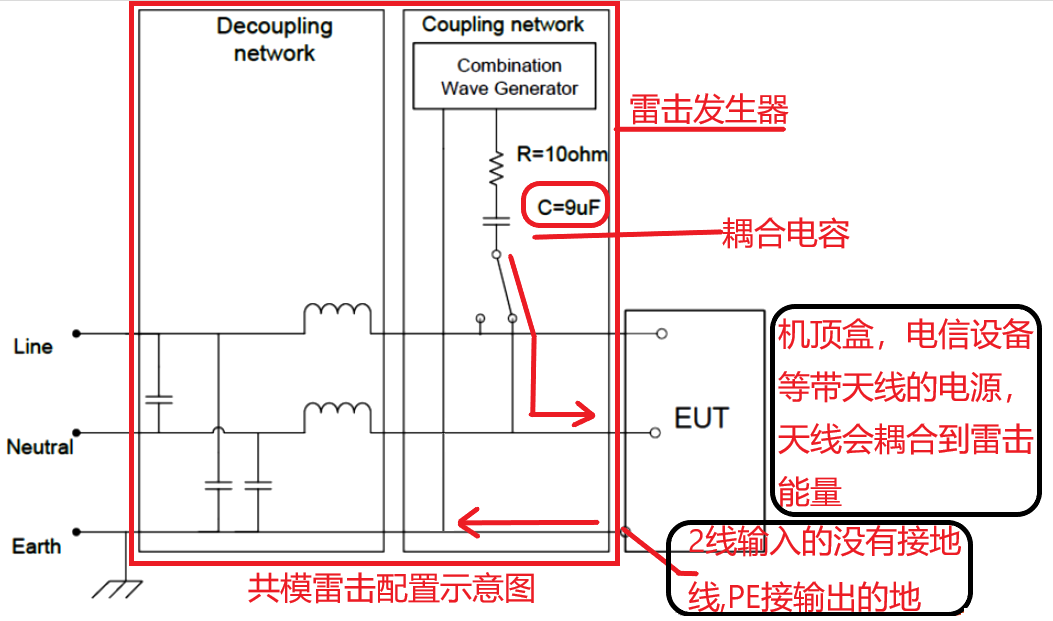

圖4 共模雷擊配置示意圖

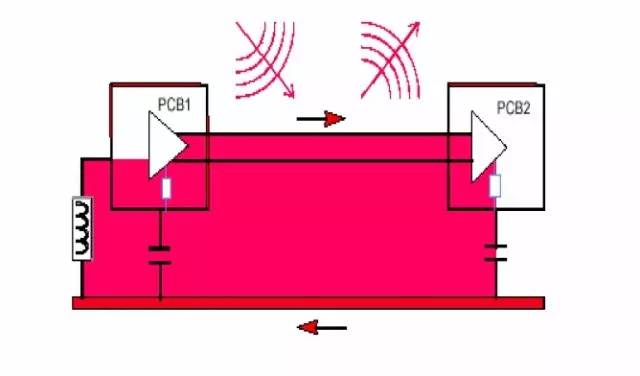

雷擊發生器內部有2個模塊,分別是解耦網絡和耦合網絡。解耦網絡的作用是將耦合網絡施加到EUT相線上的雷擊能量與供電的相線隔離開。耦合網絡的作用是通過耦合電容將理想的雷擊發生波施加到EUT的相線上。

如圖3所示:差模雷擊的耦合能量在EUT的相線L和N之間傳遞。而通過圖4可以發現共模雷擊的耦合能量在EUT的相線L(N)和PE之間傳遞。

差模干擾路徑分析及設計原則

路徑分析

圖5 差模雷擊電流示意圖

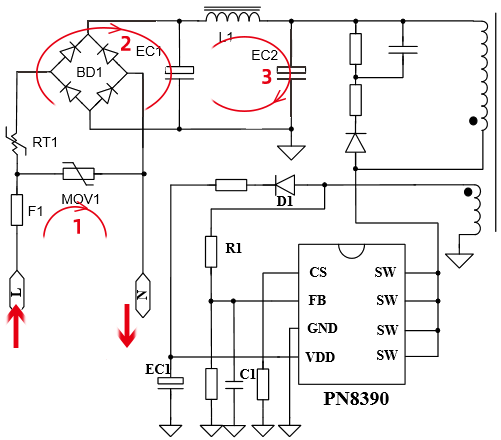

由于不同的實際電路配置會對系統差模雷擊分析產生不同影響,因此,我們通過上圖電路對差模雷擊的影響做一個簡要的分析。

差模雷擊能量通過耦合網絡,輸入EUT的相線L和N,保險絲F1,和壓敏MOV1形成回路1,產生差模電流1;

差模雷擊能量通過回路1衰減后,經熱敏電阻RT1,整流橋,電解電容EC1形成回路2,產生差模電流2;

差模雷擊能量通過回路1和2衰減后,經差模電感L1,電解電容EC2形成回路3,產生差模電流3。

設計原則

MOV1的加入可以吸收差模電流1的能量,保護整流橋BD1和電解電容EC1和EC2。回路1相當于雷擊浪涌能量的第1道防洪壩,由于該回路電流較大,PCB銅箔寬度建議0.5mm/kV;

高阻值的負溫度系數熱敏電阻RT1的加入可以分擔差模電流2施加到EC1上的能量,保護整流橋BD1和電解電容EC1,回路2相當于第2道防洪壩;

輸入差模電感的阻抗可以分擔差模電流3施加到EC2上的能量,回路3相當于第3道防洪壩,由于EC2上存在幾百伏的雷擊能量殘壓,所以原邊功率管建議采用高雪崩耐量功率MOSFET。

【專家帖】如何提高開關電源芯片MOSFET雪崩可靠性?

實驗結果

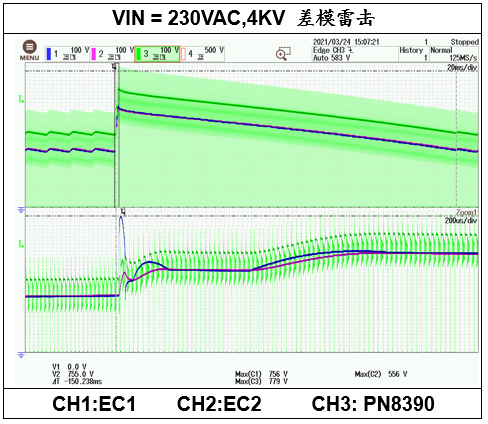

基于PN8390的12V1.5A適配器,4kV(90°)差模雷擊測試如下圖所示:

圖6 4kV差模雷擊測試波形圖

由測試波形可見:EC1最高電壓756V,EC2最高電壓556V,PN8390最高電壓779V。因此,為提高電源適配器的抗差模雷擊能力,除合理選擇MOV和NTC電阻外,應選擇高鋁箔電壓電解電容和高雪崩耐量功率MOSFET。

共模干擾路徑分析及設計原則

路徑分析

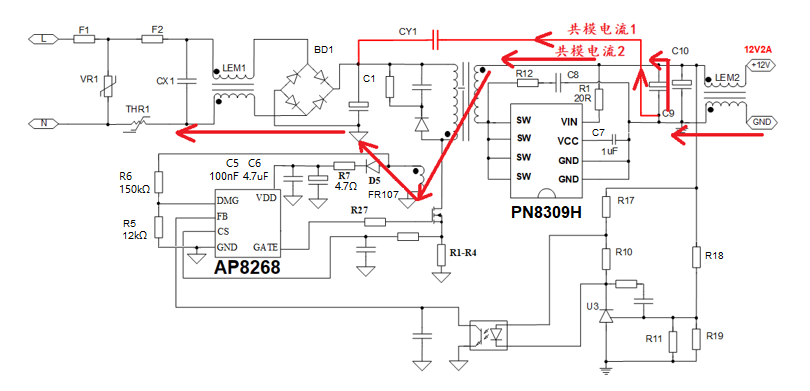

圖7 雷擊共模電流的流向圖

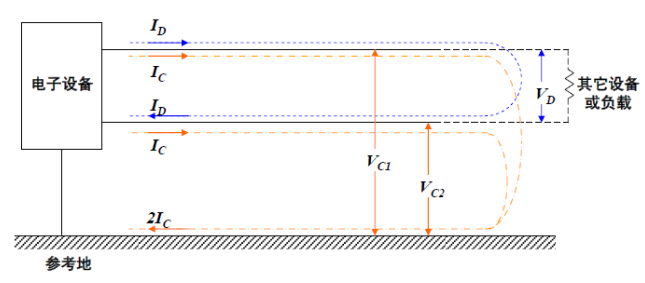

共模雷擊發生時兩路主要的共模電流路徑(以負電壓為例):

共模電流1:雷擊能量施加到輸出的地,通過輸出共模電感→次級參考地→CY1→輸入電解電容的正→整流橋→輸入共模電感→L線或N線。

共模電流2:雷擊能量施加到輸出的地,通過輸出共模電感→次級參考地→輸出電解的正→變壓器→輔助繞組的地→輸入電解電容的負→整流橋→輸入共模電感→L線或N線。

設計原則考慮共模電流路徑因素,優化PCB布線:輸入共模和Y電容增加放電針,原邊控制器的地與變壓器的地分別接到輸入電解電容負極,同步整流芯片的地與Y電容的地分別接到輸出電解電容負極;

為了防止共模電流干擾同步整流芯片,優先選用雙供電同步整流芯片,如PN8309H,并在Vin腳串聯10~22Ω電阻;

為了防止共模電流干擾原邊主控芯片,應在Vdd供電回路串聯電阻,將Vdd電解電容緊靠芯片引腳,并增加100nF去耦電容。

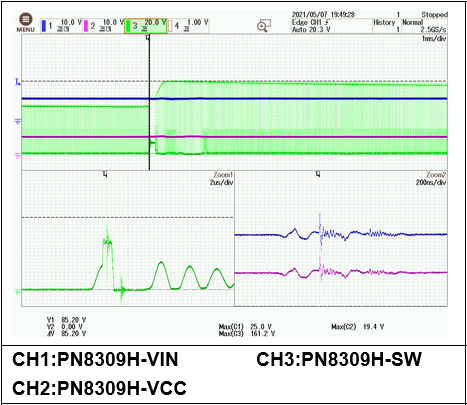

實驗結果基于PN8309H的12V3A適配器6.6kV共模雷擊測試如下圖所示:

圖8 6.6kV共模雷擊測試波形圖

由測試波形可見,PN8309H的SW、Vin、Vcc電壓分別為161V、25V、19V。因此,為提高電源適配器的抗共模雷擊能力,除合理Layout和增加濾波電容外,優先選用雙供電及集成高雪崩耐量MOSFET的同步整流芯片。結束語

電源抗雷擊能力設計是困擾不少電源工程師的難題之一,最佳的設計原則是合理的PCB走線,加上更優的器件選型。一旦出現雷擊失效,則需要從失效瞬態工作波形入手,結合原理分析和器件特性,找出根因并加以改善。

原文標題:【干貨】電源適配器雷擊設計寶典

文章出處:【微信公眾號:芯朋微電子】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

電源

+關注

關注

184文章

17573瀏覽量

249482

原文標題:【干貨】電源適配器雷擊設計寶典

文章出處:【微信號:chipown,微信公眾號:芯朋微電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

雷擊實驗配置、差模及共模干擾路徑分析和設計原則分享

雷擊實驗配置、差模及共模干擾路徑分析和設計原則分享

評論