1 MAX121芯片的性能與特點

MAX121芯片是一個帶串行接口的14位模數轉換集成電路(ADC),它包含有跟蹤/保持電路 的一個底飄溢、底噪聲、掩埋式齊納電壓基準電源。它的轉換速度快、功率消耗底、采樣速率高達308 ks/s點,滿量程輸入電壓范圍為±5V,功耗為210 mW。可與大多數流行的數字信號處理器的串行接口直接接口,該輸入可以接收TTL或CMOS的信號電平,時鐘頻率為0.1-5.5MHz。

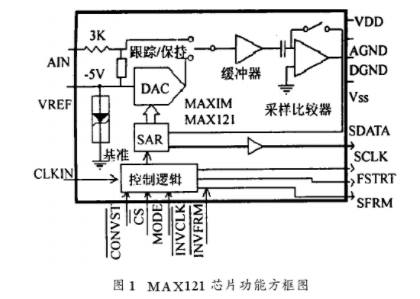

MAX121芯片的功能方框圖如圖1所示。它有16腳和20腳模式,16腳有DIP和SO封裝,20腳有 SSOP封裝。特點如下:

14位分辨率;2.9 μS轉換時間/308 ks/s吞吐率;400 ns采樣時間;底噪聲和低失真:78Db SINAD -85Db THD;±5V雙極性輸入范圍,可時承受±15V的過電壓;210 mW功耗;可用連續轉換模式;30 ppm/C,-5V內部基準源;與DSP處理器接口;16腳DIP和SO封裝,20腳SSOP封裝。

極限參數:VDD對DGND 0.3-+6V;VSS對DGND +0.3--7V;AIN對AGND±15V;AGND對DGND ±0.3V數字輸入對DGND(CS,CONVST,MODE,CLKIN,INVCLK,INVFRM);-0.3(Vdd+0.3V);數字輸出對DGND(SFRM,FSTRT,SCLK,SDATA )+0.3(Vdd+0.3V);連續功率消耗(TA=+70 ℃)

強度超出上述極限參數可能導致器件的永久性損壞。這些僅僅是極限參數,并不意味著在極限參數條件下,或在任何其他超出技術規范規定的工作條件下,器件能有效地工作。延長在極限參數條件下的運行時間,會影響器件的可靠性。

2 工作電路

MAX121運用逐次比較技術和跟蹤/保持(T/H)電路,將模擬信號轉換為14位串行數據輸出 碼。其控制邏輯接口很容易與大多數微處理器(霵)和數字信號處理器(DSP)相連接,在大多數應用中只需要很少幾個無源元件。T/H電路不需要外接電容。

2.1 模擬輸入跟蹤與保持

根據等效輸入電路分析,給出ADC的模擬比較器的采樣結構。內部緩沖器給保持電容充電,以減小轉換期間所要求的采集時間。模擬輸入端呈現6k輸入電阻及與其并聯的10pF電容。

在兩次轉換之間,緩沖器輸入通過輸入電阻連接到AIN端。當轉換開始時,緩沖器與AIN端 斷開,對輸入信號采樣。在轉換結束時,緩沖器輸入端又連接到AIN端,而且保持電容跟蹤 輸入電壓。無論何時,只要轉換沒有進行,T/H就處于跟蹤模式。在轉換開始以后,保持模 式啟動時間接近10 ns(窗口延遲)。從一次轉換到下一次轉換延遲變化的典型時間為30 ps(窗口抖動)。

2.2 電路時鐘頻率

MAX121工作時需要一個與TTL,CMOS電平兼容的時鐘,時鐘頻率的范圍從0.1-5.5 MHz。為滿足2個時鐘周期400 ns采集時間的要求,最大時鐘頻率限制在5MHz。由于內部T/H 電壓下降速率的限制,所有模式的時鐘頻率不應低于0.1MHz。

2.3 輸出數據格式

轉換結果以16位串行數據流輸出,前14位為數據位(首先為MSB),后2位為零。輸出數據 為二進制補碼形式。在CLKIN的上升沿,數據在SDATA端同步輸出。

輸出數據可用FSTRT或者SFRM輸出來分幀。FSTRT(平常為低)低于MSB1個時鐘周期變為高。FSTRT的下降沿SDATA端輸出MSB。

SFRM輸出(當INVFRM=Vdd時通常為高)變為低的同時,MSB出現在SDATA端。16個時鐘周期以后 SFRM變為高電平。通過輸入接到數字地,可反轉SFRM的極性。要求每次轉換最少為18個時鐘周期,以獲得有效SFRM輸出。

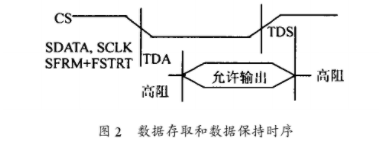

如果有幾個器件共用串行總線,可以參看圖2的數據存取和數據保持時序。

3 TMS320高速串行接口

3.1 上電后的初始化

如果滿足下列條件,上電后MAX121的首次轉換將是有效的。提供16個時鐘脈沖使T/H進入跟蹤模式,再加上跟蹤模式中數據采集的最小時間400 ns。確保基準源已經穩定。每1μF基準源旁路電容的穩定時間是0.5 ms(對22μF電容為11ms)。

3.2 串行時鐘最大速率

與數字信號處理器接口時,MAX121的串行時鐘最大速率取決于處理器的串行數據輸入所要 求的最小建立時間和ADC的時鐘與數據的最大延遲時間。MAX121有兩種方法將數據讀入處理器。 CLKIN是MAX121的輸入時鐘,而SCLK是使數據移位進入處理器的串行時鐘,支持異步數據傳輸的場合。tSU是處理器串行數據輸入端所要求的數據建立最小時間;tCD是MAX121的CL KIN到SCLK最大延時時間;tSC是MAX121的SCLK到SDATA的最大延時時間。MAX121 的SCLK輸出驅動處理器的串行接口,此時可從以上議程中去掉tCD項,并允許使 用更快的時鐘頻率。在這種情況下,串行時鐘最大速度由下式計算:

fCLKIN=1/2(tSU+tSC)

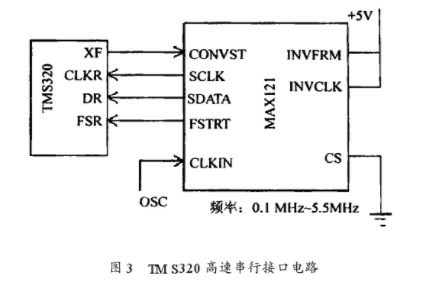

3.3 高速數據串行接口

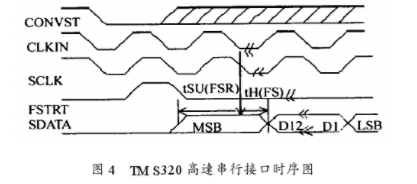

MAX121的靈活性使它可以與德州儀器公司TMS320的各種串行接口連接。高速接口可使MAX121/TM320系統獲得最大的數據吞吐率,此時MAX121工作在它的最快時鐘。圖3示出了完成這種 接口所需的連線。圖4為接口的時序圖。

MAX121的CLKIN由外部時鐘振蕩器驅動。TMS320的XF0 I/O口驅動MAX121輸入端為低,啟動 一次轉換。TMS320的CLKR(接收時鐘)端配置為輸入,并由 MAX121的SCLK輸出端驅動。MAX 121的SDATA輸出端數據在時鐘的上升沿改變狀態,而在時鐘下降沿,數據被鎖存到TMS320的 DR輸入端。這樣可提供1/2個時鐘周期,以滿足TMS320DR輸入端所需要的數據建立和保持時間。 MAX121SCLK和SDATA之間的最大時滯在+25時為65ns,所以1/2個時鐘周期足以滿足要求的建立和保持時間。

MAX121的FSTRT輸出驅動TMS320的FSR輸入,以對數據分幀。FSTRT輸出的下降沿指示MSB已準備好,可被鎖存。在下一個時鐘下降沿,MSB被鎖存在TMS320。使用這種接口,TMS320可接收16位字(在TMS320串行口整體控制寄存器中,RLEN=01),于是14位數據被時鐘同步移入DSP,同時跟隨兩位尾隨的0。

4 結論

近幾年來,隨著便攜式、手提式電子產品的日益增多,MAXIM系列產品的應用也越來越廣 泛,這里詳細介紹了MAX121芯片在數字信號處理高速串行接口電路方面的應用。同時MAX121集成電路也在語言識別和合成、DSP伺服合成、頻譜分析等領域都有廣泛的應用。

編輯:jq

-

芯片

+關注

關注

454文章

50444瀏覽量

421935 -

集成電路

+關注

關注

5382文章

11393瀏覽量

360919 -

CMOS

+關注

關注

58文章

5687瀏覽量

235162 -

TTL

+關注

關注

7文章

502瀏覽量

70140

發布評論請先 登錄

相關推薦

SOC芯片在汽車電子中的應用

串行接口PCB設計指南:優化布局與布線策略

DRV8332芯片在調試的過程中,輸出始終達不到24V,為什么?

6芯M16接口的應用探析

FPGA的sata接口設計時需要注意哪些問題

高速串行總線有哪些

高速串行收發器原理及芯片設計

串行音頻接口(SAI)中slot是什么意思?

深入探析:DLT8P68SA主控芯片在無線剪毛器中的應用

探析MAX121芯片在高速串行接口電路中的應用

探析MAX121芯片在高速串行接口電路中的應用

評論