1 引言

隨著網(wǎng)絡(luò)的迅速發(fā)展.嵌入式系統(tǒng)的應(yīng)用日益廣泛.不僅PC機(jī)能上網(wǎng),而且各種各樣的嵌入式設(shè)鋸都可以上網(wǎng),能上網(wǎng)的嵌入式設(shè)備需要加上TCP/IP網(wǎng)絡(luò)協(xié)議,這也對(duì)檢測(cè)電力系統(tǒng)運(yùn)行狀況的儀器設(shè)備提出更高的要求。嵌入式系統(tǒng)以其內(nèi)核小、專用性強(qiáng),系統(tǒng)精簡(jiǎn)、高實(shí)時(shí)性等特點(diǎn),在各領(lǐng)域取得廣泛應(yīng)用,因此嵌入式設(shè)備網(wǎng)絡(luò)化是迄今科技發(fā)展的趨勢(shì)。

在現(xiàn)今經(jīng)濟(jì)社會(huì)中,電力負(fù)荷急群增大,諧波對(duì)電力系統(tǒng)的污染越來(lái)越嚴(yán)重,且是目的電網(wǎng)中影響最為重要的一項(xiàng)指標(biāo)。本文建立在基于ARM的電壓諧波智能監(jiān)測(cè)及消諧裝置的實(shí)例研究基礎(chǔ)上,重點(diǎn)闡述基于ARM7內(nèi)核的STR710處理器的嵌入式以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)。

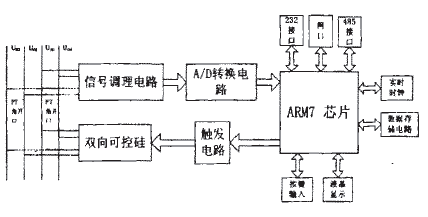

2 基于ARM的電壓諧波智能監(jiān)測(cè)及消諧裝量的結(jié)構(gòu)框圖及工作原理

本裝置主要結(jié)構(gòu)包括:開關(guān)電源模塊、信號(hào)采樣調(diào)理電路,A/D轉(zhuǎn)換電路、實(shí)時(shí)時(shí)鐘電路、數(shù)據(jù)存儲(chǔ)電路、網(wǎng)口電路、人機(jī)交互漫示電路和ARM7控制器等幾部分。系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

圖1結(jié)構(gòu)框圖(strueture)

兩路被測(cè)信號(hào)經(jīng)過(guò)電壓互感器的采集,然后經(jīng)信號(hào)調(diào)理和A/D轉(zhuǎn)換器變?yōu)樾枨蠓秶?a target="_blank">數(shù)字信號(hào)送ARM7處理。ARM芯片利用FFT變換可計(jì)算出各路電壓有效值,2~32次諧波含量,再參照電網(wǎng)電壓諧波標(biāo)準(zhǔn)進(jìn)行相應(yīng)處理。如果是高次諧波就立即觸發(fā)雙向可控硅導(dǎo)通,在切除時(shí)只要撤銷觸發(fā)信號(hào)即可.開關(guān)在電流過(guò)零之后會(huì)自行關(guān)斷。這樣,ARM7就可以有效控制可控硅的導(dǎo)通及導(dǎo)通時(shí)間,消除有害諧波。

電壓信號(hào)的采集對(duì)電網(wǎng)頻率的任何電能質(zhì)量參數(shù)的精確測(cè)量都十分關(guān)鍵。在監(jiān)測(cè)儀中采用精密電壓互感器,將輸入端信號(hào)轉(zhuǎn)化為毫安級(jí)的電流信號(hào),經(jīng)過(guò)電阻取得電壓信號(hào)。信號(hào)調(diào)理電路由電壓跟隨電路、全波整流、鎖相環(huán)電路和分頻電路組成。其中鎖相環(huán)電路和分頻電路是保持信號(hào)的同步,以便準(zhǔn)確的測(cè)量諧波。由于本監(jiān)測(cè)儀足對(duì)兩路信號(hào)進(jìn)行監(jiān)測(cè),每路需要在20ms內(nèi)采樣256個(gè)點(diǎn)的數(shù)據(jù),這對(duì)A/D芯片速度有更高的要求。該監(jiān)測(cè)儀A/D轉(zhuǎn)換芯片采用最大采樣頻率為750kHz的AD7492。

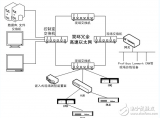

消諧裝置主要利用雙向可控硅組件,直接動(dòng)作于電壓互感器的開口三角繞組。通信部分主要有232、485和網(wǎng)口形式。電壓諧波計(jì)算由ARM芯片采用FFT算法完成。本文的ARM7芯片選用的是ST公司的STR710。ARM7以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn),采用STR710微控制器與以太網(wǎng)控制芯片CS8900A進(jìn)行硬件設(shè)計(jì),通過(guò)TCP/UDP協(xié)議進(jìn)行通訊。

ARM7芯片通過(guò)和CS8900A控制器的以太網(wǎng)接口的設(shè)計(jì)和實(shí)現(xiàn),可以實(shí)現(xiàn)對(duì)活潑的在線監(jiān)測(cè)及消除。對(duì)電力系統(tǒng)的維護(hù)具有十分重要的意義。

3 STR710簡(jiǎn)介

STR710是基于16/32位ARM7TDMI的微控制器。STR710的特點(diǎn)包括:支持32位/16位RISC體系結(jié)構(gòu)(ARM v4T)。片內(nèi)集成flash和高達(dá)64KB的RAM存儲(chǔ)器。擁有4個(gè)外部存儲(chǔ)器接口(EMI)。32位ARM指令集和16位Thumb指令集。擁有非復(fù)用的16位數(shù)據(jù)和24位地址總線。STR710集成了許多標(biāo)準(zhǔn)的接口,包括USB-Device、4個(gè)UART、10Base-T以太網(wǎng)控制器等。STR710還集成了JTAG-ICE、UART調(diào)試通道(DBUG)的調(diào)試功能。

4 CS8900A以太網(wǎng)控制器

CS8900A以太網(wǎng)控制器是由Cirrus Logic公司出的一款低成本的以太網(wǎng)控制芯片,集成了IEEE802.3協(xié)議標(biāo)準(zhǔn)的介質(zhì)訪問(wèn)控制子層(MAC),并且支持全雙工操作。不僅具有其它以太網(wǎng)控制器芯片所具有的基本功能外,還有自己獨(dú)特優(yōu)點(diǎn):優(yōu)化于工業(yè)標(biāo)準(zhǔn)體系結(jié)構(gòu)(ISA);獨(dú)特的PacketPage結(jié)構(gòu)可自動(dòng)適應(yīng)網(wǎng)絡(luò)通信模式的改變,占用系統(tǒng)資源少,從而增加系統(tǒng)效率;高度集成的設(shè)計(jì),適合作為智能嵌入式設(shè)備網(wǎng)絡(luò)接口。在本文設(shè)計(jì)

中,CS8900A用作I/O模式,其特點(diǎn)是占用系統(tǒng)資源少,硬件連接方便。

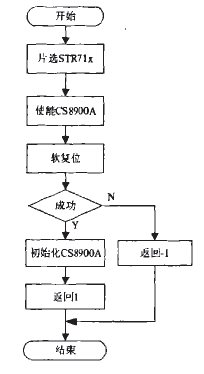

本設(shè)計(jì)采用的是STR710和CS8900A組成的以太網(wǎng)接口方案。軟硬件系統(tǒng)結(jié)構(gòu)如圖2所示:

圖2系統(tǒng)結(jié)構(gòu)圖(figure2:system structure)

5 硬件電路

結(jié)合STR710微處理器和CS8900A各自的特點(diǎn),構(gòu)成的嵌入式以太網(wǎng)接口的連接硬件原理圖如圖3所示。

(1)CS8900A端的讀信號(hào)(IOR非)通過(guò)或門(74HC32)與STR710的讀信號(hào)(RD)和片外存儲(chǔ)器CS1(bank1)相連。

(2)CS8900A端的寫信號(hào)(lOW非)通過(guò)或門(74HC32)與STR710的寫信號(hào)(WEO)和片外存儲(chǔ)器CS1(bank1)連接。

(3)數(shù)據(jù)總線D0-D15對(duì)應(yīng)相連用于16位數(shù)據(jù)傳輸。

(4)CS8900A地址總線(SA1-SA3)對(duì)應(yīng)STR710(A12-A14)相連,CS8900A的地址總線SA0和系統(tǒng)總線使能(SBHE非)與STR710的地址總線A11相連。

(5)復(fù)位信號(hào)對(duì)應(yīng)相連。

圖3硬件連接原理圖(figure3.hardware connection principle)

6 軟件實(shí)現(xiàn)

6.1驅(qū)動(dòng)模塊CS8900程序設(shè)計(jì)

本文采用的是CS8900A的I/O模式。CS8900驅(qū)動(dòng)模塊程序包括以下內(nèi)容:

(1)設(shè)定以太網(wǎng)物理地址,可在初始化CS8900前修改。(2)定義接收幀類型,以太網(wǎng)數(shù)據(jù).地址端口(3)設(shè)置工作模式,8位或16位模式。本設(shè)計(jì)采用16位模式,本文中將CS8900中的SBHE非和SA0都與STR710的地址總線A11相連,使其工作在16位模式。設(shè)定數(shù)據(jù)包收發(fā)過(guò)程中所用寄存器以及中斷方式。(4)發(fā)送幀請(qǐng)求.初始化CS8900.?dāng)?shù)據(jù)包收發(fā)流程。

由于CS8900A地址線SA0接STR710地址總線A11 (見圖3原理圖),因此訪問(wèn)CS8900A的端口地址必須左移11位。片外存儲(chǔ)器Bank1的地址范圍是0x62000000-0x62FFFFFF.即首地址為0x62000000。以太網(wǎng)端口地址相關(guān)程序可以定義為:

#define ETH_Port(n)(*(vu 16*)(0x62000000 I(n)《《11)) 初始化CS8900的軟件流程圖如圖4:

圖4軟件流程圖(software flow chart)

6.2 LwIP協(xié)議棧的實(shí)現(xiàn)

LwIP即Light Weight (輕型)IP協(xié)議,是瑞士計(jì)算機(jī)學(xué)院(SICS)的Adam Dunkels等開發(fā)的一套用于嵌入式系統(tǒng)的開放源碼的TCP/IP協(xié)議棧。它占用空間小。在保護(hù)協(xié)議主要功能的基礎(chǔ)上減少對(duì)RAM和ROM的占用。一般它只需要幾十K的RAM和40K左右的ROM就可以運(yùn)行。LwlP實(shí)現(xiàn)了較為完備的IP、CMP、UDP、TCP協(xié)議。具有超時(shí)時(shí)間估計(jì)、快速恢復(fù)和重發(fā)、窗口調(diào)整等功能。該協(xié)議棧提供了一組API函數(shù)供應(yīng)用程序調(diào)用,編程方便。由于采用靈活的數(shù)據(jù)包存儲(chǔ)機(jī)制。發(fā)送和接收的數(shù)據(jù)在各層協(xié)議之間不需要拷貝,內(nèi)存消耗小。

本文設(shè)計(jì)中UDP協(xié)議的實(shí)現(xiàn)包括以下內(nèi)容:(1)設(shè)置通信UDP IP地址及端口,設(shè)定發(fā)緩沖區(qū)類型(2)設(shè)定UDP功能函數(shù),分配一個(gè)新的UDP PCB,為緩沖區(qū)分配內(nèi)存(3)CS8900A復(fù)位 (4)初始化LwIP的內(nèi)部緩沖區(qū)、網(wǎng)絡(luò)界面,設(shè)置MAC地址(5)修改默認(rèn)網(wǎng)絡(luò)配置以適應(yīng)具體需要.配置網(wǎng)絡(luò)地址.網(wǎng)關(guān),子網(wǎng)掩碼(6)建立LwlP網(wǎng)絡(luò)界面,設(shè)為默認(rèn)網(wǎng)絡(luò)界面并啟動(dòng)網(wǎng)絡(luò)界面(7)初始化IP,TCP,HTTP模塊(8)UDP端口綁定,指定接收回調(diào)函數(shù),接收來(lái)自NIC的數(shù)據(jù)包,是否有數(shù)據(jù)包被接受?如果有.將數(shù)據(jù)包交給LwlP處理。

7 結(jié)束語(yǔ)

隨著經(jīng)濟(jì)和科技的快速發(fā)展,如電弧爐等眾多的家用電器的非線性負(fù)荷不斷增大,導(dǎo)致電力系統(tǒng)中的諧波水平隨之提高。因此,由諧波引起的系統(tǒng)諧振所產(chǎn)成的過(guò)電流、過(guò)電壓對(duì)電力系統(tǒng)的安全運(yùn)行帶來(lái)的危害不容忽視,而通過(guò)對(duì)基于ARM的電腿諧波智能監(jiān)測(cè)及消諧裝置的實(shí)例研究,對(duì)于電力系統(tǒng)的安全運(yùn)行意義重大。

本文作者創(chuàng)新點(diǎn):提出了在移植LwlP協(xié)議棧下基于ARM7嵌入式以太閱接口的實(shí)現(xiàn)方法.并在ARM7開發(fā)板上成功的用于實(shí)現(xiàn)。目前,ARM處理器由于它具有高性能、低成本、低功耗等特點(diǎn),已經(jīng)成為應(yīng)為最為廣泛的嵌入式處理器,以及CS8900A以太網(wǎng)控制器的性能優(yōu)良.功耗低,價(jià)格低廉等待點(diǎn)。在市場(chǎng)上10Mb/s嵌入式網(wǎng)絡(luò)應(yīng)用中占有很大的比例,因此基于ARM的電壓諧波智能監(jiān)測(cè)及消諧裝置的研究,特別是基于ARM7嵌入式以太網(wǎng)接口的實(shí)現(xiàn),對(duì)于開展預(yù)防和抑制諧波諧振放慢必將有著良好的應(yīng)用前景。

責(zé)任編輯:gt

-

處理器

+關(guān)注

關(guān)注

68文章

19159瀏覽量

229112 -

嵌入式

+關(guān)注

關(guān)注

5068文章

19014瀏覽量

303226 -

以太網(wǎng)

+關(guān)注

關(guān)注

40文章

5374瀏覽量

171093

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

嵌入式工業(yè)以太網(wǎng)控制器的設(shè)計(jì)和應(yīng)用

高性能嵌入式工業(yè)以太網(wǎng)監(jiān)控系統(tǒng)電路設(shè)計(jì)

32位嵌入式處理器與8位處理器應(yīng)用開發(fā)的區(qū)別

基于TCP IP協(xié)議棧的嵌入式以太網(wǎng)終端設(shè)計(jì)

基于Cortex-A8處理器的嵌入式wince工控機(jī)

基于嵌入式以太網(wǎng)控制的接口電路及軟硬件實(shí)現(xiàn)方法

基于DSP的嵌入式以太網(wǎng)接口電路設(shè)計(jì)

怎么實(shí)現(xiàn)基于S3C4480X的嵌入式以太網(wǎng)接口設(shè)計(jì)?

基于雙以太網(wǎng)處理器Jupiter實(shí)現(xiàn)嵌入式設(shè)備網(wǎng)絡(luò)的設(shè)計(jì)

基于ARM 嵌入式以太網(wǎng)接口設(shè)計(jì)與實(shí)現(xiàn)Design and

嵌入式以太網(wǎng)接口的研究與設(shè)計(jì)

基于ARM7的以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)

基于ARM7的以太網(wǎng)接口的設(shè)計(jì)與實(shí)現(xiàn)

基于OR1200微處理器的嵌入式以太網(wǎng)設(shè)計(jì)

RTL8019AS實(shí)現(xiàn)嵌入式以太網(wǎng)設(shè)計(jì).rar

基于STR710處理器實(shí)現(xiàn)嵌入式以太網(wǎng)接口的應(yīng)用方案

基于STR710處理器實(shí)現(xiàn)嵌入式以太網(wǎng)接口的應(yīng)用方案

評(píng)論