編 者 按

上世紀(jì)中葉,IEEE電子和電子工程師協(xié)會在上世紀(jì)中葉設(shè)立了一個(gè)叫ITRS的組織,該組織每年都會發(fā)布一份半導(dǎo)體領(lǐng)域中技術(shù)路線圖——ITRS(International Technology Roadmap for Semiconductors)路線圖。但在2017年,IEEE停止更新ITRS,并將其重新重命名為IRDS,他們認(rèn)為這樣可以更全面地反應(yīng)各種系統(tǒng)級新技術(shù)。

與此同時(shí),業(yè)界提出了More Moore、Moore than Moore和Beyond COMS三種方法,來持續(xù)提升芯片性能。在本文中,我們摘譯了IRDS最新版本的IRDS 2020,里面談及Moore Moore的一些路線預(yù)測,歡迎大家閱讀。

技術(shù)現(xiàn)狀

大部分的半導(dǎo)體器件都是數(shù)字邏輯,那就需要去支持兩種器件類型的技術(shù)平臺:1)高性能邏輯;2)低功耗/高密度邏輯。該技術(shù)平臺的關(guān)鍵考慮因素是速度、功耗、密度和成本。More Moore路線圖為MOSFET的持續(xù)擴(kuò)展提供了一個(gè)參考,以保持以更低的功耗和成本改進(jìn)設(shè)備性能的歷史趨勢。

所謂“More Moore”,這是一個(gè)延續(xù)CMOS的整體思路方法,具體而言就是在器件結(jié)構(gòu)、溝道材料、連接導(dǎo)線、高介質(zhì)金屬柵、架構(gòu)系統(tǒng)、制造工藝等等方面進(jìn)行創(chuàng)新研發(fā),沿著摩爾定律一路微縮。

以下應(yīng)用推動(dòng)了IRDS中More Moore技術(shù)的需求:

?高性能計(jì)算——在恒定功率密度(受熱約束)下的更高性能

?移動(dòng)計(jì)算——以恒定的功耗(受電池限制)和成本提供更多的性能和功能

?自主感知和計(jì)算(IoT)——以減少泄漏( leakage)和變異性(variability)為目標(biāo)

而技術(shù)驅(qū)動(dòng)因素包括以下重點(diǎn)項(xiàng)目:邏輯技術(shù)(Logic technologies)、基本規(guī)則縮放(Ground rule scaling)、性能助推器(Performance boosters)、性能-功率-尺寸(PPA)縮放(Performance-power-area (PPA) scaling)、3D集成(3D integration)、內(nèi)存技術(shù)(Memory technologies)、DRAM技術(shù)(DRAM technologies)、Flash技術(shù)(Flash technologies)、新興的非易失性內(nèi)存(NVM)技術(shù)(Emerging non-volatile-memory (NVM) technologies)

More Moore目標(biāo)是每2——3年為節(jié)點(diǎn)擴(kuò)展帶來PPAC價(jià)值:

?(P)性能:在標(biāo)度電源電壓下,工作頻率增加15%以上?(P)功率:在給定性能下,每次開關(guān)的能量損耗減少30%以上?(A)面積:減少30%的芯片面積;?(C)成本:晶圓成本增加《30% -縮放裸片成本減少15%。

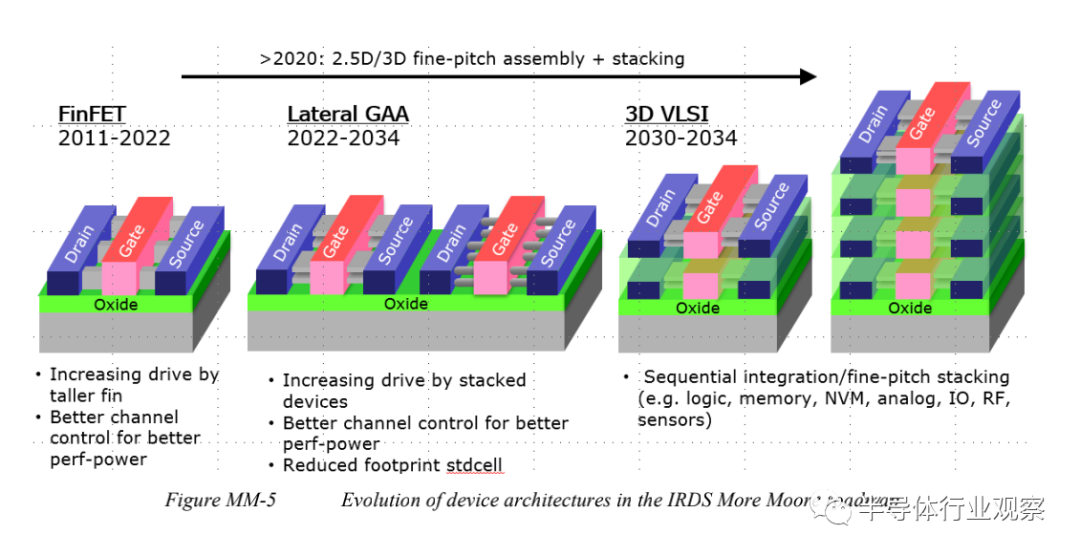

這些標(biāo)度目標(biāo)推動(dòng)了該行業(yè)的一些重大技術(shù)創(chuàng)新,包括材料和工藝的變化,如 high-κ柵極電介質(zhì)和應(yīng)變增強(qiáng)(strain enhancement),以及在不久的將來,新的架構(gòu),如柵極全方位(GAA);替代高遷移率溝道材料和新的3D集成方案,允許異構(gòu)疊加/集成。這些創(chuàng)新將以快速的速度引入,因此及時(shí)地理解、建模和實(shí)現(xiàn)到制造業(yè)中對行業(yè)來說是至關(guān)重要的。

需要注意的是,成本指標(biāo)(減少15%的裸片成本)和市場節(jié)奏(每年都需要推出新產(chǎn)品)在移動(dòng)產(chǎn)業(yè)中越來越重要。由于應(yīng)用嚴(yán)格要求所有figure-of-merits(FoM)同時(shí)滿足,有必要推進(jìn)一個(gè)有效的工藝技術(shù)清單,以維持某些設(shè)備架構(gòu)的極限,例如在未來五年推動(dòng)finFET架構(gòu)。

在從一個(gè)邏輯世代到另一個(gè)邏輯世代的過程中,這種方法還有助于以降低風(fēng)險(xiǎn)的方式維持成本。由于多圖形光刻步驟的增加,晶圓加工的成本越來越高,這就變得更加困難。我們還 需要在相同數(shù)量的晶體管上降低15%以上的成本,這只能通過在溝道材料、器件架構(gòu)、接觸工程(contact engineering)和器件隔離方面的新進(jìn)展實(shí)現(xiàn)pitch scaling。增加的工藝復(fù)雜性也必須考慮到整個(gè)裸片良率。為了補(bǔ)償復(fù)雜性的成本,需要加速設(shè)計(jì)效率,進(jìn)一步擴(kuò)大面積,以達(dá)到裸片成本的比例目標(biāo)。

在ITRS的系統(tǒng)驅(qū)動(dòng)技術(shù)工作組的早期工作中也觀察到了這些設(shè)計(jì)誘導(dǎo)的縮放因子,它們被用作校準(zhǔn)因子,以匹配行業(yè)的面積縮放趨勢。設(shè)計(jì)比例因子(design scaling factor)現(xiàn)在被認(rèn)為是More Moore技術(shù)路線圖的關(guān)鍵元素之一。

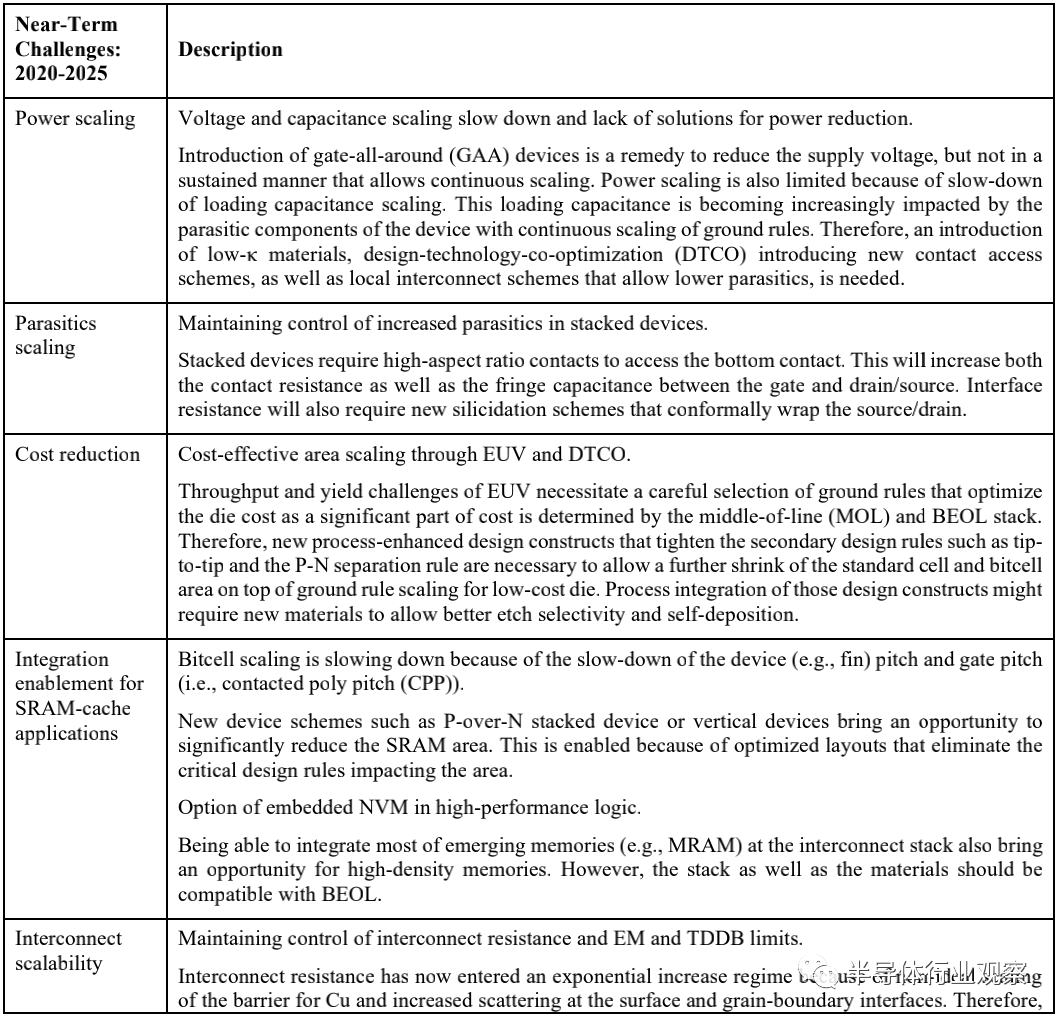

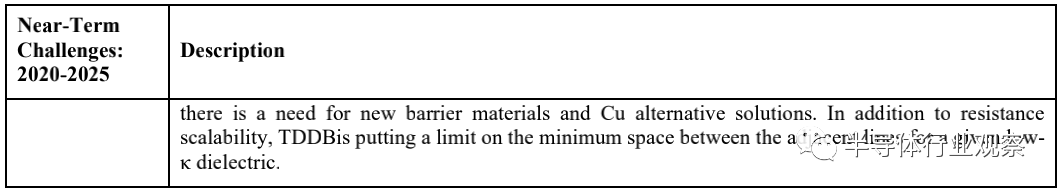

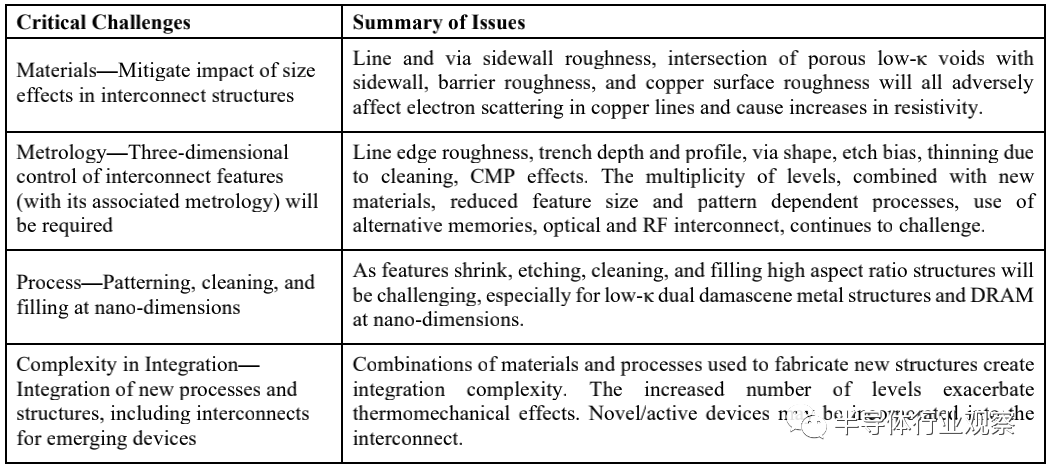

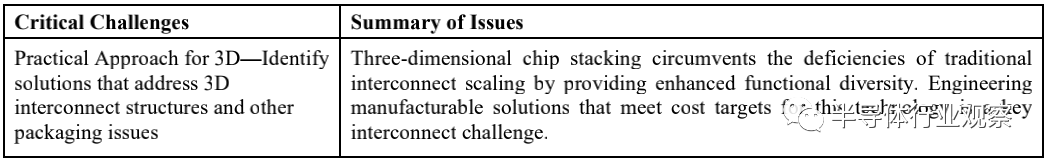

半導(dǎo)體行業(yè)的目標(biāo)是能夠在降低功耗和成本的情況下繼續(xù)擴(kuò)大技術(shù)的整體性能。器件和最終芯片的性能可以通過許多不同的方式來衡量:更高的速度、更高的密度、更低的功耗、更多的功能,等等。從本質(zhì)上講,dimensional scaling已經(jīng)足以帶來上述的性能優(yōu)點(diǎn),但現(xiàn)在已經(jīng)不是這樣了。制程、工具和材料性能等,對繼續(xù)擴(kuò)展提出了困難的挑戰(zhàn)。我們在表MM-5和表MM-6中總結(jié)了這些困難的挑戰(zhàn)。這些挑戰(zhàn)分為近期2020-2025年(表MM-5)和長期2026-2034年(表MM-6)。

如下圖所示表MM-5展示了近期的挑戰(zhàn)。

表MM-6則說明了長期的困難挑戰(zhàn)

晶體管的演進(jìn)

在More Moore路線圖中,我們將重點(diǎn)放在了有效的解決方案上,以在縮放的尺寸和縮放的供電電壓下維持性能和功率的縮放。基本規(guī)則縮放(Ground rule scaling )驅(qū)動(dòng)裸片成本降低。然而,這種縮放增加了寄生在總負(fù)載中的部分,并在性能和功率縮放中帶來的縮放收益遞減。因此,有必要關(guān)注技術(shù)擴(kuò)展的解決方案,同時(shí)擴(kuò)展設(shè)備和互連的寄生。

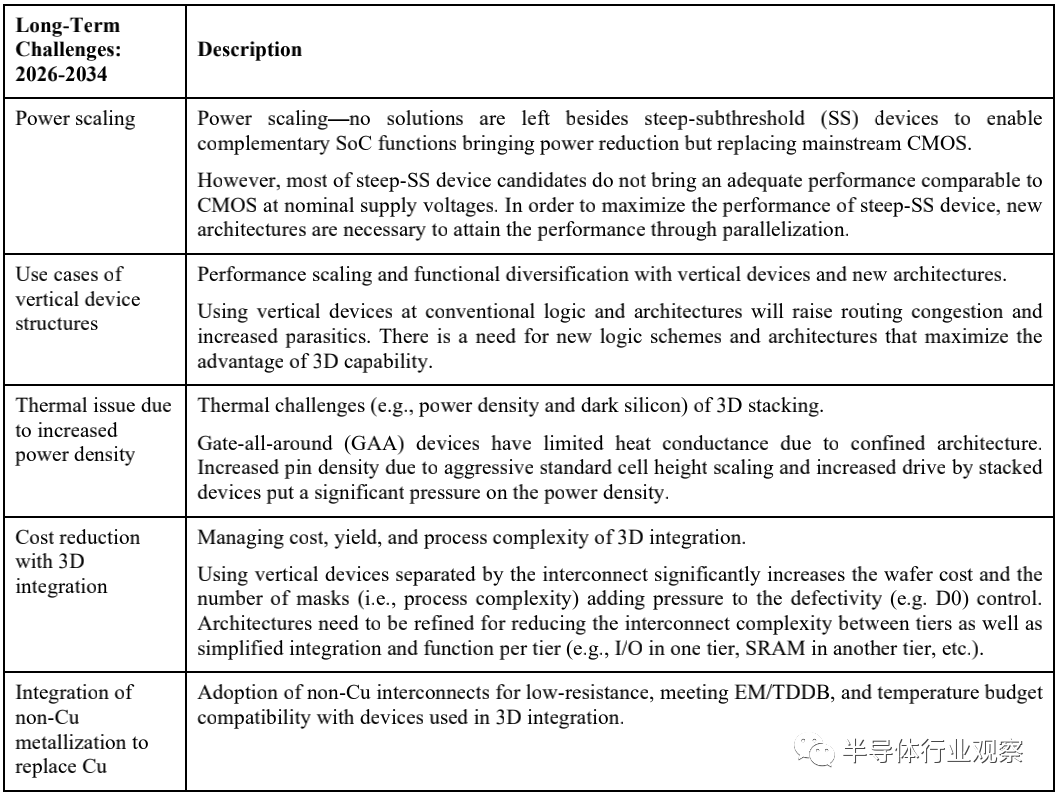

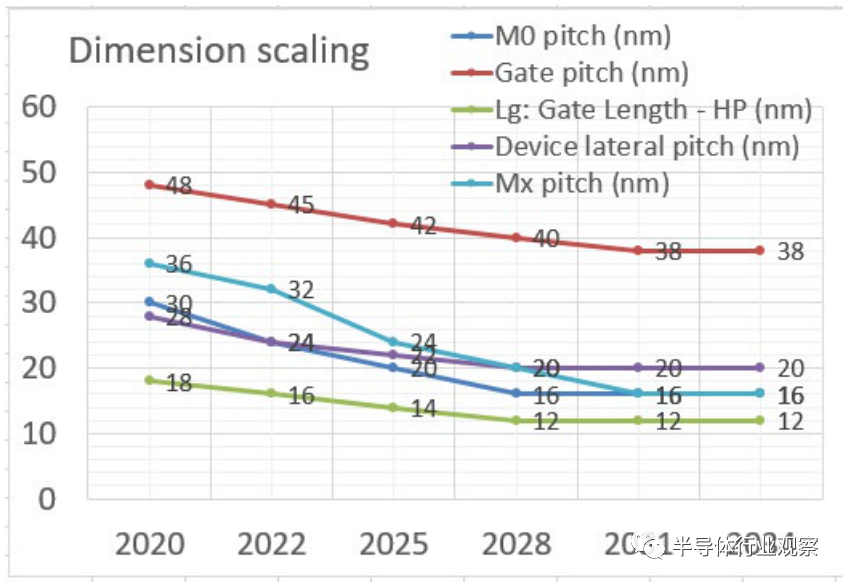

基礎(chǔ)規(guī)則縮放(Ground rule scaling )還需要使DTCO結(jié)構(gòu)能夠適應(yīng)面積縮小,并收緊限制面積縮放的關(guān)鍵設(shè)計(jì)規(guī)則。由于multiple patterning的成本和過程的復(fù)雜性,EUV被用于以較少的制程步驟來解決模式嚴(yán)密的基本規(guī)則。規(guī)劃的基本規(guī)則路線圖和設(shè)備架構(gòu)如表MM-7所示。基本規(guī)則的演化過程如圖MM-2所示。對于不同的代工廠和集成設(shè)備制造商(IDMs)的節(jié)點(diǎn)命名還沒有達(dá)成共識;

然而,計(jì)劃規(guī)則給出了技術(shù)能力符合PPAC要求的指示。基礎(chǔ)規(guī)則(ground rules)中的關(guān)鍵參數(shù)是柵極間距、金屬間距、fin間距和柵極長度,它們是核心邏輯區(qū)域縮放的重要因素。

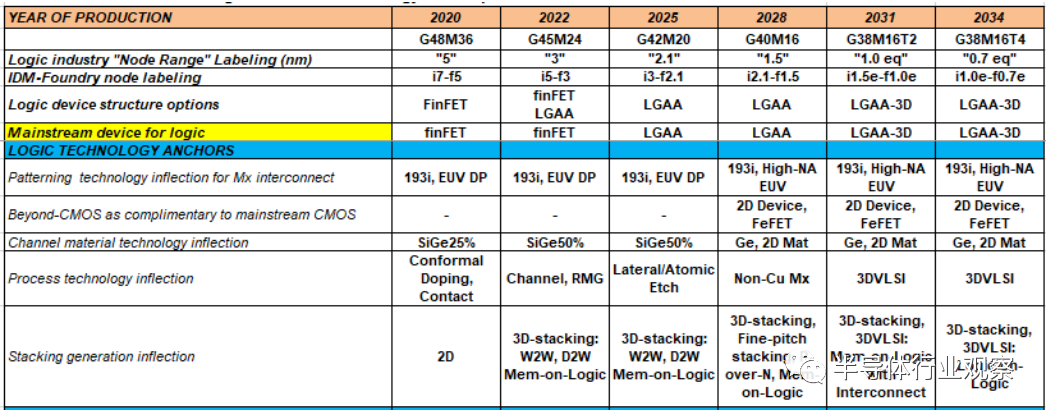

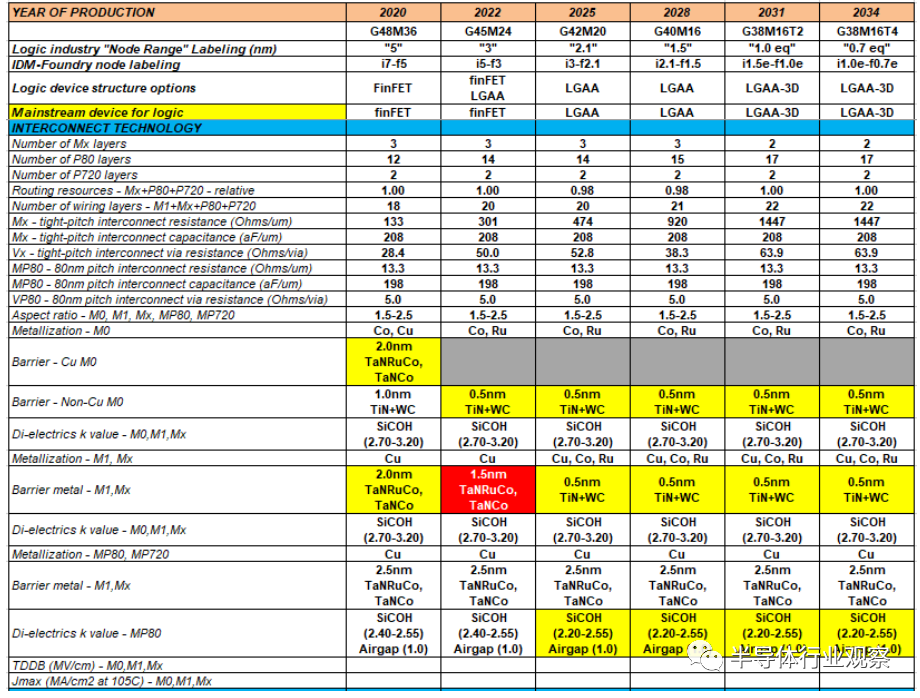

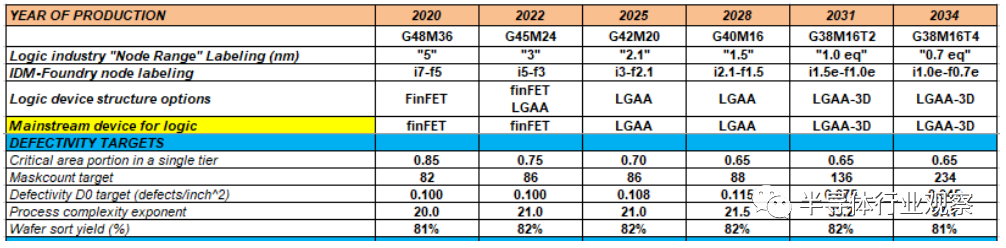

表MM-7邏輯器件的設(shè)備件、PPA和基本規(guī)則路線圖。

表中使用的首字母縮寫(按外觀順序):LGAA-lateral gate-all-around-device (GAA), 3DVLSI-fine-pitch 3D邏輯順序集成。

圖MM-2關(guān)鍵基本規(guī)則的投影比例

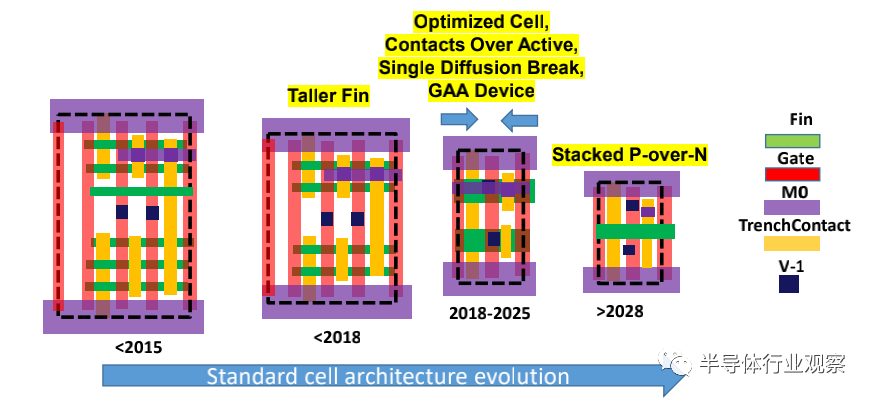

僅按基本規(guī)則縮放(Ground rule scaling )不足以縮放單元格高度。有必要將設(shè)計(jì)比例系數(shù)付諸實(shí)踐。例如,標(biāo)準(zhǔn)單元高度將通過縮放標(biāo)準(zhǔn)單元中有源器件的數(shù)量/寬度以及縮放次要規(guī)則(例如尖端到尖端(tip-to-tip)、延伸、P-N分離(P-N separation)和最小面積規(guī)則)來進(jìn)一步減小。

類似地,可以通過關(guān)注關(guān)鍵設(shè)計(jì)規(guī)則(如邊緣fin的fin端接等)和啟用結(jié)構(gòu)(如有源接觸)來減小標(biāo)準(zhǔn)單元寬度。此外,需要仔細(xì)選擇接觸結(jié)構(gòu),以降低連接處電流密度增加的風(fēng)險(xiǎn)。預(yù)計(jì)到2028年,P和N器件可以堆疊在一起,從而進(jìn)一步降低成本。標(biāo)準(zhǔn)單元縮放的趨勢如圖MM-3所示。

圖MM-3通過fin去填充和設(shè)備堆疊縮放標(biāo)準(zhǔn)單元高度和寬度

在我們看來,2031年以后,就沒有二維微縮的空間了,使用順序/堆疊集成方法的電路和系統(tǒng)的三維超大規(guī)模集成(VLSI)將是必要的。這是由于沒有接觸放置(contactplacement )的空間,以及由于gate pitch scaling和metal pitch scaling而導(dǎo)致性能惡化。

據(jù)預(yù)測,由于靜電效應(yīng)的惡化,物理溝道長度將在12nm左右飽和,而gate pitch將在38nm處飽和,以便為器件接觸預(yù)留足夠的寬度(~14nm),提供可接受的寄生。3D VLSI期望為目標(biāo)節(jié)點(diǎn)帶來PPAC增益,并為異構(gòu)和/或混合集成鋪平道路。

這種3D集成的挑戰(zhàn)是如何劃分系統(tǒng),以更好地利用設(shè)備、互連和子系統(tǒng)(如內(nèi)存、模擬和I/O)。這就是為什么在2031年后需要進(jìn)行functional scaling和/或重大架構(gòu)更改的原因。這可能是Beyond CMOS和專業(yè)技術(shù)設(shè)備/組件的時(shí)代,將系統(tǒng)微縮到單位功率密度和單位立方體積下的高系統(tǒng)性能。

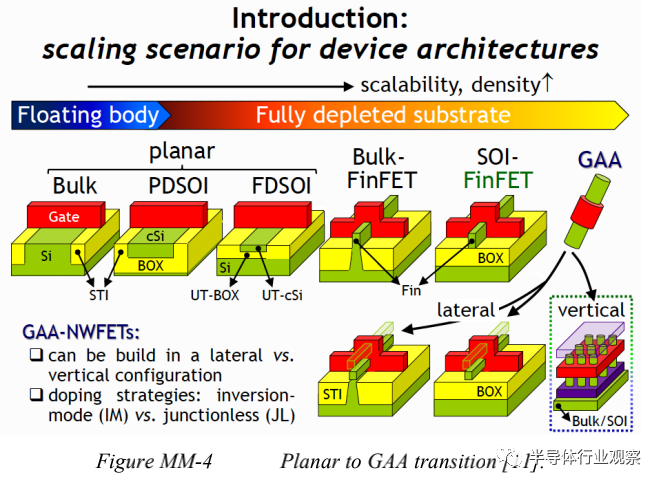

在130nm節(jié)點(diǎn)出現(xiàn)之前的最初幾年,晶體管遵循著Dennard scaling,其中等效氧化物厚度(EOT)、晶體管柵極長度(Lg)和晶體管寬度(W)均采用常數(shù)因子進(jìn)行微縮,以便在恒定功率密度下提供延遲改善。

目前,有許多輸入?yún)?shù)可以改變,而輸出參數(shù)是這些輸入?yún)?shù)的復(fù)雜函數(shù)。可發(fā)現(xiàn)其它組投射的參數(shù)值(即,不同的縮放場景)來實(shí)現(xiàn)相同的目標(biāo)。為了維持低電壓下的定標(biāo),近年來的定標(biāo)主要集中在提高性能的其他解決方案上,如在溝道中引入應(yīng)變、應(yīng)力助推器、high-κ金屬柵、降低接觸電阻和改善靜電。所有這些都是為了補(bǔ)償柵極驅(qū)動(dòng)損耗的同時(shí),還滿足高性能移動(dòng)應(yīng)用所需要的低電源電壓。

設(shè)備架構(gòu)、關(guān)鍵模塊和performance boosters的路線圖概述如表MM-8所示。

表MM-8More Moore微縮的設(shè)備路線圖和技術(shù)錨定。

FinFET仍然是關(guān)鍵的晶體管架構(gòu),目前看來他們還可以持續(xù)擴(kuò)展到2025年。ctrostatics和findepopulation仍然是改善性能的兩種有效解決方案。寄生改進(jìn)(Parasitics improvement)預(yù)計(jì)將繼續(xù)作為性能改進(jìn)的主要手段,作為收緊設(shè)計(jì)規(guī)則的結(jié)果。預(yù)計(jì)寄生( parasitics )將繼續(xù)作為關(guān)鍵路徑性能的主導(dǎo)項(xiàng)。

為了降低供電電壓,未來的晶體管必須過渡到如橫向 nanosheets這樣的GAA結(jié)構(gòu),以維持柵極驅(qū)動(dòng)改進(jìn)的靜電學(xué)。橫向GAA結(jié)構(gòu)最終將演變?yōu)榕c垂直GAA結(jié)構(gòu)的混合形式,以彌補(bǔ)由于在更緊密的pitches上增加寄生以及特殊SoC功能(如內(nèi)存選擇器)所造成的性能損失。

順序集成(Sequential integration)將允許采用單片3D (monolithic 3D)集成在彼此之上進(jìn)行堆疊。微縮的焦點(diǎn)則將從單線程性能提升轉(zhuǎn)移到功耗降低,然后發(fā)展到高度并行的3D架構(gòu),允許低Vdd操作和更多的功能嵌入到單位立方體體積中。

雖然設(shè)備架構(gòu)正在發(fā)生變化,但后續(xù)的模塊預(yù)計(jì)也將發(fā)展。這些可能包括:

1.起始襯底,如Si到絕緣體體上硅(SOI)和SRA(strain-relaxation-buffer);2.從Si到SiGe、Ge、IIIV的溝道材料演變;3.接觸模塊從硅化物演變?yōu)樘峁└?a target="_blank">肖特基阻隔高度(SBH)的新型材料,并采用包裹式接觸集成方案來增加接觸表面積。

正如前面提到的,finFET可能可能會維持到2025年。到2022年以后,橫向GAA晶體管的過渡預(yù)計(jì)將開始,并可能包括縱向GAA設(shè)備的混合形式與橫向GAA,潛在的3D混合memory-on-logic應(yīng)用。這種情況是由于fin寬度縮放和接觸寬度的限制。

Parasitic capacitance penalty, Weff(effective drive width )和RMG9(replacement metal gate )集成對GAA的應(yīng)用構(gòu)成了挑戰(zhàn)。一個(gè)折衷的解決方案可能是EGAA(electrically GAA)架構(gòu),它大大減少寄生電容,并增加有效寬度,以帶來更好的短溝道控制和更強(qiáng)的驅(qū)動(dòng)。晶體管架構(gòu)的演進(jìn)規(guī)劃如圖MM-5和圖MM-5所示。

體硅仍將是主流襯底,而絕緣體上硅(SOI)和SRB將分別用于支持更好的隔離(例如,射頻集成)和無缺陷集成的高遷移率溝道。

我們知道,像Ge和III-V族材料這樣的高遷移率材料在通過增加一個(gè)數(shù)量級的固有遷移率來增加驅(qū)動(dòng)電流方面帶來了希望。隨著柵極長度的縮放,由于速度飽和,遷移率對漏極電流的影響變得有限。

另一方面,當(dāng)柵極長度進(jìn)一步縮小時(shí),載流子傳輸變成了ballistic。這使得載流子的速度(也稱為“注入速度”)隨著移動(dòng)性的增加而導(dǎo)致漏極電流的增加。然而,對于高遷移率器件,低有效質(zhì)量(low effective mass)實(shí)際上會在較高的供電電壓下產(chǎn)生高的隧穿電流。這可能會降低III-V器件在短溝道工作函數(shù)調(diào)諧后的有效性能(例如,閾值電壓增加),以降低漏電流(Ioff),以補(bǔ)償隧穿電流。

高遷移率溝道需要考慮的另一個(gè)問題是較低的態(tài)密度( lower density of states)。電流與溝道中的漂移速度和載流子濃度的乘積成正比。這就需要正確選擇柵極長度(Lg)、電源電壓(Vdd)和器件結(jié)構(gòu),以最大化這一乘積,而這些參數(shù)的選擇將因所使用的溝道材料類型不同而不同。這一切都需要整體解決。

很可能,高移動(dòng)性溝道將用于連續(xù)集成,以協(xié)同集成高速IOs、RF(如5G及以上)和photonics協(xié)集成。

在過去十年中,應(yīng)變工程(Strain engineering)已被用作最有效的解決方案之一,如32nm節(jié)點(diǎn)和早期的所示。然而,這些壓力源的影響可能不能直觀地推進(jìn)到新的節(jié)點(diǎn)上。隨著柵極間距的縮小,源漏外延(S/D EPI)接觸和SRB上的SiGe仍然是高遷移率溝道材料的兩倍以上的遷移率的有效助推器。工程師們在使用SRB的7nm CMOS平臺上成功地演示了PMOS的SiGe溝道和NMOS的應(yīng)變Si溝道。

另一方面,SRB或S/D應(yīng)力源可能對垂直器件中的溝道應(yīng)力產(chǎn)生不起作用。其他應(yīng)變工程技術(shù)還包括gate stressor 和ground plane stressors。

互聯(lián)和3D異構(gòu)集成

對于芯片的未來,互聯(lián)也是一個(gè)重要方面,而互連最困難的挑戰(zhàn)是引入滿足導(dǎo)線導(dǎo)電性要求、降低介電常數(shù)和滿足可靠性要求的新材料。對于導(dǎo)電性,必須減小尺寸效應(yīng)對互連結(jié)構(gòu)的影響。尺寸控制是當(dāng)今和未來幾代互連技術(shù)面臨的一個(gè)關(guān)鍵挑戰(zhàn),由此產(chǎn)生的刻蝕難題是在 low-κ介電材料中形成精確的溝道和通孔結(jié)構(gòu),以減少阻容(RC)的變化。

為了獲得最大的性能,互連結(jié)構(gòu)不能容忍剖面的變化而不產(chǎn)生不希望的RC退化。這些尺寸控制要求對測量高深寬比結(jié)構(gòu)的高通量成像計(jì)量提出了新的要求。新的計(jì)量技術(shù)也需要在線監(jiān)測附著力和缺陷。更大的晶圓和限制測試晶圓的需要將推動(dòng)更多的現(xiàn)場過程控制技術(shù)的采用。表MM-12突出并區(qū)分了最主要的挑戰(zhàn),表MM-13顯示了互連擴(kuò)展路線圖。

表MM-12互連難題

表MM-13互連擴(kuò)展路線圖

至少到2025年,銅(Cu)預(yù)計(jì)仍將是互連金屬的首選解決方案,而非銅溶液(例如Co和Ru)預(yù)計(jì)將用于本地互連(M0)。另一方面,由于電遷移的限制,局部互連(middle-of-line:MOL))、M1和Mx水平將使用如鈷(Co)這樣的非銅方案,特別是對于通孔,因?yàn)樗懈玫募纱翱趤硖畛洫M窄的溝槽,同時(shí)它在縮放尺寸上有比銅更低的電阻。

銅布線、線阻擋材料必須防止銅擴(kuò)散到鄰近的介電介質(zhì)中,但也必須與銅形成合適的、高質(zhì)量的界面,以限制空位擴(kuò)散,并實(shí)現(xiàn)可接受的電遷移壽命。Ta(N)是一個(gè)知名的行業(yè)解決方案。Mn(N)在近年來也受到了人們的高度關(guān)注。對于新型材料,SAMs(self-assembled monolayers)則是候選材料之一。

同時(shí),3D異構(gòu)集成也成為大家關(guān)注的一個(gè)方向。

眾所周知,每一代的邏輯節(jié)點(diǎn)都需要為其添加新的函數(shù),以保持單價(jià)不變(以保持利潤率)。由于以下挑戰(zhàn),這變得更加困難:

?留在板上/系統(tǒng)上的協(xié)同集成功能更少?每個(gè)功能專用的異構(gòu)核心和每個(gè)專用核心所需的專用性能改進(jìn)需求?封裝外存儲器與邏輯協(xié)同集成成本高,技術(shù)與基線CMOS不兼容(可能需要晶圓/芯片級堆疊)

到目前為止,裸片成本的降低是通過柵極間距(gate pitch)、金屬間距(metal pitch)和單元高度(cell height)的同步縮放實(shí)現(xiàn)的。預(yù)計(jì)這種情況將持續(xù)到2028年。在單元和物理設(shè)計(jì)中,三維器件(如finFET和橫向GAA)和DTCO結(jié)構(gòu)可能會追求單元高度縮放。然而,這種微縮途徑預(yù)計(jì)將面臨更大的挑戰(zhàn),因?yàn)?a href="http://www.nxhydt.com/v/tag/2364/" target="_blank">電氣/系統(tǒng)效益的減少,以及SoC水平上面積減少的減少。

因此,有必要尋求3D集成的,例如器件對器件堆疊(device-over-device stacking)、精細(xì)間距層轉(zhuǎn)移(fine-pitch layer transfer)和/或monolithic 3D(或sequential integration)。這些追求將保持系統(tǒng)性能和功率增益,同時(shí)潛在地保持成本優(yōu)勢,例如在其他地方處理昂貴的非縮放組件,并使用最適合每層功能的技術(shù)。

3DVLSI可以在門級或晶體管級布線。3DVLSI提供了堆疊層的可能性,實(shí)現(xiàn)了層級別的高密度接觸(每平方毫米高達(dá)幾百萬個(gè)過孔)。柵極級的分區(qū)允許由于導(dǎo)線長度減少而獲得IC性能增益,同時(shí)通過將nFET堆疊在pFET上(或相反)在晶體管級別進(jìn)行分區(qū),實(shí)現(xiàn)兩種類型晶體管的獨(dú)立優(yōu)化(定制實(shí)現(xiàn)溝道材料/襯底定向/溝道和提高的源極/漏極應(yīng)變等),同時(shí)與平面共集成相比降低工藝復(fù)雜度,例如在SiGe pFET上方堆疊III-V nFET。

這些高遷移率晶體管非常適合3DVLSI,因?yàn)樗鼈兊墓に嚋囟群艿汀>哂懈呓佑|密度的3DVLSI還可以實(shí)現(xiàn)與高密度3D過孔進(jìn)行異質(zhì)共集成的應(yīng)用,例如用于氣體傳感的CMOS的NEMS或高度小型化的成像器。集成器件對器件堆疊(例如P器件對N器件)以解耦溝道工程(例如用于PMOS的Ge溝道)以獲得更好的性能是一個(gè)巨大的發(fā)展勢頭。

為了解決從2D到3DVLSI的過渡,路線圖中預(yù)測了以下幾代:

(1)Die-to-wafer和wafer-to-wafer 堆疊:

方法:細(xì)間距(Fine-pitch)介質(zhì)/混合鍵合和/或倒裝芯片組裝

機(jī)會:減少系統(tǒng)上的材料清單、異構(gòu)集成、邏輯上的高帶寬和低延遲內(nèi)存

挑戰(zhàn):設(shè)計(jì)/架構(gòu)劃分

(2)設(shè)備對設(shè)備(例如P-over-N堆疊)

方法:順序集成

機(jī)會:減少標(biāo)準(zhǔn)單元和/或位單元的2D占用空間

挑戰(zhàn):最小化互連開銷是N&P之間實(shí)現(xiàn)低成本的關(guān)鍵

(3)添加邏輯3D SRAM和/或MRAM堆棧(嵌入式/堆疊)

方法:順序集成和/或晶圓轉(zhuǎn)移

機(jī)會:2D區(qū)域增益,邏輯和內(nèi)存之間更好的連接,使系統(tǒng)延遲增益。

挑戰(zhàn):如果使用堆疊方法,則解決較低層互連的熱預(yù)算,重新審視緩存層次結(jié)構(gòu)和應(yīng)用程序需求、電源和時(shí)鐘分布

(4)添加模擬和I/O方法:順序集成和/或晶圓傳輸

機(jī)遇:給予設(shè)計(jì)者更多的自由,并允許集成高移動(dòng)性溝道,將非微縮組件推到另一層,IP復(fù)用,可擴(kuò)展性

挑戰(zhàn):熱預(yù)算、可靠性要求、電源和時(shí)鐘分配

(5)True-3D超大規(guī)模集成電路:集群功能堆棧

方法:順序集成和/或晶圓片轉(zhuǎn)移

機(jī)會:互補(bǔ)功能,而不是CMOS替代,如神經(jīng)形態(tài),高帶寬內(nèi)存或純邏輯應(yīng)用納入新的數(shù)據(jù)流方案有利于3D連接。應(yīng)用實(shí)例包括神經(jīng)形態(tài)結(jié)構(gòu)中的圖像識別,寬io傳感器接口(例如,DNA測序,分子分析),以及高度并行的內(nèi)存邏輯計(jì)算。

挑戰(zhàn):架構(gòu)應(yīng)用程序,在低能量、低頻率和高度并行接口可以利用,映射應(yīng)用到非馮·諾伊曼架構(gòu)。

More Moore縮放需要增加金屬化層的數(shù)量,因此,如果在patterning技術(shù)上沒有進(jìn)步,就需要增加mask。預(yù)計(jì)從193i光刻到EUV的過渡將可能拯救mask。然而,由于對金屬化和用于3D集成的FEOL)和MOL集成的重復(fù)掩模的需求增加,掩模數(shù)量預(yù)計(jì)將在2031年后上升。這反過來會增加過程的復(fù)雜性,從而增加缺陷(D0)需求。2034年所需的D0水平預(yù)計(jì)將減少2.2倍,以保持80mm2移動(dòng)裸片(表MM-15)的良率在控制之下。

表MM-15 80mm2裸片的缺陷率(D0)要求。

存儲技術(shù)也要齊頭并進(jìn)

CMOS邏輯和存儲器共同構(gòu)成了半導(dǎo)體器件生產(chǎn)的主要部分。在探討完邏輯器件之后,我們需要考慮存儲器。

正如大家所熟知,存儲器的類型有DRAM和非易失性存儲器(NVM)。我們重點(diǎn)放在商品化的、獨(dú)立的芯片上,因?yàn)檫@些芯片傾向于驅(qū)動(dòng)存儲器技術(shù)。然而,嵌入式存儲芯片預(yù)計(jì)將遵循與商品存儲芯片相同的趨勢,通常有一定的時(shí)滯。對于DRAM和NVM,都考慮了詳細(xì)的技術(shù)要求和潛在的解決方案。

對于DRAM,主要目標(biāo)是繼續(xù)微縮1T-1C單元的占用空間,達(dá)到4F2的實(shí)際限制。挑戰(zhàn)是垂直晶體管結(jié)構(gòu),high-κ電介質(zhì)提高電容密度,同時(shí)保持低泄漏。從當(dāng)前的技術(shù)看來,DRAM的技術(shù)要求隨著微縮而變得越來越困難。近年來,DRAM中引入了許多新技術(shù),如193 nm ArF浸沒式高鈉光刻技術(shù),包括Fin型晶體管在內(nèi)的改進(jìn)cell的FET技術(shù),buried word line和cell FET等技術(shù)。

由于DRAM存儲電容在物理尺寸上變得越來越小,EOT(equivalent oxide thickness)必須急劇下降,以保持足夠的存儲電容。為了測量EOT,需要具有較高的相對介電常數(shù)(κ)的介質(zhì)材料。因此,我們采用MIM(metal-insulator-metal )電容器,選用high-κ (ZrO2/Al2O/ZrO2)材料。這種材料的發(fā)展和改進(jìn)一直持續(xù)到20nm HP和超high-κ (perovskite κ 》 50 ~ 100)材料的釋放。此外,high-κ絕緣子的物理厚度應(yīng)按比例縮小,以適應(yīng)最小特征尺寸。因此,電容器的三維結(jié)構(gòu)將由圓柱形變?yōu)橹鶢睢?/p>

另一方面,隨著外圍CMOS器件的微縮,這些器件形成后的工藝步驟需要低溫工藝制程。這對于通常在CMOS器件形成之后構(gòu)造DRAM cell工藝是一個(gè)挑戰(zhàn),因此僅限于低溫處理。DRAM外圍設(shè)備的要求可以放寬Ioff,但需要更多的LSTP(Ion of low standby power )設(shè)備。但是,未來需要high-κ金屬柵來維持性能。

另一個(gè)重要的話題是從6F2遷移到4F2 cell。由于half-pitch縮放變得非常困難,這是不可能維持的成本趨勢。保持成本趨勢并通過生成增加總比特輸出的最有前途的方法是改變單元大小因子(cell size factor)a的縮放(a = [DRAM cell大小]/[DRAMhalf pitch]]2)。目前6F2 (a = 6)是最常見的。例如,垂直cell 晶體管是需要的,但仍然有一些挑戰(zhàn)。

總而言之,保持足夠的存儲電容和足夠的cell晶體管性能是需要在未來保持時(shí)間特性。為了繼續(xù)擴(kuò)大DRAM設(shè)備的規(guī)模,并獲得更大的產(chǎn)品容量,它們的困難指數(shù)也在不斷增加,。此外,如果成本縮放的效率與引入新技術(shù)相比變差,則停止DRAM縮放,采用3D cell堆疊結(jié)構(gòu),或采用新的DRAM概念。討論了3D cell堆疊和新的概念DRAM,但沒有明確的途徑進(jìn)一步擴(kuò)展2D DRAM。

在DRAM之外,還有幾種存儲技術(shù),他們都有一個(gè)共同的特征——非易變性。根據(jù)應(yīng)用的不同,要求和挑戰(zhàn)也不同,從只需要Kb存儲的RFID到芯片中數(shù)百Gb的高密度存儲。非易失性存儲器可分為兩大類——閃存(NAND閃存和NOR閃存)和非基于電荷存儲的存儲器。非易失性內(nèi)存基本上是普遍存在的,許多應(yīng)用使用的嵌入式內(nèi)存通常不需要前沿技術(shù)節(jié)點(diǎn)。More Moore 非易失性內(nèi)存表只跟蹤內(nèi)存挑戰(zhàn)和領(lǐng)先的獨(dú)立部件的潛在解決方案。

閃存是基于簡單的單晶體管(1T)單元,其中晶體管既是存取(或單元選擇)設(shè)備又是存儲節(jié)點(diǎn)。目前閃存服務(wù)于99%以上的應(yīng)用。

當(dāng)存儲的電子數(shù)量達(dá)到統(tǒng)計(jì)極限時(shí),即使可以進(jìn)一步縮放器件并實(shí)現(xiàn)更小的單元,存儲陣列中所有器件的閾值電壓分布也變得無法控制,邏輯狀態(tài)也無法預(yù)測。因此,不能通過持續(xù)擴(kuò)展基于電荷的設(shè)備來無限期地增加存儲密度。但是,有效的密度增加可以通過垂直堆疊存儲層來繼續(xù)。

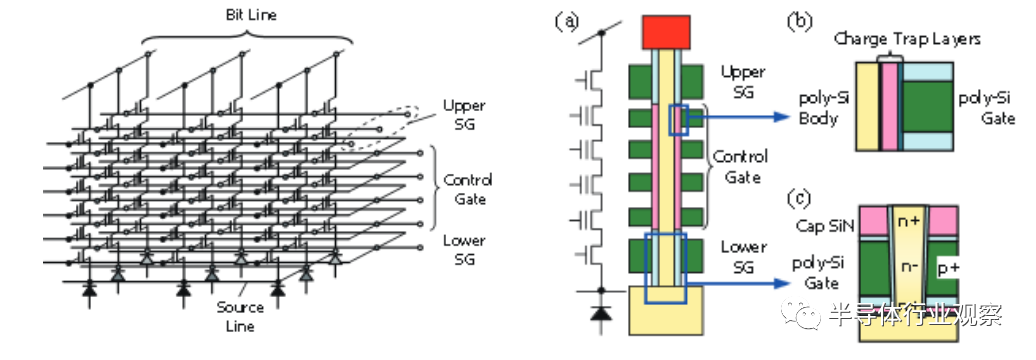

通過完成一個(gè)設(shè)備層然后再完成另一個(gè)設(shè)備層的堆疊經(jīng)濟(jì)是值得懷疑的。如圖MM-12所示,堆疊多層設(shè)備后,bit成本開始上升。此外,由于互連增加和復(fù)雜處理造成的產(chǎn)量損失,陣列效率的降低可能進(jìn)一步降低這種3D疊加的bit成本效益。

2007年,業(yè)內(nèi)提出了一種新的制造方法,大大簡化了制程步驟。這種方法無需重復(fù)處理,只需幾步就可以制作出3D堆疊設(shè)備,從而為NAND flash提供了一種新的低成本縮放路徑。圖MM-12說明了一種方法。這種架構(gòu)最初被稱為bitcost -scalable(簡稱BiCS),它將NAND string 從水平位置轉(zhuǎn)向垂直位置90度。word line(WL)保持在水平面上。如圖MM-12所示,這種類型的3D方法比堆疊完整的設(shè)備要經(jīng)濟(jì)得多,而且成本效益在相當(dāng)高的層數(shù)時(shí)不會飽和。

自2007年以來,人們提出了許多基于BiCS概念的架構(gòu),其中一些架構(gòu),包括一些使用floating gate 代替charge trapping 的存儲架構(gòu),這些技術(shù)在過去的2 - 3年已經(jīng)進(jìn)入量產(chǎn)。總的來說,所有3D NAND方法都采用了比傳統(tǒng)2D NAND更大的面積占用策略。與最小的2D NAND的~15nm相比,3D NAND的x-和y-尺寸(相當(dāng)于2D細(xì)胞尺寸)在100nm和更高的范圍內(nèi)。更大的“單元尺寸”是通過堆疊大量的存儲層來實(shí)現(xiàn)具有競爭力的封裝密度。

3D NAND的經(jīng)濟(jì)效益進(jìn)一步被其復(fù)雜和獨(dú)特的制造需求所困擾。雖然較大的cell尺寸似乎放寬了細(xì)線光刻的要求,但為了實(shí)現(xiàn)高數(shù)據(jù)速率,需要使用較大的page size,而這反過來又轉(zhuǎn)化為細(xì)線間距的位線和金屬線。因此,即使單元尺寸很大,金屬線仍然需要約20nm的半間距,這只能通過193i光刻和雙圖案實(shí)現(xiàn)。深孔的刻蝕困難且緩慢,并且刻蝕吞吐量通常很低。沉積多層電介質(zhì)和/或多晶硅,以及多層膜和深孔的計(jì)量都是一個(gè)挑戰(zhàn)。這些都轉(zhuǎn)化為對新設(shè)備和占地面積的巨大投資,以及對晶圓flow和良率的新挑戰(zhàn)。

閃存最終可以堆疊多少層?這似乎是一個(gè)未知之?dāng)?shù)。因?yàn)樵趯拥亩询B上似乎沒有嚴(yán)格的物理限制。但我們清楚認(rèn)識到,超過一定的縱橫比(也許是100:1?)后,蝕刻停止現(xiàn)象會發(fā)生,當(dāng)反應(yīng)離子蝕刻過程中的離子由于側(cè)壁上的靜電荷彎曲而無法向下傳播時(shí),可能會限制一次操作可以蝕刻多少層。

但是,可以通過堆疊更少的層,蝕刻和堆疊更多的層(以更高的成本)來繞過此問題。堆疊許多層可能會產(chǎn)生高應(yīng)力,從而使晶圓彎曲,盡管需要仔細(xì)設(shè)計(jì),但這似乎并不是一個(gè)無法解決的物理極限。即使在200層(每層約50nm)處,總堆疊高度約為10μm,仍與邏輯IC的10-15個(gè)金屬層處于相同范圍內(nèi)。這種層的厚度不會顯著影響裸片的厚度(到目前為止,最薄的厚度約為40μm)。

然而,在1000層時(shí),總的層厚度可能導(dǎo)致不符合用于在薄封裝中堆疊多個(gè)裸片(例如16或32)的形狀因數(shù)的厚裸片。現(xiàn)在閃存已經(jīng)到了170多層,我們認(rèn)為未來的256層也有可能。

當(dāng)堆積更多的層被證明太難時(shí),面積x-y可能最終開始縮小。然而,這種趨勢并不能保證。如果孔寬高比是限制,收縮 footprint不會降低比率,因此也不會有幫助。此外,與緊湊的2D NAND相比,更大的單元尺寸似乎至少部分地有助于3D NAND的性能(速度和循環(huán)可靠性)更好。x-y縮放是否還能提供這樣的性能還不清楚。可能需要新的創(chuàng)新或更強(qiáng)大的新興存儲器來進(jìn)一步降低 bit成本。

由于2D NAND Flash縮放受存儲電荷太少所致的統(tǒng)計(jì)波動(dòng)的限制,因此,一些不基于電荷存儲的非常規(guī)非易失性存儲器(鐵電或FeRAM,磁性或MRAM,相變或PCRAM,電阻性或ReRAM)正在被開發(fā)并形成通常被稱為“新興”存儲器的類別。

即使2D NAND被3D NAND取代(不再受電子數(shù)量不足的困擾),基于非電荷的新興存儲器的某些特性(如低壓操作或隨機(jī)存取)對于各種應(yīng)用也很有吸引力。因此繼續(xù)發(fā)展這些新興的存儲器通常具有兩端結(jié)構(gòu)(例如,電阻器或電容器),因此難以兼用作單元選擇裝置。存儲器單元通常以1T-1C,1T-1R或1D-1R的形式組合單獨(dú)的訪問設(shè)備。

(1)FeRAM

FeRAM器件通過切換和檢測鐵電電容器的極化狀態(tài)來實(shí)現(xiàn)非易失性。要讀取存儲狀態(tài),必須跟蹤鐵電電容器的hysteresis loop,并銷毀存儲的數(shù)據(jù),并且必須在讀取后將其寫回(破壞性讀取,如DRAM)。由于這種“破壞性讀取”,尋找鐵電和電極材料在延長的工作周期內(nèi)既能提供足夠的極化變化又能提供必要的穩(wěn)定性是一個(gè)挑戰(zhàn)。許多鐵電材料是CMOS制造材料的常規(guī)補(bǔ)充材料所不具備的,并且可以通過常規(guī)CMOS工藝條件進(jìn)行降解。

FeRAM快速,低功耗和低電壓,因此適用于RFID,智能卡,ID卡和其他嵌入式應(yīng)用。但加工難度限制了其廣泛采用。最近有人提出了基于HfO2的鐵電FET,其鐵電作用于改變FET的Vt,從而形成類似閃存的1T電池。如果發(fā)展成熟,這種新的記憶可能會成為一種低功耗、非常快的類似閃存的記憶。

(2) MRAM

MRAM(Magnetic RAM)設(shè)備采用磁性隧道結(jié)(MTJ)作為存儲元件。MTJ電池由兩種鐵磁材料組成,兩種鐵磁材料之間有一層薄絕緣層,充當(dāng)隧道屏障。當(dāng)一層magnetic moment與另一層magnetic moment對齊(或與另一層magnetic moment方向相反)時(shí),電流通過MTJ的有效電阻就會改變。可以通過讀取隧穿電流的大小來指示存儲的是1還是0。

場開關(guān)MRAM可能是最接近理想的“通用存儲器”,因?yàn)樗欠且资院涂焖俚模⑶铱梢詿o限循環(huán)。因此,它可以作為NVM以及SRAM和DRAM使用。然而,在集成電路中產(chǎn)生磁場既困難又低效。但現(xiàn)場切換MTJ MRAM已經(jīng)成功制成產(chǎn)品。然而,開關(guān)所需的磁場隨著存儲元件的擴(kuò)展而增加,而電遷移限制了可用來產(chǎn)生更高H場的電流密度。

因此,預(yù)計(jì)場開關(guān)MTJ MRAM不太可能擴(kuò)展到超過65nm節(jié)點(diǎn)以下。最近的STT有可能找到新的機(jī)會。

隨著NAND閃存技術(shù)的快速發(fā)展,以及3D NAND技術(shù)的引入有望繼續(xù)實(shí)現(xiàn)等量擴(kuò)展,STT-MRAM取代NAND的希望似乎遙不可及。然而,它類似sram的性能和比傳統(tǒng)6T-SRAM小得多的內(nèi)存占用已經(jīng)引起了人們對sram應(yīng)用的極大興趣,尤其是在不需要高循環(huán)耐力的移動(dòng)設(shè)備上,比如在計(jì)算方面。因此,STT-MRAM現(xiàn)在主要被認(rèn)為不是一個(gè)獨(dú)立的內(nèi)存,而是一個(gè)嵌入式內(nèi)存,并且不在獨(dú)立的NVM表中進(jìn)行跟蹤。

STT-MRAM不僅是嵌入式SRAM的替代方案,也是嵌入式Flash (NOR)的替代方案。這對于物聯(lián)網(wǎng)應(yīng)用來說可能特別有趣,因?yàn)榈凸氖亲钪匾摹A硪环矫妫瑢τ谄渌褂酶邇?nèi)存密度的嵌入式系統(tǒng)應(yīng)用來說,NOR Flash預(yù)計(jì)將繼續(xù)占據(jù)主導(dǎo)地位,因?yàn)樗匀痪哂懈蟮某杀拘б妗4送猓W存也建立了能夠忍受PCB板焊接過程(~ 250°C)不失其加載代碼,許多新興的記憶尚未能夠證明可行。

此外還有PCRAM、 Crosspoint存儲器和ReRAM值得關(guān)注,但限于篇幅,我們不一一介紹。

責(zé)任編輯:lq

-

晶圓

+關(guān)注

關(guān)注

52文章

4851瀏覽量

127816 -

邏輯器件

+關(guān)注

關(guān)注

0文章

88瀏覽量

20091 -

電流密度

+關(guān)注

關(guān)注

0文章

22瀏覽量

7948

原文標(biāo)題:More Moore最新路線圖淺讀

文章出處:【微信號:半導(dǎo)體科技評論,微信公眾號:半導(dǎo)體科技評論】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

一些常見的動(dòng)態(tài)電路

分享一些常見的電路

LED驅(qū)動(dòng)器應(yīng)用的一些指南和技巧

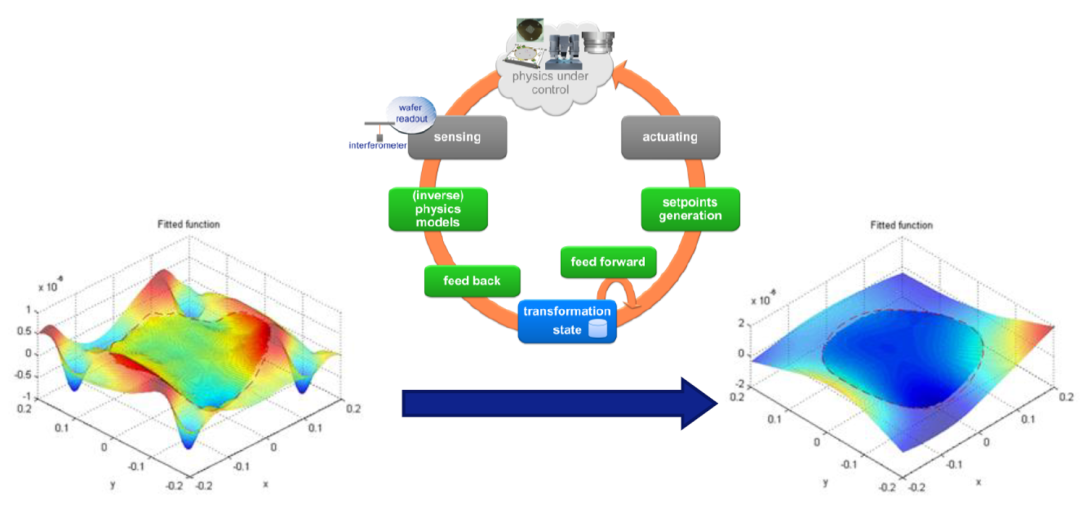

將基于模型設(shè)計(jì)應(yīng)用于半導(dǎo)體制造設(shè)備的研發(fā)

“自我實(shí)現(xiàn)的預(yù)言”摩爾定律,如何繼續(xù)引領(lǐng)創(chuàng)新

咨詢一些關(guān)于LED燈具的問題

英偉達(dá)遭潑冷水,大摩預(yù)測本季營收或低于預(yù)期

細(xì)談SolidWorks教育版的一些基礎(chǔ)知識

找一些有關(guān)通信電路的資料?

簡單了解幾種先進(jìn)封裝技術(shù)

英偉達(dá)RTX 50系列顯卡將采用PCIe Gen 6 16-Pin供電技術(shù)

免費(fèi)學(xué)習(xí)鴻蒙(HarmonyOS)開發(fā),一些地址分享

對于大模型RAG技術(shù)的一些思考

Moore Moore的一些路線預(yù)測

Moore Moore的一些路線預(yù)測

評論