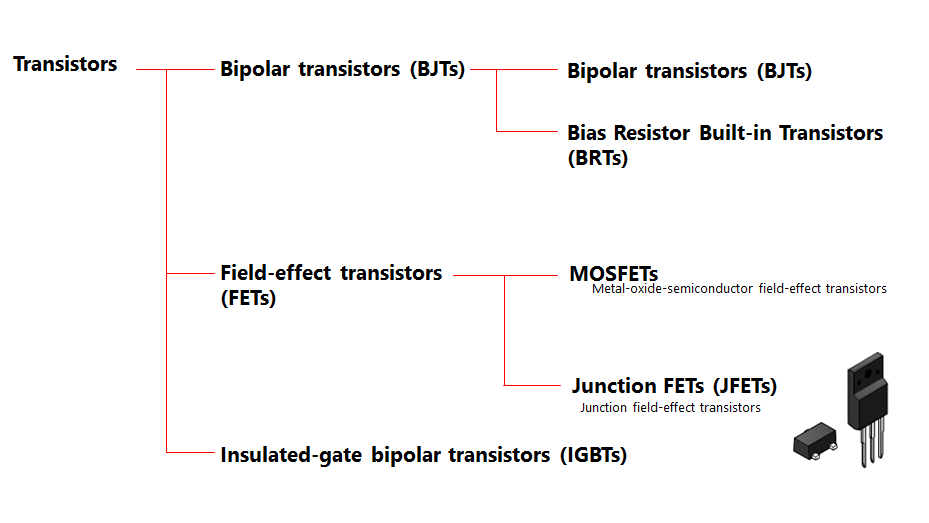

1958年,德州儀器(TI)使用兩個晶體管制造了第一臺集成電路觸發器。今天的芯片包含超過百億個晶體管。曾經可以支持整個公司會計系統的內存現在變成了一個人們隨身攜帶的智能手機。這種增長規模是由于晶體管的規模不斷擴大以及硅制造工藝的其他改進所致。在這個發展過程中,除了工藝繼續演進以外,晶體管也做了幾次變遷。在即將進入全新一代的晶體管以前,我們來回顧一下前幾代晶體管的發展。

歷史

真空管的發明推動了電子工業的發展。這些裝置將控制真空中的電子流動。但是,在第二次世界大戰之后,據觀察,由于大量的分立組件,這些設備的復雜性和功耗正在顯著增加。結果,設備的性能將持續下降。一個例子是一架波音B-29,它在戰爭中將由300-1000個真空管組成。每增加一個組件都會降低其可靠性并增加故障排除時間。

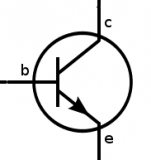

1947年這取得了重大突破,貝爾實驗室的John Baden,William Shockley和Watter Brattain推出了第一個功能點接觸鍺晶體管。1950年,肖克利開發了第一個雙極結型晶體管(BJT)。與真空管相比,晶體管更可靠,功率效率更高,尺寸更小。晶體管是一個三端設備,可以看作是一個電控開關。其中一個終端用作控制端子。理想情況下,如果將電流施加到控制端子,則該設備將充當兩個端子之間的閉合開關,否則將充當斷開開關。1958年,德州儀器(TI)的Jack Kilby建立了第一個集成電路,該集成電路由連接在一塊硅上的兩個雙極晶體管組成,從而開啟了“硅時代”。早期的IC使用雙極結型晶體管。BJT的缺點之一是由于更多的靜態功耗而產生的問題。這意味著即使電路不切換也要消耗功率。這限制了可以集成到單個硅芯片中的晶體管的最大數量。

1963年,Fairchild的Frank Wanlass和CTSah推出了第一款邏輯門,其中在互補對稱電路配置中使用了n溝道和p溝道晶體管。這就是今天所謂的CMOS。靜態功耗幾乎為零。

早期的IC使用NMOS技術,因為與CMOS技術相比,NMOS工藝相當簡單,價格便宜并且可以將更多設備封裝到一個芯片中。英特爾于1971年發布了第一個微處理器。

由于NMOS晶體管的靜態功耗要比CMOS高,因此IC的功耗在1980年代成為一個嚴重的問題,因為成千上萬個晶體管被集成到一個芯片中。由于具有低功耗,可靠的性能和高速等特性,CMOS技術將在幾乎所有數字應用中采用并取代NMOS和雙極性技術。

在接下來的幾年里,CMOS的縮放和加工技術的改進推動電路速度的不斷提高,以及芯片封裝密度和微電子產品的性能成本比的進一步提高。

在這里,我們討論了Bulk-Si CMOS技術,縮放的必要性和重要性,它們的各種影響以及相關的解決方案。我們還解決了晶體管材料和先進技術節點中使用的任何新材料的物理縮放限制。如今,由于在32nm技術節點下遇到的種種局限性,行業轉向SOI和FinFET,取代平面晶體管。

MOSFET器件概述

在這里,我們首先討論與CMOS核心單元(即MOSFET或簡稱MOS)有關的基本結構,操作和重要術語。第一個成功的MOS晶體管將金屬用作柵極材料,將SiO2(氧化物)用作絕緣體,將半導體用作襯底。因此,該器件被稱為MOS晶體管。場效應晶體管(FET)是,柵極通過晶體管導通和截止,電場穿過柵極氧化物。

A. MOS的結構:

根據導電溝道的類型,兩種MOS結構是顯而易見的:n溝道和p溝道MOS。在這里,我們將僅概述NMOS晶體管,因為兩個晶體管本質上是互補的。

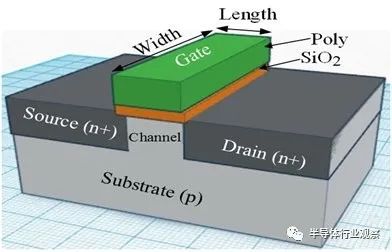

MOS晶體管是具有端子漏極,源極,柵極和主體(基板)的4端子設備。圖1顯示了NMOS的3維結構。NMOS晶體管形成在p型硅基板(也稱為主體)上。在器件的頂部中央部分,形成了一個低電阻率的電極,該電極通過絕緣體與主體隔開。通常,具有n型或p型重摻雜的多晶硅被用作柵極材料。在此,二氧化硅(SiO 2或簡單地為氧化物)用作絕緣體。通過將施主雜質注入襯底的兩側,形成源極和漏極。在圖1中,這些區域用n +表示,表示給體雜質的重摻雜。這種重摻雜導致這些區域的電阻率低。

如果兩個n +區域偏置在不同的電勢,則處于較低電勢的n +區域將充當源極,而另一個將充當漏極。因此,漏極和源極端子可以根據施加到它們的電勢互換。源極和漏極之間的區域稱為具有寬度W和長度L的溝道,在決定MOS晶體管的特性方面起著重要作用。

圖1. NMOS晶體管的結構

B.為什么用多晶硅作為柵極材料?

在半導體工業的早期,金屬鋁通常用作MOS的首選柵極材料。但是后來,多晶硅被優選作為柵極材料。向多晶硅過渡的兩個主要原因如下文所述。

早期的MOS制造工藝始于源區和漏區的定義和摻雜。然后,使用限定了柵極氧化物區域的柵極掩模,該柵極氧化物區域隨后將形成鋁金屬柵極。

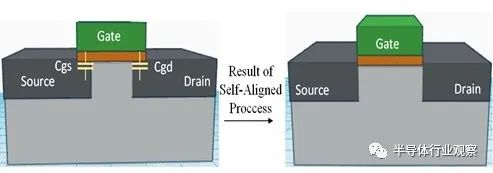

這種制造工藝的主要缺點之一是,如果柵極掩模未對準,則會產生寄生重疊輸入電容Cgd和Cgs,如圖2(a)所示。電容Cgd更有害,因為它是反饋電容。由于米勒電容,晶體管的開關速度會降低。

柵極掩模未對準的一種解決方案是所謂的“自對準柵極工藝”。該過程從創建柵極區域開始,然后使用離子注入創建漏極和源極區域。柵極下方的薄柵極氧化物用作摻雜工藝的掩模,可防止在柵極區域(溝道)下方進一步摻雜。因此,此過程使柵極相對于源極和漏極自對準。結果,源極和漏極不在柵極下方延伸。從而降低Cgd和Cgs,如圖2(b)所示。

圖2.(a)Cgd – Cgs寄生電容,(b)由于自對準過程而降低的Cgd和Cgs

漏極和源極的摻雜過程需要非常高的溫度退火方法(》 8000 * C)。如果將鋁用作柵極材料,它將在如此高的溫度下熔化。這是因為Al的熔點約為660攝氏度。但是,如果將多晶硅用作柵極材料,它將不會熔化。因此,利用多晶硅柵極可以進行自對準工藝。而對于Al-gate,則不可能,這會導致高Cgd和Cgs。未摻雜的多晶硅具有非常高的電阻率,約為108 ohm / Cm。因此,以降低電阻的方式摻雜多晶硅。

選擇多晶硅的另一個原因是MOS晶體管的閾值電壓與柵極和溝道之間的功函數差相關。早先,當工作電壓在3-5伏范圍內時,使用金屬門。但是,隨著晶體管的縮小,這確保了器件的工作電壓也降低了。在這種條件下,具有如此高的閾值電壓的晶體管將無法工作。與多晶硅相比,使用金屬作為柵極材料會導致較高的閾值電壓,因為多晶硅的成分與體硅溝道的成分相同或相似。另外,由于多晶硅是半導體,因此可以通過調節摻雜水平來調節其功函數。

C. MOS的工作原理:

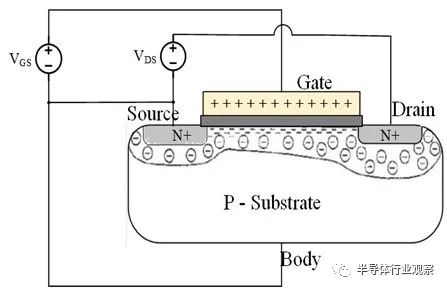

對于MOS晶體管,柵極電壓確定在漏極和源極之間是否會發生電流流動。讓我們進一步看。當足夠正的Vgs電壓施加到NMOS的柵極時,正電荷將置于柵極上方,如圖3所示。這些正電荷將排斥p型襯底的少數載流子,即來自襯底的空穴,留下產生耗盡區的負電荷受體離子。如果我們進一步提高Vgs,則在某些電勢水平下,它甚至會使表面吸引電子。因此,大量電子被吸引到表面。這種情況稱為反轉,因為p型體的表面通常具有大量的空穴,但是較新的表面具有大量的電子。

漏極至本體和源極至本體保持反向偏置。在圖3中,源到體保持零偏置。由于漏極至本體的電勢比源極至本體的電勢更正,因此漏極至本體的反向偏置更大,導致漏極區下方的耗盡層比源極側更深。

當施加跨漏極至源極的正電勢時,電子從源極流經導電溝道,并由漏極排出。因此,正電流Id從漏極流至源極。

圖3.反相區域中的NMOS晶體管

晶體管縮放的驅動力

電池供電的便攜式設備的需求隨著蜂窩電話,筆記本電腦等大量應用的增加而日益增加。此類應用的“基本要求”是面積較小,功耗較低且開發成本較低。對于這種便攜式設備,功率消耗很重要,因為電池提供的功率相當有限。不幸的是,不能期望電池技術每五年將電池存儲容量提高30%以上。這不足以處理便攜式設備所需的不斷增加的功率。

1965年,戈登·摩爾(Gordon E. Moore)預測集成電路中的晶體管數量每兩年將翻一番。通過使晶體管更小,可以在硅晶片上制造更多的電路,因此電路變得更便宜。由于電流從漏極流到源極所需的時間更少,因此溝道長度的減小可加快開關操作的速度。換句話說,較小的晶體管導致較小的電容。這導致晶體管延遲的減小。由于動態功率與電容成正比,因此功耗也降低了。晶體管尺寸的這種減小稱為縮放。每次縮放晶體管時,我們都會說一個新技術節點被引入。例如,10nm、7nm和5nm等。隨著每一代新技術的發展,這種擴展都會提高成本、性能和功耗。

對于長溝道設備,沿著溝道四個側面的“邊緣效應”確實可以忽略不計。對于長溝道設備,電場線到處都垂直于溝道表面。這些電場由柵極電壓和背柵極電壓控制。但是,對于短溝道器件,漏極和源極結構更靠近溝道,特別是當溝道中的縱向電場進入圖像時。縱向電場由漏極-源極電壓控制。縱向電場平行于電流流動方向。如果溝道長度不大于源極和漏極耗盡寬度之和,則該器件稱為短溝道器件。

在本節中,我們將討論由于二維電勢分布和短溝道中的高電場而產生的各種不良影響。

A.載流子速度飽和度和遷移率下降:

對于較低的電場值,溝道中的電子漂移速度與電場成比例。這些漂移速度傾向于在高電場下飽和。這稱為速度飽和。對于短溝道設備,縱向電場通常也會增加。在如此高的電場下,會發生速度飽和,這會影響MOSFET的IV特性。已經觀察到,對于相同的柵極電壓,MOSFET的飽和模式是在較小的漏極-源極電壓值和飽和電流降低下實現的。

由于較高的垂直電場,溝道的載流子從氧化物界面飛散。這導致載流子遷移率的下降和漏極電流的減小。

B、漏極引起的載流子降低:

另一個短溝道效應稱為DIBL,它是指在較高的漏極電壓下閾值電壓的降低。如果柵極電壓不足以使表面反轉(即,柵極電壓《閾值電壓),則溝道中的載流子將面對勢壘,該勢壘會阻止流動。通過增加柵極電勢,我們消除了這種勢壘。但是,對于短溝道設備,這種勢壘由Vgs和Vds共同控制。如果該漏極電壓增加,則漏極主體的耗盡區尺寸增大并且在柵極下方延伸。因此,即使在低于Vt的Vgs處,溝道中的勢壘也會減小,從而導致載流子(電子)在源極和漏極之間流動。漏極降低溝道勢壘并降低閾值電壓的概念稱為DIBL。閾值電壓隨溝道長度的這種減小稱為V t滾降。在這種條件下流動的電流稱為亞閾值電流(斷態電流)。即使在飽和模式下,DIBL也會導致漏極電流隨著漏極偏置的增加而增加。

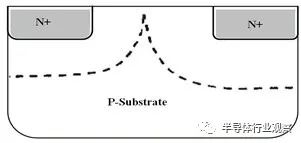

C.穿通(Punch-through:)

穿通是一種嚴重的屏障下降現象。當漏極偏壓增加時,圍繞漏極的耗盡區可以在兩個耗盡區合并的情況下進一步向源極延伸。這種情況稱為穿通。在這種情況下,隨著漏極電流的急劇上升,柵極電壓失去了對漏極電流的控制。穿通效應隨溝道長度的減小而增加。由于穿通,我們無法關閉設備,因此該設備變得無用,如圖4所示。

圖4.穿通–合并兩個耗盡區

D.熱載流子效應:

對于較小的幾何器件,電場特別是在漏極附近增加。結果,電子(載流子)獲得了大量的能量,稱為熱載流子。

它們中的一些獲得幾乎足夠的能量,從而導致在漏極附近發生碰撞電離,從而產生新的電子-空穴對。結果,它會引起漏極到身體的電流(I db)。少量熱電子可能會穿過氧化物隧穿并通過柵極收集自身。盡管某些熱載流子甚至會損壞氧化物,從而導致器件性能下降。

控制短溝道效果

我們在上一節中觀察到,如果溝道長度比耗盡區小,那么短溝道效應將變得無法忍受。這限制了柵極長度的進一步減小。為了限制這些影響,應減小耗盡區寬度并相應減小溝道長度。這可以通過增加溝道摻雜濃度或增加柵極電容,或兩者兼而有之來實現。柵極電容決定了柵極對溝道的控制。等式1表示可以通過縮放(減小)柵極氧化層厚度來增加柵極電容。已經觀察到具有更薄的柵極氧化物的器件具有減小的耗盡寬度,并因此改善了SCE特性。

COX = EOX / TOX (方程- 1)其中COX : 柵極氧化物電容,EOX : 氧化物的電場TOX :氧化物厚度

在過去的幾十年年中,對于英特爾的工藝節點,已經觀察到氧化物的比例大致與溝道長度成比例,以限制SCE。

傳統縮放的創新

A.移動助推器:應變硅技術

納米級晶體管中關鍵的縮放問題之一是由較大的垂直電場引起的遷移率降低。有很多方法可以增強晶體管的性能和遷移率。一種方法是在溝道中使用鍺薄膜,因為鍺具有較高的載流子遷移率。另一種方法是通過在溝道中引入機械應變來使用應變硅。

應變硅技術涉及使用各種方式對硅晶體進行物理拉伸或壓縮,從而增加載流子(電子/空穴)的遷移率并增強晶體管的性能。例如,當溝道受到壓縮應力時,可以增加PMOS的空穴遷移率。

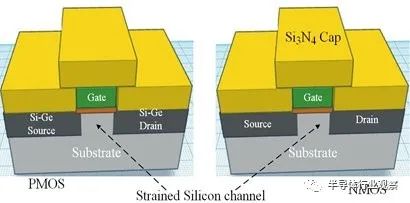

為了在硅溝道中產生壓縮應變,通過外延生長用Si-Ge膜填充源區和漏區。Si-Ge通常包含20%的鍺和80%的硅混合物。Si和Ge原子的數量等于原始Si原子。鍺原子大于硅原子。因此,當產生力時,它會推動溝道并提高孔的遷移率。增加半導體的遷移率可改善驅動電流和晶體管速度。

MOS晶體管的應變硅技術于2003年由Intel首次在其90nm工藝技術中使用。在該技術節點中,用于PMOS晶體管的Si-Ge源極漏極結構在溝道中產生壓縮應變,從而使電流提高了25%。通過在晶體管周圍添加高應力Si 3 N 4覆蓋層來引入NMOS應變,可將電流提高10%。

B.減少柵極漏電流:高介電常數

SiO2(氧化物)電介質的厚度應與其溝道長度成比例。65納米節點需要約2.3納米(實際為1.6納米)的有效氧化物厚度(EOT)。但是,如果將氧化物厚度進一步降低到此點以下,則載流子現象的直接隧穿將占主導地位。結果,柵極泄漏增加到不可接受的極限。因此,氧化物的厚度極限約為1.6nm,這是由柵至溝道隧穿泄漏(也稱為量子機械隧穿)設置的。

如果我們看方程式1,剩下的唯一選擇就是選擇具有高介電常數(K)的介電材料,以增加氧化物電容。由于可以使用更厚的介電層,因此我們可以獲得較高的柵極氧化物電容。該較厚的層導致較少的載流子隧穿。SiO2的介電常數為3.9。柵氧化物的突破是在2007年,基于Intel (HfO2)的High-K介電材料是Intel在其45nm大批量生產工藝中首次引入的。material材料的介電常數約為25,比SiO2高6倍。

圖5. a)PMOS:單軸拉伸應變b)NMOS:單軸拉伸應變

EOT由等式3給出。等式3表示6nm厚的HfO2提供約1nm的EOT。

EOT = ( 3.9 X TOX ) / K (方程 - 3)其中:EOT:有效氧化物厚度,TOX:氧化物厚度,K:材料的介電常數

C.消除多晶硅耗盡:金屬柵極

在多晶硅和柵極氧化物的界面處形成耗盡區。隨著器件尺寸的不斷縮小,這種多晶硅的損耗會變大,等效氧化物厚度的較大部分將限制柵極氧化物的電容。多晶硅耗盡的負面影響是由于反型層電荷密度的降低和器件性能的下降。因此,除了柵極氧化物的厚度之外,多晶硅耗盡層的厚度也需要最小化。

此外,由于諸如閾值電壓釘扎和光子散射之類的效應,多晶硅柵極也可能與高K電介質不兼容,這使得難以獲得低閾值電壓并降低溝道的遷移率。

消除多晶硅耗盡效應的一種解決方案是使用金屬柵極代替多晶硅柵極。金屬柵極不僅可以消除多晶硅耗盡效應,而且還可以使用高K電介質。

英特爾首次采用高K介電和金屬柵極技術推出了45納米節點。NMOS和PMOS使用不同的金屬,因為NMOS和PMOS需要不同的功函數。

晶體管工藝流程始于高K電介質和虛擬多晶硅的沉積。在高溫退火工藝之后,沉積并拋光層間電介質以暴露多晶硅。然后,去除偽多晶硅。最后,在柵極溝槽中沉積PMOS,然后沉積NMOS功函數金屬。

創新的結構

對于常規的MOS結構,隨著溝道長度的縮小,柵極不能完全控制溝道,這是不希望的。其影響之一是導致從漏極到源極的更多亞閾值泄漏,從功耗的角度來看,這是不好的。在傳統的MOS中,柵極不能控制泄漏路徑,該泄漏路徑與柵極之間的距離很遠。可以使用各種MOS結構來改善這一點,這些結構允許晶體管的縮放超出常規MOS縮放限制。在本節中,我們將討論兩個新的MOS結構,即SOI和FinFET。兩種結構的主要目的是使柵極至溝道電容最大,并使漏極至溝道電容最小。

A.絕緣體上硅(SOI):

常規MOS結構與SOI MOS結構之間的主要區別在于SOI器件具有掩埋氧化物層,該掩埋層使主體與襯底隔離。如圖7所示,SOI晶體管是一個planner設備。

除了起始硅晶片之外,SOI MOS的制造工藝與體MOS(常規MOS)工藝相似。SOI晶圓具有三層;1.硅薄表面層(形成晶體管的地方)。2.絕緣材料的底層。3.支撐或“處理”硅晶片。

SOI晶圓

掩埋氧化物層背后的基本思想是,它將減少寄生結電容。寄生電容越小,晶體管工作的速度就越快。提供更高的性能。由于BOX層,沒有多余的泄漏路徑遠離柵極。這導致較低的功耗。

根據操作過程中薄體的狀況,SOI器件可分為部分耗盡(PD)SOI和完全耗盡(FD)SOI。與PD SOI相比,FD SOI具有非常薄的自身結構,因此在運行過程中自身已完全耗盡。此FD SOI也稱為超薄型SOI。對于PD SOI,主體的厚度為50 nm至90 nm。而對于FD SOI,主體的厚度約為5納米至20納米。

圖7. SOI FET的結構

SOI設備的優勢:

由于氧化層隔離,漏極/源極的寄生電容降低了。因此,與批量CMOS相比,該器件的延遲和動態功耗更低。

由于具有氧化層,與體CMOS相比,閾值電壓對背柵偏置的依賴性較小。這使SOI器件更適合低功耗應用。

SOI器件的亞閾值特性更好,因此漏電流更小。

SOI設備沒有閂鎖問題。

SOI設備的缺點:

PD SOI設備的缺點之一是它們受歷史影響。在PD SOI中,隨著物體變厚,浮體變得明顯。因此,人體電壓取決于設備的先前狀態。該浮體電壓可以改變器件的閾值電壓。這可能會導致兩個相同晶體管之間的嚴重失配。

SOI器件的另一個問題是自熱。在SOI器件中,有源薄膜位于氧化硅上,氧化硅是很好的絕熱材料。在操作過程中,有源區消耗的功率無法輕易耗散。結果,薄體的溫度升高,這降低了器件的遷移率和電流。

FD SOI的挑戰之一是制造薄型SOI晶圓的困難。

B.FinFET:

臺積電前首席技術官和伯克利大學教授胡正明及其團隊在1999年提出了FinFET的概念,并在2000年提出了UTB-SOI(FD SOI)的概念。這兩種結構的主要原理是薄體,因此柵極電容更接近整個溝道。身體非常薄,大約10nm或更短。因此,沒有遠離柵極的泄漏路徑。澆口可以有效地控制泄漏。

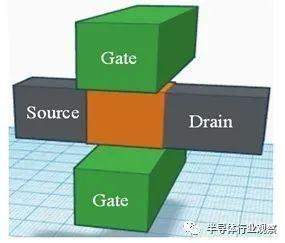

他們提出的FinFET的基本結構將是一個由多個溝道的一側控制的溝道。雙門結構之一如圖8所示。

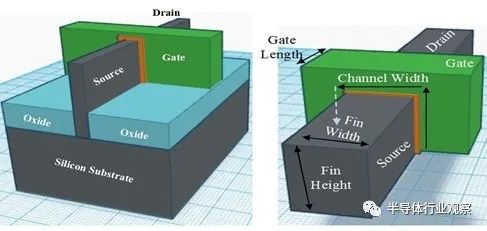

圖8.雙柵極結構

現代FinFET是3D結構,如圖9所示,也稱為三柵晶體管。FinFET可以在體硅或SOI晶圓上實現。這種FinFET結構由基板上硅體的薄(垂直)鰭片組成。閘門纏繞在溝道周圍,可從溝道的三個側面進行出色的控制。這種結構之所以稱為FinFET,是因為其Si體類似于魚的背鰭。

圖9. Fin-FET結構

在批量MOS(計劃MOS)中,溝道是水平的。在FinFET溝道中時,它是垂直的。因此,對于FinFET,溝道的高度(Fin)決定了器件的寬度。溝道的理想寬度由公式4給出。

Width of Channel = 2 X Fin Height + Fin Width (Equation-4)(來源:Synopsys)

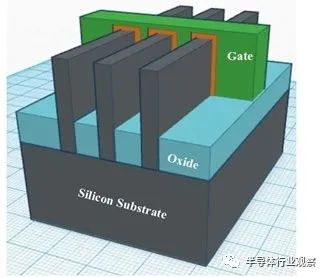

FinFET的驅動電流可以通過增加溝道的寬度(即通過增加Fin的高度)來增加。我們還可以通過構建如圖10所示的連接在一起的多個平行鰭來增加器件驅動電流。這意味著對于FinFET,任意溝道寬度都是不可能的,因為它總是鰭高度的倍數。因此,設備的有效寬度變得量化了。在planner設備中,可以通過更改溝道寬度自由選擇設備的驅動強度。

圖10.多鰭FinFET結構

在傳統的MOS中,將摻雜物插入到溝道中,以減少各種SCE并確保高Vth。在FinFET中,柵極結構包裹在溝道周圍,并且主體很薄,提供了更好的SCE,因此溝道摻雜成為可選的。這意味著FinFET受摻雜劑引起的變化的影響較小。低溝道摻雜還確保了溝道內部載流子的更好遷移性。因此,更高的性能。在這里注意到的一件事是FinFET和SOI技術都引入了“主體厚度”作為新的縮放參數。

FinFET技術提供了優于塊CMOS的眾多優勢,例如,給定晶體管占位面積的驅動電流更高,因此具有更高的速度,更低的泄漏,更低的功耗,無隨機的摻雜波動,從而使晶體管的遷移率和縮放度超過了28nm,而臺積電也更將這個晶體管技術應用到其5nm芯片上。

接下來是什么?

FinFET和SOI結構均具有更好的柵極控制和較低的閾值電壓,且泄漏較少。但是,當我們移到較低的技術節點(例如10nm節點以下)時,泄漏問題再次開始。這導致許多其他問題,例如閾值平坦化,功率密度增加和散熱。FinFET結構在散熱方面效率較低,因為熱量很容易積聚在鰭片上。與其他設計規則(例如可制造性設計)不同,這些擔憂可能會導致一類新的設計規則-散熱設計。

隨著這些設備接近其極限,行業正在努力合作以提供潛在的解決方案,包括修改設備結構,用新材料替換現有的硅材料。其中包括碳納米管(CNT)FET和GAA等都是當前的熱們選擇。

責任編輯:lq

-

半導體

+關注

關注

334文章

27026瀏覽量

216356 -

晶體管

+關注

關注

77文章

9635瀏覽量

137856 -

MOSFET器件

+關注

關注

0文章

18瀏覽量

9118

原文標題:晶體管發展歷程回顧

文章出處:【微信號:半導體科技評論,微信公眾號:半導體科技評論】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

NMOS晶體管和PMOS晶體管的區別

CMOS晶體管和MOSFET晶體管的區別

晶體管處于放大狀態的條件是什么

晶體管電流的關系有哪些類型 晶體管的類型

晶體管的分類與作用

如何提高晶體管的開關速度,讓晶體管快如閃電

什么是達林頓晶體管?達林頓晶體管的基本電路

晶體管Ⅴbe擴散現象是什么?

在特殊類型晶體管的時候如何分析?

如何根據管腳電位判斷晶體管

晶體管是如何工作的?BJT和MOSFET晶體管區別

進入全新一代的晶體管以前,回顧一下前幾代晶體管的發展

進入全新一代的晶體管以前,回顧一下前幾代晶體管的發展

評論