引言

隨著電子技術和通信技術的發展,對高速通信和超快速計算的需求日益增大。從早期的簡單語音傳輸發展到圖像傳輸和大量數據傳輸;調制方式上由單載波發展到多載波調制;天線技術方面由單天線發展到多天線傳輸;電子技術方面從單核處理器發展到多核處理器。這些技術都是為了提高信號傳輸的高速度和高靈敏度以滿足高速通信的需求。

目前迫切需要解決的是語音、視頻和數據三重播放的應用問題。三重播放的核心集中在連接性和計算能力上。連接性就是必須實現不同設備、板卡和系統之間數據的高速通信;計算能力指設備、板卡和系統中的處理器能夠滿足新的復雜的算法要求。本文介紹一種在數字信號處理器(DSP)C645x上實現串行 RapidIO總線數據傳輸的方法。該串行RapidIO傳輸可以達到芯片之間的10 Gbps的傳輸速度,滿足高速數據通信的需求。

1 串行RapidIO及其結構

RapidIO互連技術在2001年完成基本規范。2003年10月,國際標準組織和國際電工委員會(IEC)一致通過了RapidIO互連規范,即 ISO/IEC DIS 18372。目前在系統邏輯器件、FPGA和ASIC器件中已經實現了該技術。TI公司經過努力,也已經在DSP芯片上實現了該項技術。串行 RapidIO互連架構解決了高性能嵌入式系統(包括無線基礎設施器件、網絡接入設備、多服務平臺、高端路由器和存儲設備等)在可靠性和互連性方面的挑戰。Ra—pidIO互連為嵌入式系統設計提供了高帶寬和低延遲的數據通信。RapiclIO技術允許任何數據協議運行;同時通過提供自建的糾錯機制和點對點架構來排除單點故障,滿足嵌入式設計的可靠性需求。

基于DSP的串行RapidIO的主要特點有:

①引腳數少;

②數據寬度和速度可調;

③具備DMA和消息傳遞功能;

④支持復雜可調整的拓撲結構;

⑤支持多點傳送;

⑥可靠性高,可提供服務質量保證;

⑦功耗低。

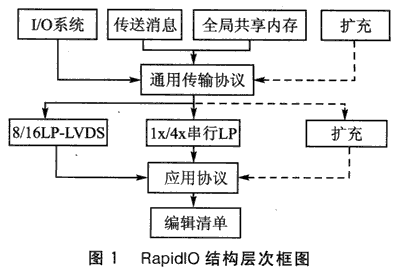

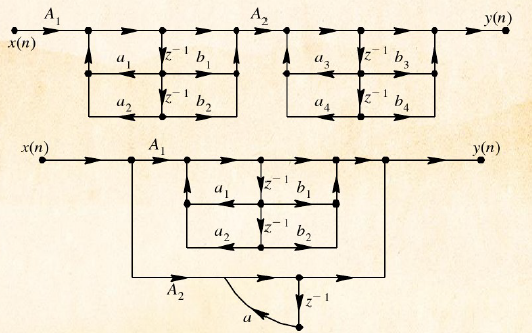

C645x的串行RapidIO有3層結構,如圖1所示。RapidIO結構主要包括物理層、傳輸層和邏輯層。其中物理層負責描述器件的接口規范,例如分組傳輸機制、流量控制、電特性以及低級錯誤管理等;傳輸層為在不同端點設備之間傳送分組提供路由信息,交換設備以基于器件的路由方式工作于傳輸層;邏輯層定義總體的協議和分組格式,每個分組最多包含256字節的載荷,事務通過Load、Store或DMA操作來訪問地址空間。圖1中,邏輯層包括I/0系統、傳送消息、全局共享內存以及為將來可能增加功能預留的擴充單元。傳輸層僅有一個實現通用傳輸協議單元;物理層現在包括8/16LP_LVDS和 1x/4x串行LP兩個單元,同樣預留可擴充單元。圖中的應用協議和編輯清單屬于應用層,由不同用戶改寫。

2 系統硬件結構

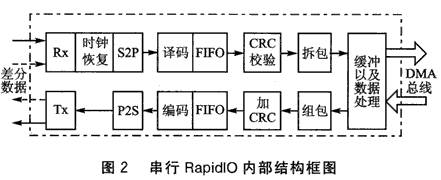

TMS320C645x系列DSP為TI公司推出的速度達到1.2 GHz的DSP,主要應用于電信、醫療電子和新興的電子行業;可以連接32位DDR2內存和66 MHz的PCI接口;具有2個串行干兆媒體獨立接口、以太網MAC端口、1個千兆以太網關,還有一個用于無縫連接公共電信數據流的電信串行接口。 TMS320C645x具有的這些特性非常適合于超高速數據處理系統中。在高速數據系統中,大量數據的芯片之間的傳輸十分關鍵。只有快速、及時地將數據傳輸出去或者讀取進來,才可以減輕系統對數據存儲的壓力。為此TMS320C645x專門增加了串行RapidIO模塊,使得在高速數據處理的同時,數據傳輸速度可以達到10 Gbps。圖2為TMS320C645x系列DSP的串行Ra—pidIO內部結構框圖。

從圖2可以看出,接收到的差分數據進入串行Ra—pidI0,首先RapidIO模塊根據數據的上升沿變化速度檢測出數據發送時鐘頻率,并以此頻率來接收后面的數據。然后,將接收的串行數據經過S2P(Series to Parallel)單元,將串行數據轉換成10位的并行數據,從而降低了10倍數據傳輸速度。物理層得到并行數據后,將數據送到邏輯層,依次經過譯碼、 FIFO、CRC校驗和拆包處理,送到緩沖并進行數據處理,最后經過DMA總線送到DSP處理單元,完成數據的接收。數據發送和接收過程相似,需要經過一個并串轉變P2S單元,發送無需時鐘處理單元,發送數據的速度包含了時鐘速度。

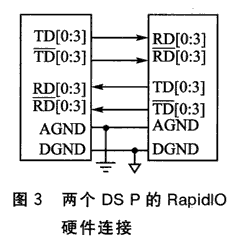

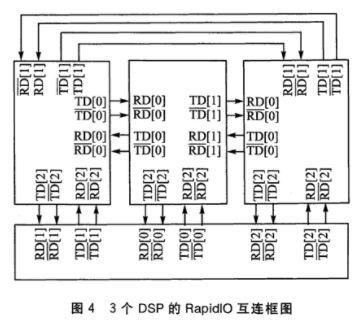

2個DSP之間的RapidIO連接簡單、方便,如圖3所示,只要將收發數據相應地連接上就可以了。由于RapidIO有4根并行數據總線,如果將所有的數據總線全部連接上,可以確保最高的通信速率。也可以使用1根數據總線通信,這時數據傳輸速度降低到最高通信速率的1/4。如果多個DSP相互之間都需要進行通信,則一般采用單根數據通信方式。圖4中的3個DSP之間相互使用RapidIO總線通信。由于只有4根數據總線,最多只能實現4個DSP之間相互使用RapidIO總線通信。需要注意的是,由于RapidIO通信速率較高,在數據總線的連接上,一定要注意屏蔽電磁干擾,盡量做到數據線等長。此外,DSP之間的數據地和模擬地需要分別連接在一起(見圖3)。

3 系統軟件設計

RapidIO總線的設置有3個步驟:

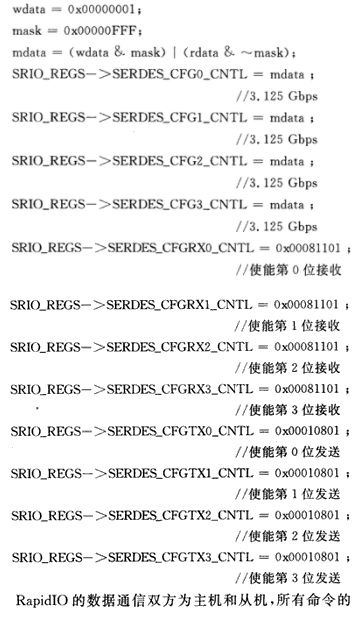

①設置RapidIO的時鐘,通過SERDES_CFG_CNTL寄存器設置數據收發的速率;

②使能RapidIO的接收器,同時設置一些和數據接收相關的參數,包括差分信號的自適應均衡設計、相位偏差設置、信號損耗設置等;

③使能RapidIO的發送器,同時設置一些和數據發送相關的參數,包括發送速率、總線寬度等。

設置RapidIO速率為3.125 Gbps,使能接收器和發送器的代碼如下:

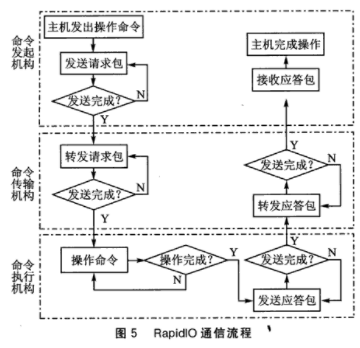

開始和結束都是由主機發起和控制的,從機被動地接收命令并執行指令。當從機需要主動向主機發送數據時,只能由從機發出中斷到主機;主機響應中斷后,發出數據讀取命令。具體的工作流程如圖5所示。主機的命令發起機構發出操作命令,并將發送請求包經過命令傳輸機構傳送到從機的命令執行機構,從機的命令執行機構可能執行數據接收(主機向從機發送數據)和數據發送(主機要求從機發送數據)任務。命令執行機構處理完成相應命令,發送應答包到主機,主機判斷到命令完成,將命令狀態清除,完成整個命令的操作。

RapidIO在數據傳輸過程中,可能產生錯誤。根據錯誤情況,RapidIO發出2種不同的中斷到CPU:狀態錯誤,此時CPU應復位或者重新同步 RapidIO;嚴重錯誤,此時CPU應復位所有和RapidIO相關的設備。CPU進行相應處理后,RapidIO就可以正常通信了。

4 總結

本文介紹了DSP中的串行RapidIO總線,詳述了該總線的層次結構和內部結構,并且結合多個DSP之間的RapidIO通信介紹了硬件和軟件系統設計。該總線可以實現 10 Gbps的高速數據通信,可以滿足語音、圖像和數據等多種通信業務的需求。整個通信系統連接簡單、通信可靠、實用性強。

責任編輯:gt

-

嵌入式

+關注

關注

5072文章

19026瀏覽量

303523 -

通信系統

+關注

關注

6文章

1176瀏覽量

53290

發布評論請先 登錄

相關推薦

數字信號處理器(DSP)簡介

支持過程級動態軟硬件劃分的RSoC設計與實現

利用FPGA怎么實現數字信號處理?

數字信號處理器的特點

基于軟硬件協同設計的低功耗生理信號處理ASIC設計

數字信號處理器(DSP)

Builder數字信號處理器的FPGA設計

PCI局部總線的性能特點及實現通用信號處理系統的軟硬件設計

基于數字信號處理器實現RapidIO通信系統的軟硬件設計

基于數字信號處理器實現RapidIO通信系統的軟硬件設計

評論