近年來,人工智能的發(fā)展重心逐漸從云端向終端轉(zhuǎn)移,相伴而生的,是人工智能芯片產(chǎn)業(yè)的全面發(fā)展。但,如何在大大小小的市場玩家中,避免千人一面的同質(zhì)化競爭,揚長避短,在激烈的市場競爭中分得一杯羹,是所有AI公司都要面對的問題和挑戰(zhàn)。

時擎智能科技(上海)有限公司致力于通過架構(gòu)創(chuàng)新和定制化芯片設(shè)計,為廣泛的端側(cè)設(shè)備提供支持語音、視覺、影像、顯示等多模態(tài)智能人機交互和數(shù)據(jù)處理的芯片產(chǎn)品,以及完整的系統(tǒng)級解決方案。

時擎科技總裁 于欣

公司總裁于欣在接受電子發(fā)燒友網(wǎng)專訪時表示,時擎科技核心團隊來自前Marvell的ARM處理器團隊和芯原微電子的SoC團隊,在各種不同類型的處理器(主控/DSP/NPU/DSA)微架構(gòu)、邏輯設(shè)計、軟件工具鏈等方面均具有領(lǐng)先的能力;在SoC方面,時擎科技核心團隊曾主導(dǎo)過各種類型的音視頻SoC,對各類端側(cè)影音芯片的設(shè)計和量產(chǎn)具有豐富的工程經(jīng)驗;公司研發(fā)能力完整地覆蓋了核心IP,芯片設(shè)計、驗證、實現(xiàn),生產(chǎn)運營,系統(tǒng)軟件和圖像語音算法等芯片研發(fā)的各個流程和環(huán)節(jié),可以為客戶端側(cè)場景的需求提供完整的解決方案。

如何應(yīng)對:端側(cè)設(shè)備對成本/功耗的敏感性

在應(yīng)用繁多的AIoT時代,產(chǎn)品自主創(chuàng)新朝著何種方向,更需要根據(jù)不同的場景進行分析。但從總的趨勢來看,端側(cè)設(shè)備智能化是顯而易見的。

在競爭力方面,對成本和功耗比較敏感的端側(cè)設(shè)備而言,算力效率即單位算力的成本和功耗極為重要,同時,不容忽視的,還有算力落地的可實現(xiàn)性,也就是如何將算力高效的發(fā)揮出來,切實的為用戶帶來更好的產(chǎn)品體驗。此外,在端側(cè)場景下,如何打造定制化的處理器方案,與各類語音、圖像、聲學(xué)前處理、識別分類等深度學(xué)習(xí)算法更好的配合,在滿足應(yīng)用需求的前提下,做到更好的算力效率,也是提升能效比、性價比培養(yǎng)競爭力的著力點。

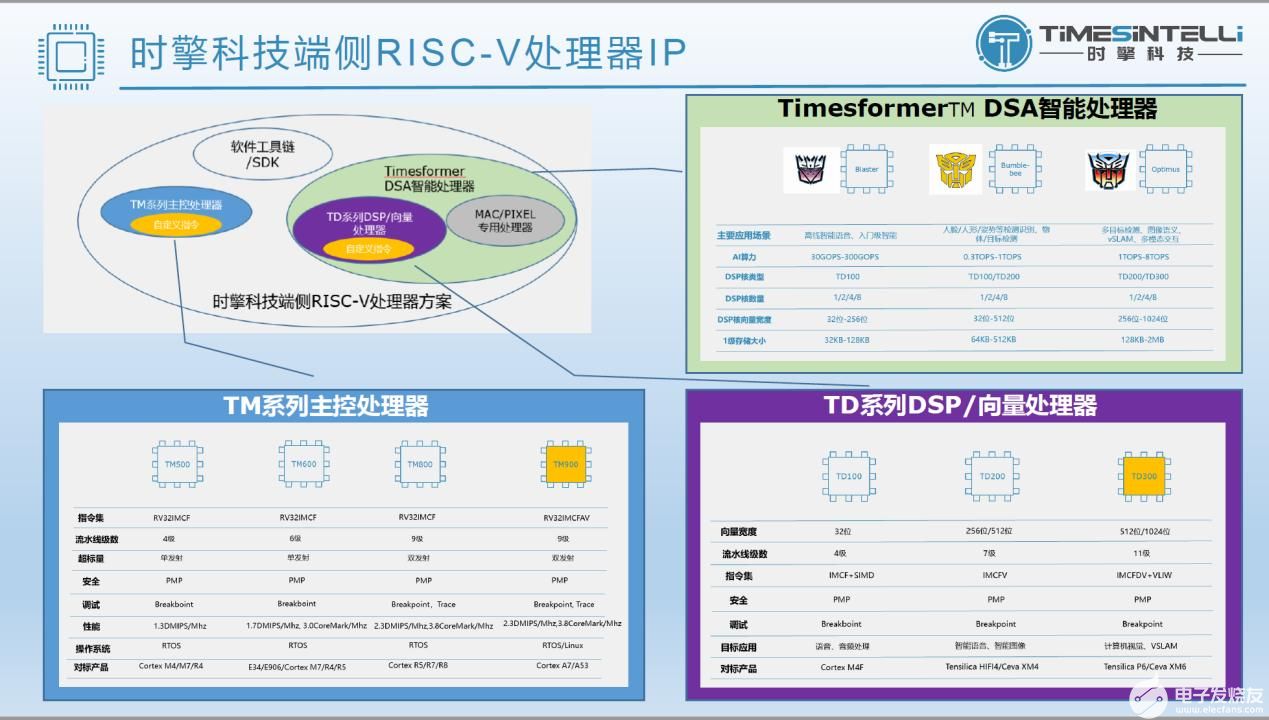

對此,于欣表示,時擎科技堅持采用自研處理器作為端側(cè)芯片產(chǎn)品的核心、并從落地場景的算法需求出發(fā),從最核心的處理器IP開始設(shè)計,力求在芯片的架構(gòu)層面與目標場景的應(yīng)用需求達到更好的契合,力爭為產(chǎn)品打上“高性價比“、“高能效比”和”強應(yīng)用適用性”的標簽。此外,通過基于RISC-V架構(gòu)的、一站式、統(tǒng)一的開發(fā)環(huán)境,與目前主流的CPU/DSP/NPU三套開發(fā)環(huán)境各自為政的方案相比,可以使得開發(fā)者不需要關(guān)注異構(gòu)多核之間的通信交互和任務(wù)調(diào)度,從而大大簡化了對異構(gòu)芯片開發(fā)和調(diào)試的挑戰(zhàn)。

對于端側(cè)智能處理算法的趨勢,于欣認為,未來網(wǎng)絡(luò)模型為了更方便地在端側(cè)設(shè)備部署,將會呈現(xiàn)小型化、輕量化的特征;迭代更新速度將會很快,而與之對應(yīng)的芯片則因研發(fā)周期長而存在“滯后效應(yīng)”;傳統(tǒng)DSP算法與NN算法針對不同的應(yīng)用會長期共存互補。結(jié)合對算法趨勢的預(yù)測,時擎科技推出了Timesformer智能計算架構(gòu),并以此作為產(chǎn)品在端側(cè)實現(xiàn)高效計算的核心引擎。

借力RISC-V,提供turn-key方案

相較于絕對的算力等指標數(shù)字,從實際應(yīng)用或算法的角度來評判芯片的性能,看似在芯片規(guī)格之外,實則又是直接決定芯片競爭力的關(guān)鍵。

目前,時擎科技面向不同應(yīng)用場景、不同算力需求的端側(cè)智能應(yīng)用,研發(fā)了三個不同系列的芯片--AT800、AT1000和AT5000。據(jù)于欣介紹,公司端側(cè)芯片競爭力主要表現(xiàn)在三個方面,一是更高的AI算力效率,可以做到與端側(cè)算法的緊密配合;二是能夠為用戶帶來更好的編程體驗,讓AI算法更容易地高效部署落地;三是可以提供定制化的圖像處理器(ISP)和豐富靈活的多媒體接口組合。

時擎科技端側(cè)RISC-V處理器IP

據(jù)電子發(fā)燒友網(wǎng)了解,目前出貨的主要是AT1000系列,并且從去年Q3成功量產(chǎn)以來,累計出貨量已接近百萬片;AT800和AT5000系列也將會在今年下半年開始量產(chǎn)出貨。

時擎科技AT系列端側(cè)智能芯片

據(jù)于欣介紹,一家合作伙伴的雙麥降噪+離線識別的算法,原本運行在雙核Cortex-A7,64MB DDR2的應(yīng)用處理器上,去年開始與時擎科技密切合作,進行算法的深度優(yōu)化和移植,最后,成功將對方的算法部署在AT1611上(Timesformer Blaster-100 + 8 MB PSRAM),實際效果幾乎完全一致。

于欣表示,時擎科技會根據(jù)對端側(cè)市場需求的理解,按照RISC-V處理器的研發(fā)規(guī)劃,持續(xù)投入研發(fā),下一步的重點,則是結(jié)合應(yīng)用需求和市場反饋,在目前的產(chǎn)品系列基礎(chǔ)上做更新迭代。相較于廣義的生態(tài)支持,時擎科技針對目標應(yīng)用提供turn-key的方案,作為新興的ISA發(fā)展模式,通過前期觸達的應(yīng)用先落地生根,同步建設(shè)健全生態(tài),進而在某個或某些領(lǐng)域向通用化發(fā)展,就有機會形成如今天ARM在手機中這樣的“事實上的標準”。

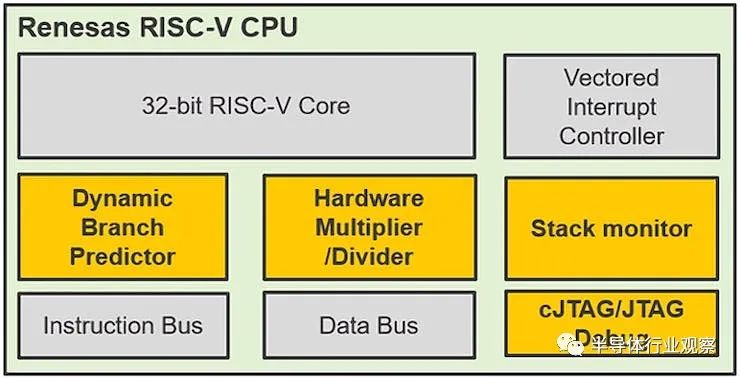

對于產(chǎn)品的架構(gòu)問題,于欣認為,架構(gòu)只是工具,談不上路線,只有適合與不適合,沒有對與錯,針對主控處理器、DSP處理器、NPU、DSA等不同種類的處理器,公司已經(jīng)積累了包括微架構(gòu)、邏輯設(shè)計、物理設(shè)計、配套軟件工具鏈等在內(nèi)的全棧定制能力。如前文所述,時擎科技團隊本身是做ARM處理器出身,對ARM的架構(gòu)、處理器IP和SOC等具備深厚的經(jīng)驗基礎(chǔ),因此,除了大力研發(fā)RISC-V芯片,未來也會有基于ARM架構(gòu)的芯片產(chǎn)品面世,據(jù)悉正在積極籌備規(guī)劃中。

是挑戰(zhàn) 更是機遇

端側(cè)智能芯片在保障利用AI算法處理巨量數(shù)據(jù)所需的算力的同時,具有高度的靈活性,并能夠針對具體用場景做出更好的優(yōu)化,同時削減了傳輸時延,也大幅降低了通信需求在應(yīng)用端承擔(dān)的沉重壓力,此外在隱私保護和數(shù)據(jù)安全方面也具有難以替代的優(yōu)勢,正是由于諸多優(yōu)點吸引了大量企業(yè)聚焦于此。

在日新月異、快速發(fā)展的AI業(yè)界,初創(chuàng)企業(yè)面臨著不小的挑戰(zhàn)。市場和銷售渠道都要從零到一進行搭建,產(chǎn)品也需要一個循序漸進的打磨過程,另外,仍有待提高的市場成熟度,也是需要面對的挑戰(zhàn);但另一方面,是挑戰(zhàn)更是機遇,正是因為屬于初創(chuàng)企業(yè),沒有積累,也意味著沒有包袱,市場尚未成熟,群雄逐鹿,但意味著尚未形成寡頭格局。對于端側(cè)智能芯片的機遇與挑戰(zhàn),于欣認為,從時擎科技的角度,一方面,已經(jīng)形成了一定規(guī)模、具備相當經(jīng)驗的業(yè)務(wù)團隊,更重要的是,作為一家產(chǎn)品涵蓋從處理器IP到芯片再到應(yīng)用全鏈條的公司,還應(yīng)堅持從應(yīng)用和落地出發(fā)去打磨產(chǎn)品,既要敏銳的洞察市場風(fēng)向,也要堅持自身的既定路線,在芯片本身的競爭力基礎(chǔ)上,扎扎實實做好每一個細分領(lǐng)域的應(yīng)用落地,相信隨著市場的成熟和爆發(fā)之后,會有所期待的收獲。

對于公司的未來規(guī)劃,于欣表示,公司成立三年來,每年營收增幅都超過100%,2020年公司營收超過2000萬,預(yù)計2021年可以達到8000萬,未來三年內(nèi),在產(chǎn)品方面,時擎科技將把產(chǎn)品定義、研發(fā)、銷售的閉環(huán)在現(xiàn)有的三個系列的產(chǎn)品上完全驗證走通,并進行產(chǎn)品的升級和迭代;在團隊建設(shè)方面,繼續(xù)補強短板,加強研發(fā)投入,在扎實的芯片設(shè)計能力之上,也將加強算法和應(yīng)用軟件的團隊規(guī)模和力量,力爭早日在國內(nèi)端側(cè)芯片的廠家里占有屬于自己的一席之地。

電子發(fā)燒友開放平臺【RISC-V專題】,歡迎本土創(chuàng)新產(chǎn)品及方案商,一起探討RISC-V帶來的機遇及商業(yè)化落地~

專題合作/入群交流/更多資訊,掃碼添加好友

-

DSA

+關(guān)注

關(guān)注

0文章

48瀏覽量

15124 -

終端側(cè)技術(shù)

+關(guān)注

關(guān)注

0文章

3瀏覽量

8107 -

RISC-V

+關(guān)注

關(guān)注

44文章

2233瀏覽量

46045 -

AI算力

+關(guān)注

關(guān)注

0文章

73瀏覽量

8573 -

算力

+關(guān)注

關(guān)注

1文章

936瀏覽量

14750

發(fā)布評論請先 登錄

相關(guān)推薦

RISC-V,即將進入應(yīng)用的爆發(fā)期

多核RISC-V處理器供應(yīng)商超睿科技全力支持RT-Thread Smart,共同賦能“大芯片”生態(tài)

risc-v在人工智能圖像處理應(yīng)用前景分析

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

開源芯片系列講座第22期:異步電路機制為RISC-V處理器賦能

RISC-V適合什么樣的應(yīng)用場景

RISC-V在中國的發(fā)展機遇有哪些場景?

直播預(yù)告 |開源芯片系列講座第22期:異步電路機制為RISC-V處理器賦能

算能全系列RISC-V處理器進入PLCT實驗室6.6內(nèi)核維護工程

為何什么risc-v芯片比arm的效率高

risc-v多核芯片在AI方面的應(yīng)用

IC咖啡沙龍“芯未來”公益講座丨仇健樂:RISC-V指令架構(gòu)賦能端側(cè)智能芯片產(chǎn)業(yè)化落地

國產(chǎn)RISC-V MCU推薦

瑞薩推出首款基于RISC-V指令集架構(gòu)的處理器內(nèi)核

RISC-V架構(gòu)DSA處理器賦能端側(cè)應(yīng)用 破解智能處理芯片算力效率難題

RISC-V架構(gòu)DSA處理器賦能端側(cè)應(yīng)用 破解智能處理芯片算力效率難題

評論